Вычислительное устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и специализированных вычислительных устройствах. Целью изобретения является повышение быстродействия устройства при перемножении трех и более сомножителей с одновременным сокращением аппаратных затрат. Поставленная цель-достигается тем, что в вычислительном устройстве, содержащем блок 2 вычисления логарифма и экспоненты , выполненный в виде блока памяти, сумматор 9 и преобразователь 3 прямого кода в дополнительный, управляющий вход которого соединен с входом показателя степени операнда устройства, дополнительно введены блок 6 управления и мультиплексор 1, сумматор выполнен накапливающим. 3 ил., 2 табл.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)з 6 06 F 7/38 роыиацю фсм

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

К АВТОРСКОМУ С ВИДЕТЕЛ БСТВУ

1 (21) 4849175/24 (22) 09,07.90 (46) 23.06.92. Бюл;. ¹ 23 (71) Киевский политехнический институт им.

50-летия Великой. Октябрьской социалисти . ческой революции (72) Наджар Яхья ($У), В.П.Тарасенко и

Е.M.Øвец (SU) (53) 681.325 (088.8) (56) Авторское свидетельство СССР. № 1305666, кл. G 06 F 7/52, 1987.

Авторское свидетельство СССР № 1080135, кл. G 06 F 7/38, 1984. (54) ВЫЧИСЛИТЕЛ6НОЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной .технике и может быть использовано в цифро„„5U„„1742814 А1 вых вычислительных машинах и специализированных вычислительных устройствах.

Целью изобретения является повышение быстродействия устройства при перемножении трех и более сомножителей с одновременным сокращением аппаратных затрат. Поставленная цель достигается тем, что в вычислительном устройстве, содержащем блок 2 вычисления логарифма и экспоненты, выполненный в виде блока памяти, сумматор 9 и преобразователь 3 прямого кода в дополнительный, управляющий вход которого соединен с входом показателя степени операнда устройства, дополнительно введены блок 6 управления и мультиплексор

1, сумматор выполнен накапливающим. 3 ил., 2 табл.

1742814

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и специализированных вычислительных устройствах.

Известно устройство для деления и умножения, содержащее логарифмирующие функциональные преобразователи, алгебраический сумматор, блок сдвига и потенциирующий функциональный преобразователь, осуществляющий потенциирование младших разрядов мантиссы.

Недостатком этого устройства является большой объем памяти, который приводит к усложнению его реализации. Ограниченные функциональные воэможности устройства заключаются в том, что оно позволяет реализовать операции умножения и деления только над двумя операндами и не пригодно для вычисления сложных функциональных зависимостей, Известно устройство для умножения, содержащее первые два блока памяти, выполняющие операции логарифмирования первого и второго сомножителей, сумматор по модулю два, комбинационный сумматор и третий блок памяти, преобразующий сум му логарифмов сомножителей в их произведение;

Недостаток данного устройства — ограниченные возможности, так как здесь возможно лишь вычисление произведения двух чисел, представленных в дополнительном двоичном коде.

Наиболее близким к предлагаемому является вычислительное устройство, содержащее первый и второй блоки памяти, к адресным входам которых подключены соответственно выходы первого и второго регистров операндов, а информационные входы связаны соответственно с информационными входами первого и второго сдвигателей, выход первого сдвигателя подключен к первому входу сумматора, к второму входу которого через группу элементов И подключен выход преобразователя прямого кода в.дополнительный, вход которого соединен с выходом второго сдвигателя, выход сумматора подключен к адресному входу третьего блока памяти, информационный выход которого подключен к входу регистра результата. Кроме того, устройство содержит вход управления возведением в степень, вход задания режима умножения или деления и входы показателя степени первого и второго операндов.

Вычисления в известном устройстве производятся на основе соотношения

2Х Й . (1) Иначе можно записать

2=2(Ь х gôg n eoq ) (2) где (< =+ 1; @=0,1, что эквивалентно выражению(1) при ф = ф», Откуда следует, что при ((= 1) производится умножение, а при (ф= — 1) — деление

Х íà Y . В частности, при k = 1 = 0 проиэ2 1 водится соответственно умножение (ф = 1) и деление((=-1) Х íà Y. При ф=0 и k > 0 производится возведение X в степень 2 а при k < 0 извлечение их Х корня степени 2(.

Таким образом, известное устройство выполняет операции умножения, деления, возведения в степень и извлечения корня.

Недостатком известного устройства является низкое быстродействие и большие затраты оборудования при реализации на нем вычислений вида

М! МФ Мл

Y = X1 X2 ... Х,, где а» (— 1, 1}; 1 = 1,п.

».

Целью изобретения является повышение быстродействия устройства при перемножении трех и более сомножителей при вычислении выражений вида 2 ОСп

Y =X) X2 „. Xn, где QE(— 1,1); I =1,п.

Поставленная цель достигается тем, что в вычислительном устройстве, содержащем блок вычисления логарифма и экспоненты, выполненный в виде блока памяти, сумматор и преобразователь прямого кода в дополнительный, управляющий вход которого соединен с входом показателя степени операнда устройства, дополнительно введены блок управления и мультиплексор, сумматор выполнен накапливающим, при этом первый информационный вход мультиплексора соединен с входом операнда устройства, входы пуска и синхронизации которого соединены соответственно с входами сброса и синхронизации блока управления и сумматора, выход которого соединен с вторым информационным входом мультиплексора, выход которого соединен с информационным входом блока вычисления логарифма и экспоненты, управляющий вход которого соединей с управляющим входом мультиплексора и выходом блока управления, выход блока вычисления логарифма и экспоненты соединен с выходом результата устройства и информационным входом преобразователя прямого кода в дополнительный, выход которого соединен с информационным входом сумматора.

20

30

40

50

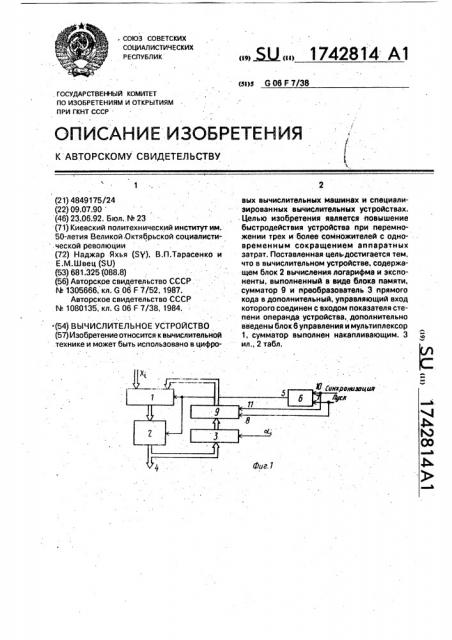

На фиг.1 изображена структурная схема вычислительного устройства; на фиг.2 — схема построения блока управления; на фиг.3 — временные диаграммы, поясняющие работу блока управления и устройства.

Вычислительное устройство содержит мультиплексор 1, первый информационный вход которого соединен с входом операнда устройства. а выход — с информационным входом блока 2 вычисления логарифма и экспоненты. Выход этого блока соединен с информационным входом преобразователя

3 прямого кода в дополнительный и выходом 4 результата. Управляющие входы мультиплексора 1 и блока вычисления логарифма и экспоненты 2 соединены с выходом

5 блока 6 управления, первый управляющий вход 7 которого объединен с входом пуска устройства и с первым управляющим входом 8 сумматора 9, а второй управляющий вход 10 — с входом синхронизации устройства и вторым управляющим входом 11 сумматора

9. Этот сумматор выполнен накапливающим и его информационный вход соединен с выходом преобразователя 3 прямого кода в дополнительный, а выход — с вторым информационным входом мультиплексора

1. Управляющий вход преобразователя 3 прямого кода в дополнительный соединен с входом показателя степени операнда, При конкретной реализации устройства:мультиплексор 1 может быть реализован, например, с использованием микросхемы

531 КП11, Блок 6 управления (фиг.2) содержит счетчик 11, RS-триггер 12 и элемент И 13.

Вход 10 подключен к входу синхронизации устройства и является входом синхронизации блока 6 управления. С. этим входом соединены тактирующие входы счетчика 11 и триггера 12. Вход 7 подключен к входу пуска устройства и является входом сброса блока 6 управления. С этим входом соединены входы сброса счетчика 11 и триггера 12, выход 5 которого является выходом блока 6 управления. Выходы счетчика 11 подключены к входам элемента И 13, выход которого соединен с единичным входом триггера 12.

При конкретной реализации блока 6 управления, счетчик 11 может быть реализован с использованием, например, микросхемы К155ИЕ5. Триггер 12 может быть выполнен на элементах И вЂ” НЕ (микросхемах

К155ЛАЗ). В качестве элемента И может быть использована микросхема К155ЛИ4.

Устройство предназначено для вычисления выражений вида

lKi с(д

У=Х1 Хт ...Х ", где а t(-1,1): I - 1,п, Выражение можно представить как

y С 1 и С м,Е,Х,+„,Ь,Х,, ... +g„eo>, Х„

При таком представлении Y его вычисление сводится к сложению или вычитанию (в зависимости от значения сц) логарифмов

loge XI и дальнейшему потенциированию полученной суммы Sn.ïî основанию С. Блок вычисления логарифма и экспоненты 2, выполненный в виде блока памяти, используется для воспроизведения логарифмов log< Х и потенциирования S . Преобразователь 3 прямого кода в дополнительный в зависимости от значения а либо преобразует код, поступающий с выхода блока 2 вычисления логарифма и экспоненты в дополнительный при а = -1 (с приходом сигнала логической

"1" на управляющий вход преобразователя

3 прямого кода в дополнительный), либо передает код с выхода блока 2 вычисления логарифма и экспоненты на вход сумматора

9 без изменений при и - 1 (с приходом сигнала логического "0" на управляющий вход преобразователя 3 прямого кода в дополнительный).

Устройство работает следующим образом, Перед началом работы по сигналу "О" на входе пуска устройства сумматор сбрасывается в "0", т.е. So = О. C приходом сигнала "1" на вход пуска устройства на выходе 5 блока

6 управления появится "О" и будет разрешено прохождение операндов с первого информационного входа мультиплексора 1.

Синхронно с тактовыми импульсами, поступающими на вход синхронизации устройства, подаются первый операнд Х1 на первый информационный вход мультиплексора 1 и значение его показателя степени а} íà управляющий вход преобразователя 3 прямого кода в дополнительный. Далее в блоке 2 вычисления. логарифма и экспоненты производится логарифмирование, код числа Y< = loge Х1 поступает на информационный вход преобразователя прямого кода в дополнительный 3, который в зависимости от значения а (от управляющего сигнала "О" или "1"), либо передает код с информационного выхода блока 2 вычисления логарифма и экспоненты на информационный вход сумматора 9 без изменения, либо преобразует указанный код в допол ни.тельный, т.е. 21= Y> loge X1, В свою очередь, на выходе сумматора 9 имеется значение результата суммирования очередного значения 2> + log Х1 к текущей сумме

So, т.е. $1 So + log X> = log Х1. Этот код

1742814

1G

Y =X < Х Хз -Х4 появится на выходе сумматора 9 и на втором информационном входе мультиплексора 1.

Не втором шаге с приходом следующего тактового импульса (фиг.3) принимаются второй опеоанд Х2 и значение его показателя степени 4 Далее работа блока 2 вычисления лОгарифма и экспоненты и преОбразователя

3 прямого кода в дополнительный повторяется, на выходе сумматора 9 имеем код

52 - 31 + 22 - +. loge Х1 + 1ОЯе Х2, Таким образом, за и шагов на выходе сумматора 9 получают

Я, = и loge X> и loge Х2 + ... + loge Xn

Этот код подается на второй информационный вход мультиплексора 1, а в блоке 2 вычисления логарифма и экспоненты производится потенциирование, т.е. Y = exp Sn, так как на управляющие входы мультиплексора 1 и блока 2 вычисления логарифма и экспоненты подается сигнал "1" (фиг.3).

Блок 6 управления работает следующим образом.

С приходом положительного импульса

"Пуск" с входа 7 блока 6 управления счетчик

11 и триггер 12 будут сброшены в состоянии G". Синхронно с тактовыми импульсами за и шагов (например, и = 8, где и — количество операндов) триггер 12 переключается в "1".

Временные диаграммы, поясняющие работу блока 6 управления и устройства представлены на фиг.3, Пример, поясняющий работу устройства при вычислении (X< =4, Хг=6, Хз=3, Х4=2) приведен в табл.1.

Выбор числа разрядов m при указанных выше вычислениях может быть выполнен с помощью табл.2.

Определяют время вычислений на предлагаемом устройстве. На выходе мультиплексора 1 после времени tMS появится код операнда, поступающего с первого или второго его информационного входа в зависимости от сигнала "0" или "1" íà его управляющем входе. В блоке 2 вычисления логарифма и экспоненты через время tnav воспроизводится логарифмирование или потенциирование. Через время tnt преобразователь 3 прямого кода в дополнительный в зависимости от значения а либо передает код с выхода блока 2 вычисления логарифма и экспоненты на информационный вход сумматора 9 без изменений; либо преобразует код s дополнительный. Через время fcM на выходе сумматора 9 имеют результат суммирования очередного значения Zi = й!ОЯ, XI к текущей сумме Si-l.

Таким образом, общее время выполнения указанных действий на каждом шаге составляет г1 = tMs+ tnzv+ tnt+ тсм. После шагов на выходе устройства 4 получают т = ехр Sn, поэтому суммарное время формирования результата составляет

<= и t1+ tMS+ тПЗУ.

В известном устройстве время каждого шага вычислений для пары операндов

15 t2 = 2 тпзУ + тсЯ + тпк + тсм, где tq — время сдвига чисел на сдвигателе. Кроме того, при вычислении выражений т = X> .Xz ... X n" известным устройством после умножения каждой пары операндов необходимо выпол-.

20 нять пересылку результата в один из регистров операндов. Поэтому общее время вычисления в известном устройстве составляет Т = (n — 1) (tn+ t2), гдето — время пересылки. Таким образом, сокращение времени

25 вычислений составит

At = (n 1) (ПЗУ+ tn+ tcg) tnt — тСМ вЂ” (и+1) tMS.

Поскольку во многих практических случаях ь

tnav =1 =1сц =tnt< =1см =GAMS= t то At =2t(n-3) и эффект сокращения време35 ни вычислений проявляется всегда, если. только п >3.

В известном устройстве используются три блока постоянной памяти, имеющие входное слово длиной соответственно m, m, 40 m+1 разрядов. Поэтому емкость всей памяти в прототипе составляет 2 + 2 + 2 " слов.

В предлагаемом же устройстве используется один блок постоянной памяти для

45 воспроизведения логарифмирования и потенциирования, длина входного слова для которого не превышает m+1. Поэтому емкость всей памяти в предлагаемом устройстве составляет 2 слов, а выигрыш от

m+t

50 применения этого устройства, выраженный через экономию памяти, составляет 2 2 слов.

Формула изобретения

Вычислительное устройство, содержа55 щее блок вычисления логарифма и экспоненты, выполненный в виде блока памяти, сумматор и преобразователь прямого кода в дополнительный, управляющий вход которого соединен с входом показателя степени

1742814

Таблица 1

Таблица.2 операнда устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства при перемножении трех и более сомножителей, устройство дополнительно содержит блок управления и мультиплексор, сумматор выполнен накапливающим, при этом первый информационный вход мультиплексора соединен с входом операнда устройства, входы пуска и синхронизации которого соединены соответственно с входами сброса и синхронизации блока управления и сумматора. выход которого соединен с вторым информационным входом мультиплексора,- выход которого соединен с информационным входом блока вычисления логарифма и экспоненты, уп5 равляющий вход которого соединен с управляющим входом мультиплексора и выходом блока управления, выход блоке вычисления логарифма и экспоненты соединен с выходом результата устройства и информацион10 ным входом преобразователя прямого кода в дополнительный, выход которого соединен с информационным входом сумматора.

1742814 вы.а i и

8ЙЮЭ Ююкрф 4к

8го ьг &о«а

Birxo3 Хи«а д4/ У ям,«у дьюоР Рококо

Составитель Н,Яхья

Техред М.Моргентал

Корректор Л.Бескид

Редактор А.Мотыль

Производствен 10 "издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 2286 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35; Раушская наб., 4/5