Устройство для сжатия и обработки информации

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной и измерительной техники и может быть использовано в различных автоматизированных системах сбора и обработки информации, а также диагностического контроля. Цель изобретения - повышение информативности и достоверности устройства Устройство содержит аналого-цифровой преобразователь 1, дифференцирующий элемент 2, первый 3 второй М блоки сравнения, генератор 5 импульсов , делитель 6, формирователь 7 кодов, счетчик 8, первый блок 9 буфепном памяти, блоки обработки, содержащие первый 10, второй 11, третий 12, четвертый 13 элементы И, триггер И, первый 15, второй 16 элементы сравнения, элемент ИЛИ 17. Устройство также содержит элемент ИЛИ 18, элемент И-НЕ 19, элемент И 20, второй блок 21 буферной памяти. 6 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ . РЕСПУБЛИК

Щ)5 GOBC 1/28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4794984/24 (22) 22.02.90 (46) 23.06.92. Бюл. NÐ 23 (72) А.С.Бурый и В.П:,Орлов (53) 625.381(088.8) ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ПИНТ СССР (56).Авторское свидетельство СССP

И 1381572, кл. С 08 С 19/28, 1988.

Авторское свидетельство СССР

М 1365107, кл. G 08 С la/28, 1988.

Титце У., Шенк К, Полупроводниковая схемотехника - И.: Мир, 1982. (54) УСТРОЙСТВО ДЛЯ СЖАТИЯ И .ОБРА"

БОТКИ ИНФОРИАЦИИ (57) ИзоЬретение относится к области вычислительной и измерительной техники и может Ьыть использовано в различных автоматизированных системах

«сЫ 1742842 А1

2 сЬора и оЬработки информации, а также диагностического контроля. Цель изоЬретения — повышение информативности и достоверности устройства.

Устройство содержит аналого-цифровой преобразователь 1, дифференцирующий элемент 2, первый 3, второй

4 блоки еравнения, генератор 5 импульсов, делитель 6, формирователь

7 кодов, счетчик 8, первый блок 9 буфепной памяти, блокиобработки, содержацие первый 10, второй 11, третий

12, четвертый 13 элементы И, триггер

14, первый 15, второй 16 элементы сравнения, элемент ИЛИ 17. Устройство также содержит элемент ИЛИ 18, weмент И-НЕ 19, элемент И 20, второй блок 21 буферной памяти. 6 ил.

1742842

Изобретение относится к вычислительной и измерительной технике и может быть использовано в различных автоматизированных системах сбора и обработки информации, а также диагностическогo контроля.

Известно устройство для обработки и сжатия информации, содержащее регистр текущей выборки, информационные входы которого являются информационными входами устройства, выходы разрядов подключены к информационным входам блока оперативной памяти и первым информационным входам регистра числа, выходы младших разрядов соединены с первыми информационными входами сумматора, вторые информационные входы которого подключены к первому выходу блока оперативной .памяти, ин- 20 формационные выходы сумматора соединены с информационными входами узла сравнения с допуском, выход которого подключен к первому входу первого элемента ИЛИ, выход которого соединен с суммирующим входом реверсивного счетчика, тактовым входом блока оперативной памяти и тактовым входом регистра числа, выход которого является первым выходом устройства, 30 второй выход и второй информационный вход регистра числа соединены соответственно с информационными. входом и выходом блока буферной памяти, тактовый вход которого объединен с вычитающим входом реверсивного счетчика и является первым тактовым входом устройства, управляющие вы-, зоды реверсивного счетчика соединены с первыми входами первых элементов

И, вторые входы которых являются вторыми тактовыми входами устройства, выходы реверсивного счетчика соединены с тактовыми входами узла сравнения с допуском.

Недостатком данного устройства является его низкая эффективность при.высокой динамике измеряемого процесса, так как существенной. вы-:. боркой может быть признано аномальное измерение, а при малом изменении входного сигнала идет накопление ошибки эа счет компромисса между быстродействием и шагом сравнений входной величины.

Наиболее близким яо технической сущности к предлагаемому является устройство, содержащее аналого-цифровой преобразователь, вход которого является входом устройства, генера" тор импульсов, выход генератора импульсов соединен с входом первого делителя частоты, выход которого соединен с управляющим входом аналогоцифрового преобразователя и с входом счетчика, триггер, выход которого .соединен с управляющими входами первого и второго ключей, выход аналого-цифрового преобразователя соединен с входом первого блока буферной памяти, регистр сдвига, выход которого подключен к первому входу вычислителя, второй вход которого объединен с входом регистра сдвига, выход вычислителя соединен с входом квадратора, выход квадратора соединен с входом усреднителя, выход которого соединен с первым входом блока сравнения, к второму входу которого подключен выход блока постоянной памяти, первый и второй выходы блока сравнения соединены соответственно с .вторыми входами первого и второго ключей., выход первого ключа соединен с суммирующим входом сумматора, выход второго ключа соединен с вычитающим входом сумматора, выход которого соединен с управляющим входом .коммутатора, информационные входы которого соеди" нены с соответствующими выходами второго делителя частоты, выход коммутатора соединен с управляющим входом регистра сдвига, выход второго Ьлока Ьуферной памяти является выходом устройства, третий ключ.

Ф

Недостатком известного устройства является его низкая информатив.-. ность, обусловленная негибкостью работы устройства, возможностью пропуска аномальности в существенной выборке и накоплением ошибки при малом изменении входного сигнала за счет шага определения существенной выборки.

Предлагаемое устройство предназначено для увеличения информативности измерительной информации и повышения ее достоверности эа. счет предварительной обработки.

Цель изобретения - повышение информативности и достоверности устройства

В устройство для сжатия и обработки информации, содержащее анало2 6 первый вход элемента И-НЕ и второй вход аналого-цифрового преобразователя оЬъединены и подключены к выходу генератора импульсов, выход делителя частоты соединен с вторыми входами четвертых элементов И каналов обраЬотки информации, вторым входом второго блока Ьуферной памяти и входом формирователя кодов, выходы которого соединены с вторыми входами элементов сравнения соответствующих каналов обработки информации, выход второго блока сравнения соединен с инверсными входами первых элементов

И блоков обработки информации и с вторым входом элемента ИЛИ, выход которого соединен с вторым входом элемента И-НЕ, выход которого соединен с вторым входом элемента И.

Предлагаемое устройство по сравнению с известным .отличается наличием дифференцирующего элемента, блока сравнения, формирователя кодов, элемента И-НЕ, элемента ИЛИ, блоков обработки, каждый из которых содержит четыре элемента И, элемент

ИЛИ, два элемента сравнения, триггер и их связями с остальными эле-; ментами схемы. Однако при их введении в указанной связи с остальными элементами схемы в устройство для сжатия и обработки информации указанные блоки проявляют новые свойства, что приводит к повышению информативности и достоверности путем отслеживания динамики и исключения аномальных значений входного сигнала.

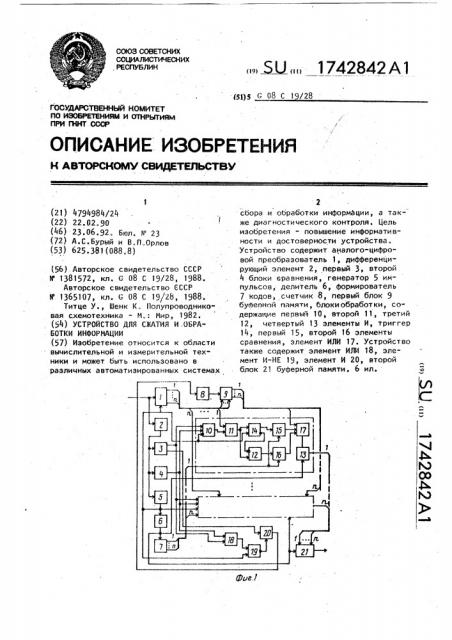

На фиг. 1 представлена функциональная схема устройства; на фиг.2реализация входного сигнала с малой динамикой; на фиг.3 - схема первого

Ьлока сравнения и временные диаграм" мы его работы; на фиг.4 - сигналы на входах соответствующих элементов устройства; на фиг.5 - структура и особенности дифференцирующего элемента; на фиг.б - структура формиро-: вателя кодов.

Устройство (фиг. 1) содержит аналого-цифровой преобразователь 1 (АЦП), дифференцирующий элемент 2, первый 3, второй 4 блоки сравнения, генератор 5 импульсов, делитель 6, формирователь 7 кодов,. счетчик 8, первый блок 9 буферной памяти, блоки обработки, содержащие первый 10, второй 11, третий 12, четвертый 13 элементы И, триггер 14, первый 15„

174284 го-цифровой:преобразователь, первый вход которого является. входом устройства, выходы соединены с одноименными и первыми входами первого блока буферной памяти, второй Ьлок буферной памяти, выход которого является выходом устройства, генератор импульсов, выход которого соединен с входом делителя частоты, 10 счетчик, первый блок сравнения и элемент И, введены формирователь кодов, дифференцирующий элемент, вто- рой блок сравнения, элемент И-НЕ, элемент ИЛИ и блоки обработки информации, каждый из которых выполнен на элементах И, элементе ИЛИ, триггере и элементах сравнения, выход первого элемента И соединен с первым входом второго элемента И, выход ко- 20 торого соединен с прямым входом третвего элемента И и с первым входом триггера, инверсный выход которого соединен с инверсным входом третьего элемента И, прямой выход триггера и выход третьего элемента И соединены с первыми входами соответственно первого и второго элементов сравнения выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с первым входом четвертого элемента И, выходы четвертых элементов И блоков обработки информации соединены с соответствующими первыми входами второго блока буферного памяти, вторые входы вторых элементов И блоков обработки информации подключены к соответствующим выходам аналого-цифрового преоЬразователя, выход счетчика соединен с вторым входом первого блока буферной памяти, выходы которого соединены с третьими входами эле". ментов ИЛИ соответствующих блоков обработки информации, вход дифференцирующего элемента подключен к входу устройства, выход соединен с входами генератора импульсов, первого и второго блоков сравнения, первый выход первого блока сравнении соединен

$0 с первым входом элемента ИЛИ и пер. выми прямыми входами первых элемен- . тов И всех блоков обработки информации, второй выход первого блока сравнения соединен с первым входом элемента И, выход которого соединен с входом счетчика, вторые входы триггеров и вторые входы первых элементов И каналов обработки информации, 7 174 второй 16 элементы сравнения, элемент ИЛИ 17, устройство также содержит элемент ИЛИ 18, элемент И-HE

19, элемент И 20, второй блок 31 буферной памяти. Формирователь 7 содержит счетчик 7, 1 и блок 7.2 постоянной памяти, вход считывания которого соединен с счетным входом счетчика

7.1 и выходом делителя 6, выходы счетчика 7.1 являются адресными вхо." дами блока 7.2.

АЦП 1 с управляющим входом может быть реализован ho известной схеме, дифференцирующий элемент 2 - по известной схеме, с дополнением, генератор 5 может быть выполнен на базе прецизионного триггера

Шмитта, у которого входной сигнал поступает на вывод, блок 3 - двухпороговый компаратор, блок 4известный блок 7.2 может быть выпол нен на NKC К 155 РУ 2,.элементы 15 и 16 сравнения - это компараторы, где для каждого разряда может быть использованв известная схема, передавая через мультиплексор на выход результат сравнения самых старших из несовпадающих разрядов. Для сравнения 4- и 5-разрядных чисел выпускются ИИС, например БМ 7485, счетчик

8 - асинхронный счетчик на вЬсемь, причем импульс старшего разряда поступает в блок 9 и одновременно на вход установки в "0" счетчика 8.

Вход устройства подключен к пер" вому входу АЦП 1 и входу дифференцирующего элемента 2, выход которого соединен с входами блоков 3 и 4,гене" ратора 5, выход которого подключен к второму входу АЦП 1, а через дели тель 6 - к входу блока 7 и второму входу блока 21, Выход д оторого является выходом устройства. Группа выходов АЦП 1 соединена с первыми (информационными) входами блока 9, второй вход которого подключен к выходу счетчика 8, счетный вход которого соединен с выходом элемента

И 20, Выход генератора 5 также под" ключен через элемент И"HE 19 к . второму входу элемента И 20, первый вход которого соединен с вторым вы" зодом блока 3, первый выход которого через элемент ИЛИ 18 подключен к второму входу элемента И-НЕ 19. Выход блока 4 соединен с вторым входом элемента ИЛИ 18 а также с инверсным г

2842 8 входом элемента И 1О каждого блока оЬработки, Второй, первый прямые входы, выхо3 ды элемента И 10 подключены соответственно к выходу генератора 5, первому выходу блока 3, а через элемент И 11 - к информационному первому входу триггера 14, прямой выход которого через элемент !5 сравнения, элементы ИЛИ 17, И 13 соединен с соответствующим первым входом Ьлока 21. соответствующий выход АЦП 1 подключен к второму входу элемента И 11, выход которого соединен через элемент И 12, элемент 16 с вторым входом элемента

ИЛИ 17. Третий вход элемента ИЛИ 17 каждого блока обработки подключен к соответствующему выходу блока 9.

2© Второй вход элемента И 1О также соединен с вторым (тактирующим) входом триггера 14, инверсный выход которого подключен к инверсному входу элемента И 12. Выход делителя 6 соединен с вторыми входами элементов

И 13 блоков обработки, вторые входы элементов 15 и 16 которых, кроме того, соединены о соответствующими выходами Формирователя 7. Устройство

36 позволяет B соответствии с динамикой входного процесса изменять частоту дискретизации, а также исключать аномальные измерения и накапливающиеся ошиЬки при малой динамике про"

35 ц

Устройство работает следующим образом.

На вход устройства сжатия и обработки информации поступают аналоговые сигналы от датчиков в виде меняющего во времени напряжения.

Для простоты описания работы устройства предположим;. что обслуживают только один датчик, который выдает непрерывный во времени ана" логовый сигнал U(t). Тогда при подаче питания на устройство его блоки устанавливаются в исходное состояние, в котором счетчик 8 импульсов, блок 9, элементы 15 и 16 сравнения очищены, генератор 5 начинает работу сразу же при включении устройства.

Поступающий на вход устройства аналоговый сигнал u(t) действует одновременно на АЦП1, частота дискретизации которого зависит от управляющего напряжения, и на диффереицирующий элемент 2. Последний сле1742842 10 дит за скоростью изменения напря" жения поступающего с датчика, и выполняет функцию Д U/Д t. Полученное на выходе дифференцирующего элемента

2 напряжение поступает одновременно на генератор 5, где в зависимости от величины поступившего напряжения изменяется частота генерируемого тактового сигнала, а также на блоки

3 и 4 сравнения, которые представляют собой компараторы. . Блок.4 производит сравнение поступающей величины d U/d t с величиной задаваемого опорного напряжения

U . Опорное напряжение U< выбирается заранее на основе имеющихся опытных данных или же расчетным путем, его физический смысл — максимальная скорость изменения входного процесса.

Следовательно, блок 4, выдавая. на выходе сигнал Д U/Д > U,, сигнализирует о наличии аномального измерения.

Сигнал о наличии аномального измере" ния с выхода блока 4 поступает одно- . временно для обработки на инвертирующий вход элемента И 10, а также на второй вход элемента ИЛИ 18. Блок

3 производит сравнение величины поступающего из Ьлока 2 напряжения d U/

/J t с величинами задаваемых напряжений И и U(U> (U) „Величина напряжения U< также выЬирается заранее на основе имеющихся априорных данных об измеряемых процессах или же рас четным путем.

Физический смысл введенной константы U> - это та минимальная скорость изменения входного процесса, при которой устройство воспринимает входной процесс, как изменяющийся во времени. Задаваемая величина U определяет коэффициент сжатия информации. Варьируя величиной константы .U<, можно изменять коэффициент сжатия в зависимости от программы испытаний.

Блок 3 сравнения, определяя величину

Uz а 3 U/gt C U,, фактически формирует коридор существенных отсчетов, т.е. скорость изменения процесса, попавшая в этот промежуток, требует формирования очередного существенного отсчета. В зависимости от результата сравнения констант U и U с величиной производной в текущий момент времени с выходов блока 3 выдается сигнал урпавления: соответственно на элементы И 10, ИЛИ 18 с первого выхода на элемент И 20 с второго. Временные диаграммы (фиг.3) поясняют работу

Ьлока 3, причем для него U+Ä= dU/4t.

Генератор 5, получая с выхода элемента 2 напряжение JU/Д с, вырьирует частотой тактовых импульсов, управляя, таким образом, частотой дискретизации АЦП 1, формированием временных ворот для элементов И 1О, И-НЕ

1.0 19„ работой триггера 14.и блока 9, Кроме того, с выхода генератора 5 импульсы поступают на. делитель 6 (частоты). Выдача информации в канал связи с выхода блока 21 происходит

15 под управлением импульсов с выхода делителя б, у которого постоянный коэффициент деления. При малой динамике процесса возможен. случай, когда выборка в течение К-тактов ра20 боты подряд признается несущественной.

В этом случае накаливается ошибка

Ь Б, максимум которой равен

hS = КАБ;, (i =. 1, К), 25 где hS. — ошибка в i-м такте рабо.1 ты, которая стремится в пределе к значению величины U (фиг.2).

В целях исключения подобной ситуации в предлагаемое устройство вво-

ЗО дится счетчик 8, который ведет под" счет количества следующих подряд несущественных выборок и при достижении заданного числа выдает сигнал в блок 9 буферной памяти. РаЬотой

35 счетчика Ь управляют элементы ИЛИ 18, И-НЕ 19, И 20 ° Элемент ИЛИ 18 при, наличии на его входе одного из сигналов из Ьлоков 3 и 4 формирует уп.. равляющий сигнал на элемент И-НЕ 19

40 и в случае совпадения его с импульсом от генератора 5 элемент И-НЕ 19 формирует "временные ворота" элементу И 20 на пропуск результата сравнения d U/4 t < U с второго выхода

l5 блока 3 в качестве счетного импульса на счетчик 8. . С группы выходов АЦП 1 результат измерения в цифровом коде поступает в блок 9 и на соответствующие входы

50 элементов И 11 каждого из блоков обработки под воздействием тактового импульса от генератора 5. Элемент

И 10 в .зависимости от комбинации сигналом на его входе, выполняя функцию 7 = Х1 ХЯ Х3, где 7, . Х1с Х2в

Х5- сигналы соответственно на выходе, первом, втором, третьем входах элемента, выдает управляющий импульс на элемент И 11, который, соответст11 1742842

12 венно, управляет раЬотой элемента

И 12 и одновременно поступает на первый (информационный) вход триггера 14.

Триггер 14 и элемент И 12 управляет поступлением на вход элементов

15 и 1b соответственно нечетной и четной существенных выборок, при этом инверсный выход триггера 14 10 соединен с инверсным входом элемента

И 12, С элементов 15 и 16 разряд существенной выборки поступает на эле" мент ИЛИ 17, на входе которого могут присутствовать разряды от несущественной выборки, пришедшей из блока 9, или же существенной с элементов 15 и 16. Один иэ этих разрядов поступает на вход элемента И 13 и по управляю- 20

Ча а айаг

40

Z = а а а а,Уа а ага 1ас азага Ма азагэ, Ìà

1 где а; - соответствует наличию "1". на i -м входе блока 21; а. - соответствует присутствию

"О", = 1,4, На входе эл мента 15 (16) каждого блока обработки может встретиться одна из следующих комбинаций Х:

X = b Ü × Ü Ь УЬгЬ ЧЬ b1, где Ь, Ь - означает наличие "1" на входе соответственно, от элемента 14(12) и формирователя 7.

На выходе элемента 15(16) "1" в следующем случае:

Y(1) = Ь,Ь,Yb. Ü УЬ,Ь, 1l0l1

v(O) = ЬгЬ, .

Тогда в нашем случае а; =ЬгЪ) "ЬгЬ МЬгЬ,, а =Бг 1 соответственно для каждого из четырех разрядов.

Наличие двух элементов сравнения (элементы 15 н 16) в каждом блоке обработки необходимо для повышения быстродействия работы устройства. Делитель 6 представляет собой обычный счетный триггер.

На выход из блока 21 буферной па" мяти существенная выборка выдается по приходящим тактовым импульсам с выхода делителя 6. В связи с тем, что коэффициент деления делителя 6 постоя нен, то выдача информации в канал связи с выхода Ьлока 21 происходит через интервалы времени щему сигналу, пришедшему от делителя

6 частоты, пропускает разряд измерения на соответствующий вход блока 21

Поясним работу элементов 15, 16 obpaботки. В связи с тем, что элементы

15 и 16 идентичны, опишем работу одного из них для случая, когда разрядность выдаваемого из АЦП 1 кода равна четырем (n = 4).

Формирователь 7 под воздействием тактового сигнала, прошедшего делитель 6, выдает контрольную константу, предположим 1010, и на вход блока 21

Ьуферной памяти должен пройти код, вес которого меньше или равен этой константе. На входах блока 21 может присутствовать следующий результат

7 °

I зага Ча аъага Ч а У а1а зага1Ч а+азага

c = kf

f У где f „- частота генератора 51.

- коэффициент, пропорциональный коэффициенту деления делителя 6.

В связи с этим достаточно обеспечить синхронизацию запуска часов устройства с часами системы обработки данных, например, по моменту поступления входного сигнала для осуществления принципиальной воэможности восстановления сигнала (фиг.4).

Входной процесс в виде напряжения представлен (фиг.4) на диаграмме. Имеются два характерных участка АБ,. БВ и точка Г - аномальный выброс. Участок

АБ характеризуется тем, что в его пределах для входного напряжения выполняется неравенство U <. †--

2 для участка БВ выполняется нерад 0вХ венство U

На участке AN на выходе диффереи-.. © цирующего элемента 2 (фиг.4б).:,напря-. . жение изменяется пропорционально скорости изиенения входного напря-- жения, в соответствии с ним изменяется частота генератора 5. (фиг.4в).

Напряжение на первом выходе Ьлока 3 изменяется ступенчато (диаграмма Г), на втором выходе блока 3 - диаграмма Д. На последней имеется отклик на аномальный выброс (точка Г на

ЗО

17 диаграмме 4а), который пока таковым не считается.

На выходе блока 4 - сигнал нулеv ! вои (фиг.4е) за исключением отклика на аномальный выброс. На выходе

АЦП 1 (фиг.4ж) присутствует дискрет- ная величина, совпадающая по величине с реализацией входного процесса в момент выдачи генератором 5 импульса. На участке ВГ реализация входного процесса имеет малую динамику (gV „/de -. V ) и частота опроса определяется в осйовном разрядностью счетчика 8. Точка Г характеризует работу блока 4 ° На выходе блока 4 имеется отдельный импульс, совпадающий по времени с аномальным выбросом, который отражается в виде аномального измерения на выходе АЦП 1 (Фиг.4ж).

Запись существенных отчетов в блок 21 осуществляется в моменты времени, пропорциональные частоте генератора 5 (диаграмма 4з). Результат возможной аппроксимации представлен на эпюре 4и. Отмеченные участки ГД, At ., ЕЖ (фиг.4а) аналогичны соответственно ВГ, БВ и АБ, Таким образом, частота дискретизации подлежащих передаче сигналов изменяется в соответствии со скоростью изменения входного процесса при упрощении устройства. Исключение аномальных измерений и теперь существенных выборок при малой динамике входного процесса позволяет повысить дос товерность получаемой информации.

Формула изобретени я

42842

14 ботки информации, каждый из которых выполнен на элементах И, элементе

ИЛИ, триггере и элементах сравнения, выход первого элемента И соединен с первым входом второго элемента И, выход которого соединен с прямым входом третьего элемента И и с первым входом триггера, инверсный выход которого соединен с инверсным входом третьего элемента И, прямой выход триггера и выход третьего элемента

И соединены с первыми входами соответственно первого и второго элементов сравнения, выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с первым входом четвертого элемента И, выходы четвертых элементов И блоков обработки информации соединены с соответствуюзими первыми входами второго. блока буферной памяти, вторые входы вторых элементов И блоков обработки информации подключены к соответствующим выходам аналого-цифрового преобразователя, выход счетчика соединен с вторым входом первого блока буферной памяти, выходы которого соединены с третьими входами элементов ИЛИ соответствующих блоков обработки информации, вход дифференцирующего элемента подключен к входу устройства, выход соединен с входами генератора импульсов. первого и второго блоков сравнения, первый выход первого блока сравнения соединен с первым входом элемента ИЛИ и первыми прямыми входами первых элементов И всех блоков обработки информации, второй выход

Устройство для сжатия и обработки информации, содержащее аналого-цифровой преобразователь, первый вход которого является входом устройства, выходы соединены с одноименными и первыми входами первого блока буферной памяти, второй блок буферной памяти, выход которого является выходом устройства, генератор. импульсов, выход которого соединен с входом частоты, счетчик, первый блок сравнения и элемент И, о т л и ч а ющ е е с я тем, что, с целью повышения информативности и достоверности устройства, в него введены формиро" ватель кодов, дифференцирующий элемент, второй блок сравнения, элемент И"НЕ, элемент ИЛИ и блоки обрапервого блока сравнения соединен с первым входом элемента И, выход которого соединен с входом счетчика. вторые входы триггеров и вторые входы первых элементов И каналов обработки информации, первый вход элемента И-НЕ и второй вход аналогоцифрового преобразователя объединены и подключены к выходу генератора импульсов, выход делителя частоты соединен с вторыми входами четвертых элементов И кайалов обработки информации, вторым входом второго блока буферной памяти и .входом формирователя кодов, выходы которого соединены с вторыми входами элементов сравнения соответствующих каналов обработки информации, выход второго блока сравнения соединен с ин+le НОЕ

1 I 1

А 1 1. 1 л1 к а к

Ь 1 4 Х

Х4 версными входами первых элементов

И блоков обработки информации и с вторым входом элемента ИЛИ, выход

1742842

16 которого соединен с вторым входом элемента И-НЕ, выход которого соединен с вторым входом элемента И.

1 !

Ф 1 t

1

1742842 и читОть1 тон 5

JJIILLLLJ ШШШ рямкннсна evan

xab

Г .1

Я, 1742842!

С вЂ”вЂ”

tg омрНЯ

BAOK 7 фиг, 6

Составитель О.Богомолова

TexÐe4 М.Моргентал Корректор А.Осауленко

Редактор И.Шулла.Заказ 2287 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101

1 Йе

1

t

1

1

Блок 2

«» ) Ивь1Х дирр. м-тА