Устройство для защиты переключающего транзистора от короткого замыкания в нагрузке

Иллюстрации

Показать всеРеферат

Использование: в бесконтактной коммутационнозащитной аппаратуре. Сущность изобретения: устройство содержит переключающий транзистор 1, транзистор 2, компараторы напряжений 4 и 5, элемент НЕ 6, конденсатор 7, элемент 2 И-НЕ 8, формирователь 9 коротких импульсов низкого уровня по фронту входного сигнала, формирователь 10 коротких импульсов низкого уровня по срезу входного сигнала. RS-триггер 11, резисторы 12-15. 1 ил.

COIO3 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 Н 02 Н 7/10

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

117

,1

К АВТОРСКОМУ СВИ4ЕТЕЛЬСТВУ (21) 4877526/07 (22) 26.10.90 (46) 23.06.92. Бюл. N 23 (71) Львовский научно-исследовательский радиотехнический институт (72) О.Л.Сидорович и А.И.Черников (53) 621,316.925.4 (088.8) (56) Авторское свидетельство СССР

К 886136, кл. Н 02 Н 7/10, 1980.

Электронная техника в автоматике, /

Под ред. Ю,И,Конева. — М,: Советское радио, 1978, вып. 10, с. 70. М» 1742933 А1 (54) УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ПЕРЕКЛЮЧАЮЩЕГО ТРАНЗИСТОРА QT RQРОТКОГО ЗАМЫКАНИЯ В НАГРУЗКЕ (57) Использование: в бесконтактной коммУтационно- защитной аппаратуре, Сущность изобретения: устройство содержит переключающий транзистор 1, транзистор 2, компараторы напряжений 4 и 5, элемент НЕ

6, конденсатор 7, элемент 2 И-НЕ 8, формирователь 9 коротких импульсов низкого уровня по фронту входного сигнала, формирователь. 10 коротких импульсов низкого уровня по срезу входного сигнала. RS-триггер 11, резисторы 12-15. 1 ил.

1742933

Изобретение относится к устройствам защиты силовых транзисторных ключей от коротких замыканий в нагрузке и может быть использовано в бесконтактной коммутационно-защитной аппаратуре.

Известно устройство для защиты переключающего транзистора, содержащее датчик тока в цепи эмиттера защищаемого транзистора и вспомогательный транзистор, база которого через резистор соединена с датчиком тока, а через второй резистор и диодный ключ — с коллектором защищаемого транзистора, причем эмиттер-коллектор вспомогательного транзистора включен параллельно эмиттеру-базе защищаемого транзистора, дополнительный резистор, включенный между базами защищаемого и вспомогательного транзисторов.

Известно также устройство, содержащее датчик тока в цепи эмиттера защищаемого транзистора и вспомогательный транзистор, база-эмиттер которого подключен параллельно датчику тока, а коллектор подключен к базе защищаемого транзистора.

Недостатком известного устройства является низкий КПД за счет рассеиваемой мощности в датчике тока.

Цель изобретения — повышение КПД устройства.

Использование изобретения позволит повысить КПД на 25% по сравнению с известным устройством при одинаковых режимах работы, Для повышения КПД устройства в него введены новые элементы, а именно: два компаратора, логический элемент НЕ, логический элемент 2И-НЕ, формирователь коротких импульсов низкого уровня по срезу входного сигнала, формирователь коротких импульсов низкого уровня по фронту входнаго сигнала, RS-триггер с инверсными входами, конденсатор, дополнительные резисторы и их связи.

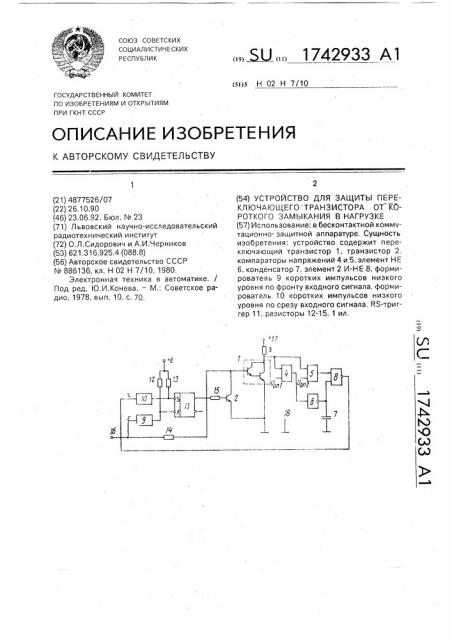

На чертеже приведена принципиальная электрическая схема предлагаемого устройства.

Устройство защиты содержит переключающий транзистор 1, второй транзистор 2, нагрузку 3, компараторы 4 и 5 напряжения, логический элемент НЕ 6, конденсатор 7, логический элемент 2И-НЕ 8, формирователь 9 коротких импульсов низкого уровня по фронту входного сигнала, формирователь 10 коротких импульсов низкого уровня по срезу входного сигнала, RS-триггер 11 с инверсными входами, резисторы 12-15, управляющую шину 16, шину 17 питания и общую шину 18.

Переключающий транзистор 1 подключен эмиттером к общей шине 18, к которой также подсоединены эмиттер второго транзистора 2 и первый вывод конденсатора 7.

Коллектор переключающего транзистора 1 подсоединен к первому выводу нагрузки 3 и измерительным входам компараторов 4 и 5, причем на входы опорных сигналов компараторов 4 и 5 подаются опорные напряжеНИя Uon) И Оол2 СООтВЕтСтВЕННО. ВЫХОД первого компаратора 4 соединен с входом логического элемента Н Е 6, выход которого

10 соединен с первым входом логического элемента 2И-НЕ 8, выход которого соединен с

15 входом формирователя 10 коротких импульсов низкого уровня по срезу входного сигнала, выход которого подключен к S-входу стора 13 и выходу формирователя 9 коротких импульсов низкого уровня по фронту входного сигнала, вход которого подключен к управляющей шине 16 и первому выводу резистора 14, второй вывод кото25 рого соединен с базой переключающего транзистора 1 и коллектором второго транзистора 2, база которого через резистор 15 подключена к прямому выходу триггера 11.

Вторые выводы резисторов 12 и 13, подключены к источнику+ Е питания микросхем, а второй вывод нагрузки 3 подключен к шине

17 питания.

Формирователь коротких импульсов

35 низкого уровня по фронту входного сигнала реализован по известной схеме; Формирователь коротких импульсов низкого уровня по срезу входного сигнала реализован также по известной схеме

Устройство работает следующим образом.

В исходном состоянии при подаче питания на шину 17 транзистор 1 закрыт, его коллектор и измерительные входы компараторов 4 и 5 находятся под потенциалом питания. Опорное напряжение компаратора 4 должно быть больше напряжения насыщения транзистора 1, но меньше определенного значения напряжения, соответствующего напряжению коллектор-эмиттер транзистора 1, находящегося в активном режиме.

ОпоРное напРЯжение компаРатоРа 5 Uon2 должно быть больше определенного значе50 ния, соответствующего напряжению коллектор-эмиттер транзистора 1, находящегося в активном режиме, но меньше напряжения питания устройств1. На выхо55 дах компараторов 4 и 5 устанавливается нулевой потенциал, потому что напряжение питаниЯ больше Uon1l4 больше Uon2 На пеРRS-триггера с инверсными входами 11 и к первому выводу резистора 13, а R-вход триг20 гера 11 подключен к первому выводу рези1742933

25

35

В случае короткого замыкания в нагруз- 40 вый вход логического элемента 2И-НЕ 8 подается сигнал компаратора 4, инвертированный логическим элементом 6, а на второй вход — сигнал компаратора 5, В результате на входе второго формирователя импульсов появляется сигнал, соответствующий переходу от низкого уровня к высокому.

На выходе формирователя 10 коротких импульсов низкого уровня по срезу входного сигнала изменения сигнала не происходит, следовательно, на входах триггера 11 R и S присутствует напряжение высокого уровня, и с выхода триггера на базу второго транзистора 2 через резистор 15 подается напряжение низкого уровня, которое удерживает транзистор 2 в закрытом состоянии.

В момент подачи входного сигнала на управляющую шину 16, соответствующего переходу входного напряжения от низкого уровня к высокому, срабатывает формирователь 9 коротких импульсов низкого уровня по фронту входного сигнала и íà R-входе триггера 11 появляется короткий импульс низкого уровня, таким образом дублируется обнуление триггера 11. Одновременно входной сигнал подается на базу переключающего транзистора 1 и он переходит в режим насыщения, при этом на выходах компаратора устанавливается .сигнал низкого уровня. На первом входе логического элемента 2И-НЕ 8 высокий уровень напряжения. В результате на выходе логического элемента 2И-HE 8 уровень сигнала не изменяется и не изменяется состояние формирователя 10 коротких импульсов низкого уровня по срезу входного сигнала и триггера 11. Второй транзистор 2 остается закрытым. ке 3 переключающий транзистор 1 выходит из насыщения в область активного режима работы, при этом при достижении напряжением коллектор-эми гер транзистора 1 величины, превышающей выбранное значение опорного напряжения компаратора 4 Upn, на выходе компаратора 4 устанавливается напряжение низкого уровня, которое после инвертирования логическим элементом НЕ 6 поступает на первый вход логического элемента 2И-НЕ 8, на второй вход последнего поступает высокий потенциал с выхода компаратора 5, так как величина U<> z больше величины напряжения коллектор-эмиттер транзистора 1, находящегося в области активного режима работы, На выходе логического элемента 2И-НЕ 8 напряжение изменяется от высокого уровня к нулевому, при этом формирователь коротких импульсов низкого уровня по срезу

55 входного сигнала 10 вырабатывает короткий импульс низкого уровня, подаваемый на

S-вход триггера 11. На прямом выходе триггера 11 устанавливается высокий уровень напряжения, которым открывается транзистор 2. Открытие транзистора 2 шунтирует база-эмиттерный переход транзистора 1 и запирает его. После устранения короткого замыкания для повторного запуска переключающего транзистора 1 необходимо снять сигнал с управляющего входа и вновь подать его:

При включении устройства в момент перехода переключающего транзистора 1 из режима отсечки в режим насыщения напряжения коллектор-эмиттер изменяется от напряжения питания до напряжения насыщения транзистора и какое-то время его значение находится в зоне Оотг и Uon1, что соответствует режиму короткого замыкания, и это способно вызвать ложное срабатывание схемы защиты, Для исключения ложных срабатываний вводится конденсатор 7, который дает крагковременную задержку поступления сигнала высокого уровня на первый вход логического элемента 2И-НЕ 8 в момент включения переключающего транзистора 1.

Формула изобретения

Устройство для защиты переключающего транзистора от короткого замыкания в нагрузке, содержащее транзистор, коллектор которого предназначен для подключения к базе переключающего транзистора, о т л и ч а ю щ е е с я тем, что, с целью повышения КПД устройства, введены два компаратора напряжений, элемент НЕ, элемент 2И-НЕ, конденсатор, формирователь коротких импульсов низкого уровня по фронту входного сигнала, формирователь коротких импульсов низкого уровня по срезу входного сигнала, RS-триггер с инверсными входами и два резистора, причем измерительные входы компараторов напряжений предназначены для подключения к коллектору переключающего транзистора, а другие входы компараторов подключены к соответствующим источникам опорного напряжения, выход первого компаратора соединен с входом элемента НЕ, выход которого соединен с первым входом элемента 2И-Н Е, выход второго компаратора соединен с вторым входом элемента 2И-Н Е, выход которого соединен с входом формирователя коротких импульсов низкого уровня по срезу входного сигнала, выход которого соединен с S-входом триггера, Rвход которого соединен с выходом формирователя коротких импульсов низкого уровня по фронту входного сигнала, вход

1742933

20

30

40

50

Составитель О,Сидорович

Техред M.Ìoðãåíòàë . Корректор M.Äåì÷èê

Редактор И,Горная

Заказ 2292 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат Патент", г. Ужгород, ул,Гагарина, 101 которого подключен к управляющей шине и через первый резистор предназначен для подключения к базе переключающего транзистора, прямой выход триггера через второй резистор подключен к базе транзистора, эмиттер которого предназначен для подключения к эмиттеру переключающего транзистора, при этом конденсатор включен между выходом элемента НЕ и об5 щей шиной.