Логический элемент

Иллюстрации

Показать всеРеферат

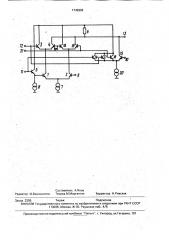

Изобретение относится к импульсной технике и позволяет расширить функциональные возможности логического элемента . Сущность изобретения: логический элемент содержит первый 1, второй 2, третий 3, четвертый 4 и пятый 5 транзисторы, резистор 6, первый 7 и второй 8 источники тока, первую 9 и вторую 10 шины опорного напряжения, первый 11 и второй 12 входы, выход 13 первый 14, второй 15, третий 16, четвертый 17, пятый 18 и шестой 19 дополнительные транзисторы, дополнительный источник тока 20 и третий вход 21. 1 ил.

„,59„„1742992 А1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)л Н 03 К 19/086

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО. ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Изобретение относится к импульсной нять достаточно стабильный уровень логитехнике,. в частности к логическим элемен- . ческого нуля в элементе и приводит к увелитам на переключении тока, и может быть чению задержки. использовано в сверхскоростных интег- Наиболее близким потехнической сущральных схемах для построения комбинаци-. ности является логический элемент, реалионной части логических схем. ЗуЮщий функциЮ F.(X1X2) = Х1 Х2 на двух

Известны элементы,. выполненные. из уровнях переключения тока, т.е, формирует двух и более токовых ключах, с двумя уров-- функцию, являющуюся частным случаем нями переключения тока, причем макси- .требуемой при Хз = О. Недостатком этого К) мальная задержка таких схем примерно элемента явля":-.тся невозможность реализаравна задержке одного токозого ключа.. циифункции F(Х1,Х2,ХЗ)=Х1Х2+Х2Хзоттрех

Однако в элементе, построенном. дан- переменных, каждая из которых отлична от ным образом, через резистор, формирую- . const.. щий логический перепад, может . Цель изобретения — расширение, функодновременно протекать О, 1, 2 и более то- циональных возможностей логического элеков токовых ключей. Для .стабилизации мента. уровня логического нуля в элемент введен Поставленная цель достигается тем, что параллельноэтомурезисторуограничитель- в логический элемент, содержащий пять ный диод, что, однако, не позволяет сохра- транзисторов, резистор, два источника то1 (21)4786754/21 (22) 24.01.90 (46) 23,06.92. Бюл. N- 23 (71) Ленинградское объединение электронного приборостроения "Светлана" (72) А.П.Голубев и С,Л,Афиногенов (53) 621.374 (088,8) (56) Микросхемы интегральные, Кристалл

К1520ХМ2, Исходные данные по проектированию заказных матричных БИС на базовом . матричном кристалле И60.734,106, 1984, с.

43-44, 54, Алексеенко А.Г., Шагурин И.И. Микросхемотехника — M.: Радио и связь, 1982, с.

77, рис.2.24.

2 (54) ЛОГИЧЕСКИЙ ЭЛЕМЕНТ (57) Изобретение относится к импульсной технике и позволяет расширить функциональные возможности логического элемента. Сущность изобретения: логический элемент содержит первый f, второй 2, третий 3, четвертый 4 и пятый 5 транзисторы, резистор 6, первый 7 и второй 8 источники тока, первую 9 и вторую 10 шины опорного напряжения, первый 11 и второй 12 входы, выход 13 первый 14, второй 15, третий 16, четвертый 17, пятый 18 и шестой 19 допол- нительные транзисторы, дополнительный источник тока 20 и третий вход 21. 1 ил;

I 1742992

: ка, две шины опорного напряжения, два входа и выход, эмиттеры первого и второго транзисторов, подключены к первому источнику тока, .коллектор первого транзистора соединен с эмиттерами третьего и четвертого транзисторов, база первого транзистора соединена с эмиттером пятого транзистора и вторым источником тока, база второго транзистора — с первой шиной опорного напряжения, база четвертого транзистора подключена к.второй шине опорного напряжения, база пятого транзистора соединена. с первым. входом„база третьего транзистора соединена с вторым входом, коллектор четвертого транзистора подключен к первому выводу резистора и выходу, коллектор третьего транзистора подключен к коллектору пятого транзистора и второму выводу резистора, введены шесть дополнительных транзисторов, дополнительный источник тока и третий вход, эмиттеры первого. второго, третьего и четвертого дополнительных транзисторов соединены с дополнительным источником тока, коллектор второго транзистора соединен с эмиттерами пятого и шестого дополнительных транзисторов, база: первого дополнительного транзистора соединена с базой пятого транзистора, база второго дополнительного транзистора — с первой шиной опорного напряжения, база . третьего дополнительного транзистора — с базой шестого дополнительного транзистора и третьим входом, база четвертого дополни. тельного транзистора соединена с вторым входом, а коллектор четвертого дополнительного транзистора — с коллекторами первого, третьего, пятого дополнительных транзисторов и третьего транзистора, коллекторы второго и шестого дополнительных транзисторов соединены с коллектором четвертого транзистора, база пятого дополнительного транзистора соединена .с второй шиной опорного напряжения.

Предложенный логический элемент обладает новизной и существенными отличиями, Введение дополнительных элементов, укаэанных в формуле изобретения, позволяет реализовать функцию F(X1,Хг,Хз) = Х)Хг+

+ ХгХз, причем через резистор протекает одновременно не более. одного тока первого источника тока или дополнительного источника тока, поэтому не требуется . подключения ограничительного диода, а задержка практически равна задержке элемента, реализующей функцию F(X>,Хг) = Х1х х Хг.

На чертеже представлена электрическая схема логического элемента, реализу. ющего функцию F(X1,Хг,Хз) = Х1Хг + ХгХз.

15

25

45 полнительных транзисторов 14, 16, 18 и третьего транзистора 3, коллекторы второго и шестого дополнительных транзисторов

15, 19 соединены с коллектором четвертого транзистора 4, база пятого дополнительно50 го транзистора 18 соединена с второй шиной опорного напряжения 10.

Предлаженный логический элемент функционирует следующим образом.

На входы 11; 12, 21 подаются сигналы, 55

Логический элемент, реализующий функцию F(X>,X2,X ) = Х1Хг + ХгХз, содержит пять транзисторов 1 — 5, резистор 6, два источника.тока 7, 8, две.шины опорного.напряжения 9, 10, два входа 11, 12 и выход 13, эмиттеры первого и второго транзисторов 1, 2 подключены к первому источнику тока 7, коллектор первого транзистора 1 соединен с эмиттерами третьего и четвертого транзисторов 3, 4, база первого транзистора 1 соединена с эмиттером пятого транзистора 5 и вторым источником тока 8, база второго транзистора 2 — с первой шиной опорного напряжения 9, база четвертого транзистора

4.подключена к второй шине опорного напряжения 10, база пятого транзистора 5 соединена с первым входом 11, база третьего транзистора 3 соединена с вторым входом.12, коллектор четвертого транзистора 4 подключен к первому выводу. резистора 6 и выходу 13, коллектор третьего транзистора 3 подключен к коллектору пятого транзистора

5 и второму выводу резистора.6. Согласно изобретению в логический элемент введены шесть дополнительных транзисторов 14 — 19, дополнительный источник тока 20, третий вход 21, причем эмиттеры первого, второго, третьего и четвертого дополнительных транзисторов 14-17, соединены с дополнительным источником тока 20, коллектор второго транзистора 2 соединен с эмиттерами пятого и шестого дополнительных транзисторов 18, 19, база первого дополнительного транзистора 14 соединена с базой пятого транзистора 5, база второго дополнительно-. го транзистора 15 — с первой шиной опорного напряжения 9, база третьего дополнительного транзистора 16 — с базой шестого дополнительного транзистора 19 и третьим входом 21, база четвертого дополнительногоо транзистора 17. соединена с вторым 12 входом, а. коллектор четвертого дополнительного транзистора 17 — с коллекторами первого 14, третьего 16, пятого досоответстВующие уровню логического нуля или единицы. В таблице представлены пути протекания токов первого источника тока 7 (!1) и дополнительного источника тока 20 (!г) при различных комбинациях входных сигналов (всего комбинаций 2 + 8), а также зна1742992 . чение на выходе 13 (в случае, когда один из с первым входом, база третьего транзистотоков протекает через резистор 6, на выхо- ра соединена с вторым входом, коллектор де 13 формируется уровень логического ну-- четвертого транзистора подключен к перволя, в противном случае — уровень му выводу резистора и выходу, коллектор логической единицы). Как следует изтабли- 5 третьего транзистора подключен к коллекцы, логический элемент реализует функцию тору пятого транзистора и второму выводу

Р(Х1,Х,Хз) = Х1Хг + Х2Хз, причем одновре- - резистора,отл ич а ю щийс я тем, что, с .менно через резистор 6 протекает не более * целью. расширения функциональных воз.одного тока (или 11, или l2), т,е. уровень можностей, в логический элемент введены . логического нуля остается постоянным. 10 шесть дополнительных транзисторов, доТаким образом, предложенный логиче-, полнительный источник тока и третий вход, ский элемент по сравнению с известным, причемэмиттеры первого, второго, третьего позволяет реализовать функцию от трех пе- . и четвертого дополнительных транзисторов ременных, т.е. расширить функциональные соединены с дополнительным источником возможности, причем задержка остается 15 .тока, коллектор второго транзистора соедипрактически равной задержке элемента, ре- нен с эмиттерами пятого и шестого дополниализующегофункциюотдвух переменных. тельных:транзисторов, база первого дополнительного транзистора соединена с

Ф о р м у л а и з о б р е т е н и я базой пятого транзистора, база второго до20 полнительного транзистора — с первой шиной

Логический элемент, содержащий пять опорного напряжения, база третьего дополтранзисторов, резистор, два источника то- . нительHoго транзистора — с базой шестого ка,.две шины опорного напряженйя,. два ..дополнительноготранзистораитретьимвховхода и выход, эмиттеры первого и второго дом, база четвертого дополнительного трантранзисторов подключены к первомуисточ- 25 зистора соединена с вторым входом, а нику тока, коллектор первого транзистора . коллектор четвертого дополнительного трансоединен с эмиттерами третьего и четверто- зистора — с. коллекторами первого, третьего, го транзисторов,.база первого:транзиатора. пятого дополнительных транзисторов и соединена с эмиттером пятого транзйстора третьего транзистора, коллекторы второго и и вторым источником тока, база второго 30 шестого дополнительных транзисторов соетрайзистора — с первой шиной опорного динены с. коллектором четвертого транзистонапряжения; база четвертого транзистора: . ра, база пятого дополнительного транзистора . подключена к второй шине опорного напря-, соединена с второй шиной опорного напряжения, база пятого транзистора соединена жения.

П р и м е ч а н и е: Протекание тока по пути коллектор-эмиттер транзисторов с номером

i обозначено как Ть а протекание тока через резистор 6 — как R ..Запись — (Tj+ T ) —. означает, что ток протекает параллельно через оба транзистора (после них он вновь складывается).

1742992

12

Составитель А.Янов

Редактор .И.Ванюшкина Техред М.Моргентал Корректор Н.Ревская

Заказ 2295 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская нэб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101