Устройство для приема, регенерации и передачи относительного биимпульсного сигнала

Иллюстрации

Показать всеРеферат

Изобретение относится к технике цифровой связи. Цель - повышение защищенности от импульсных помех, устранения линейных искажений биимпульсного сигнала и обеспечение работы на многоточечной линии связи большой протяженности. В известное устройство дополнительно введены фазочастотный корректор 2, ограничитель амплитуд 4, пороговый блок 5, опорный генератор 6, блок автоподстройки 7, приемник синхробайта 8, первый , второй 11 и третий 13 блоки ключей, инвертор 18, формирователь синхробайта. Полученные на выходе формирователя переходов 6 импульсы корректируют работу блока автоподстройки 7, который выдает синхросигналы, используемые для декодирования и регенерации ОБС. Блок 16 запрета передачи вводит в заголовок посылки ОБС синхробайт, а приемник 9 сихробайта выделяет этот синхробайт и дает разрешение дешифратору декодированного двричного сигнала. Второй и третий блоки ключей 11 и 13 обеспечивают разделение режимов передачи и регенерации , 3 ил. сл С

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 Н 04 В 1/38

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4828564/09 (22) 23.05.90 (46) 23,06.92. Бюл. N 23 (71) Научно-производственное объединение автоматизации и систем управления на же- лезнодорожном транспорте "Союэжелдоравтоматизация" (72) Е.И.Мольвер и А.А.Кочетков (53) 621.394.62 (088.8) (56) Авторское свидетельство СССР

N. 824460, кл, Н 04 .В 5/02, 1979. (54) УСТРОЙСТВО ДЛЯ ПРИЕМА; РЕГЕНЕРАЦИИ И ПЕРЕДАЧИ ОТНОСИТЕЛЬНОГО

БИИМПУЛЬСНОГО СИГНАЛА (57) Изобретение относится к технике цифровой связи. Цель — повышение защищенности от импульсных помех, устранения линейных искажений биимпульсного сигнала и обеспечение работы на многоточечной линии связи большой протяженности. В из„„50„„1743004 А1 вестное устройство дополнительно введены фазочастотный корректор 2, ограничитель амплитуд 4, пороговый блок 5, опорный генератор 6, блок автоподстройки 7,.приемник синхробайта 8, первый 10, второй 11 и третий 13 блоки ключей, инвертор 18, формирователь синхробайта. Полученные на выходе формирователя переходов 6 импульсы корректируют работу блока автоподстройки 7, который выдает синхросигналы, используемые для декодирования и регенерации ОБС. Блок 16 запрета передачи вводит в заголовок посылки ОБС синхробайт, а приемник 9 сихробайта выделяет этот синхробайт и дает разрешение дешифратору декодированного двричного сигнала. Второй и третий блоки ключей 11 и 13 обеспечивают разделение режимов передачи и регенерации, 3 ил.

1743004

Изобретение относится к устройствам передачи сигналов по линиям связи (модемам) и может быть использовано в устройствах передачи дискретных сигналов, а именно для кодирования относительным биимпульсным сигналом (ОБС).

Цель изобретения — повышение защищенности от импульсных помех, устранение линейных искажений биимпульсного сигна ла и обеспечение работы на многоточечной линии связи большой протяженности.

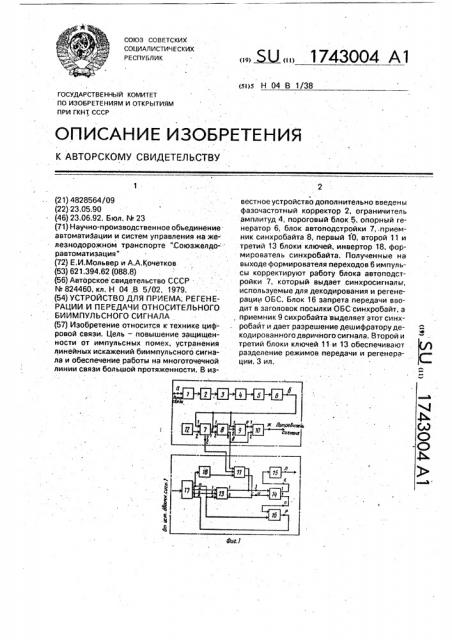

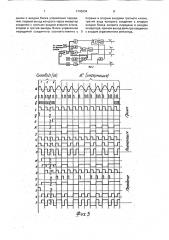

На фиг,1 представлена структурная схема предлагаемого устройства; на фиг,2 — то же, блок управления передачей; на фиг,3— временные диаграммы работы.

Устройство для приема, регенерации и передачи относительного биимпульсного, сигнала включает входной усилитель 1. фазочастотный корректор 2, фильтр 3, ограничитель 4 амплитуд, пороговый блок 5, формирователь 6 переходов, блок 7 автоподстройки, блок 8 выделения двоичного сигнала, приемник 9 синхробайта, первый

10 и второй 11 ключи, опорный генератор

12, третий ключ 13, формирбватель 14 относительного биимпульсного сигнала, выходной усилитель 15, блок 16 запрета передачи, . блок 17 управления передачей, первый инвертор 18.

Блок управления передачей содержит блок 19 регистров, первый мультиплексор

20, второй мультиплексор 21, первый элемент ИЛИ 22, второй элемент ИЛИ 23, синхронизатор. 24, тактовый генератор 25, первый делитель 26 частоты; второй делитель 27 частоты, счетчик 28 выбора регистра. счетчик-формирователь 29 адреса, второй инвертор 30, элемент И 31, третий элемент ИЛИ 32 и источник 33 синхробайта.

При поступлении относительного биимпульсного сигнала (ОБС) на входной усилитель 1 . (фиг,За) он проходит последовательно блоки 1-6, и на выходе формирователя 6 переходов появляются однополярные импульсы (фиг.36). Эти импульсы по входу t, блока 7, регулируют частоту синхросигнала. формируемого в блоках 12 и

7 (фиг.Зв.г), Импульсы переходов также управляют блоками 8 и 9.

Блок 7 автоподстройки представляет собой делитель частоты с переменным коэффициентом деления, регулируется автоматически совмещением импульсов переходов и периода синхросигнала (СС), получаемого от опорного .генератора 12.

Так, например, если импульсы переходов

ОБС опережают сигнал СС, то коэффициент деления уменьшается, и наоборот, если импульсы переходов отстают от сигнала СС, то коэффициент деления увеличивается.

Блок 8 основан на принципе временного стробирования с высокой частотой интервалов между приходящими импульсами пЕреходов, Длинный интервал соответствует двоичному сигналу (ДС) "0", а короткий интервал — ДС "1". Принцип использует свойство ОБС, состоящее в том, что биты "0" и "1" двоичного сигнала в ОБС отличаются в два раза по частоте прямоугольного колебания, причем фазы колебаний на границах тактов не имеют значения..

Приемник синхробайта 9 построен на основе счетчика-делителя на 10, у которого на входе "R (запирания и обнуления) включена интегрирующая цепочка. В исходном состоянии, когда нет импульсов перехода, конденсатор заряжен, и на R установлен высокий потенциал. счетчик заперт и обнулен по входу 2 блока 9. При поступлении первого импульса перехода по входу 2 блока

9 конденсатор разря>кается(постоянная цепи разряда равна длительности сформиро.ванного импульса перехода через йуль), и на входе R устанавливается низкий потенциал, счетчик отпирается, и с второго импульса начинается счет, Причем каждый импульс поддерживает конденсатор в разряженном состоянии, так как постоянная цепи заряда равна длительности двух тактов. Когда счет30 чик досчитывает до 10, он становится на блокировку, и на выходе 2 блока 9 устанавФ ливается.высокий потенциал, который отпирает первый ключ 10. В результате через него к потребителю поступает остаток син35 хробайта и информационная последовательность со "стартовым" импульсом вначале. В режиме регенерации приемник синхробайта 9 не участвует, поэтому сигнал в искаженном виде с выхода 2 блока выде40 ления двоичного сигнала 8 подается на второй ключ 11;

Так как пороговый блок 5 представляет собой компаратор, переключающийся только при воздействии двухполярного колеба45 ния определенной амплитуды, а импульсная помеха имеет, как правило, преобладание одной полярности, то при действии пачки импульсных помех компаратор перебрасывается далеко не от всех помех в пачке. При

50 этом.для того, чтобы счетчик досчитал до 10, необходимо, чтобы компаратор перебросился как минимум; 11 раз.

Кроме того, необходимо, чтобы длительность интервалов перебрасывания компа55 ратора или длительность между импульсами переходов через нуль при действйи пачки помех была менее длительности двух тактов сигнала. Иначе конденсатор успеет зарядиться, и счетчик обнулится, Так как указанные условия в пачках помех выполняются

1743004 редко. то это и обеспечивает повышение сутствует сигнал "0", то с его выхода сигнал защищенности приемника, "1" в виде ГП выдается по выходу 1. .Выдача ДС из блока 17 на выход 2 и СС Когда по входу 2 поступает сигнал ЗП на выход 3 осуществляется только при низ- (сигнал 1), то блоки 26, 29 и 31 запираются, ком потенциале на входе 2 (отсутствие сиг- 5 и выдача ГП становится невозможной. Если нала запрета передачи (ЗП). А это имеет ЗП снимается (сигнал "0"), то блоки 26, 29 и место при свободности канала связи, что 31 отпираются, и на выходе 1 выставляется исключает столкновение сообщений. Если в ГП (сигнал "1"). Когда выдача данных.по выблоке 17 есть информация, то он выставляет ходу 2 закончена, то на выходе 2 счетчика 29 на выход 1 сигнал готовности передачи (ГП) 10 появляется сигнал "1", который запирает по в виде высокого потенциала. При этом вто- входу 2 элемент 32, и ГП с выхода 1 снимарой ключ 11 и блок 16 запираются, а третий ется (сигнал "0"). При этом отпирается блок ключ 13 отпирается, Далее от блока 17 по- 16, и на вход 1 вновь подается сигнал ЗП, ступают сигналы ДС и СС (фиг.2н,о) на вы- который обнуляет и запирает счетчик 29, ходы 1 и 2 блока 14. Сформированный ОБС 15 делитель частоты 26 и запирает И 32. (фиг.2к) через блок 15 выдается в линйю связи (фиг.3л). Формула изобретения

Блок 17 работает следующим образом.

Данные от источника двоичного сигна- устройство для приема, регенерации и ла по шине ш1 (вход 1) поступают в парал- 20 передачи относительного биимпульсного лельном виде побайтно в блок регистров, а сигнала, содержащее входной и выходной на управляющие входы регистров по шине усилители, опорный генератор, фильтр, ш2 поступают с интервалами 1 с сигналы формирователь переходов, блок выделения перезаписи байтов данных из одного реги- двоичного сигнала, формирователь относистра в другой, Сигналы перезаписи форми- 25 тельного биимпульсногосигнала, отл и ч а юруются из частоты тактового генератора 25 . щ е е с я тем, что, с целью повышения при помощи второго делителя 27 частоты и защищенности от импульсных помех, счетчика 28 выбора регистра, Данные с вы- уменьшения линейных искажений биимхода последнего регистра блока 19 подают- пульсного сигнала и обеспечения возможся в параллельном виде по шине ш3 на вход 30 ности работы на многоточечной линии связи данных второго мультиплексора 21, асинх- большой протяженности,. введены фазочаробайт от источника 33 в виде постоянно стотный корректор, вход которого соединен действующих сигналов логической "1" в па- с выходом входного усилителя, а выход — с раллельном виде подается на вход данных входом фильтра, последовательно соедипервого мультиплексора 20. На адресные 35 ненные ограничительамплитуд и пороговый входы мультиплексоров 20 и 21 по шине ш4. блок, выход которого соединен с входом подаются управляющие коды. сформиро- формирователя переходов, выход которого ванные от тактового генератора 25 при по- соединен с объединенными первыми входамощи первого делителя 26 частоты и ми блока автоподстройки, блока выделения счетчика-формирователя 29 .адреса. Вы- 40 двоичного сигнала и приемника синхробайбранные по очереди синхробайт и байт дан- та, второй вход которого соединен с первым ных, выдаются побитно мультиплексорами выходом блока выделения двоичного сигна20 и 21 на первой и второй входы второго . ла, второй вход которого соединен с обьедиэлемента ИЛИ 23 и с его выхода — на первый ненными первым входом первого и второго вход синхронизатора 24, на второй вход ко- 45 ключей, второй вход которого соединен с торого подается синхросигнал с выхода первым выходом блока автоподстройки, первого делителя 26 частоты. Синхрониза- второй выход которого соединен с вторым тор 24 выдает в передатчик по выходу 2 входом блока выделения двоичного сигнасинхронизированный двоичный сигнал, а по ла, а второй вход блока автоподстройки совыходу3 выдается синхросигнал. 50 единен с выходом опорного генератора, По шине ш3 данные из блока 19 регист- выход приемника синхробайта соединен с

pos также поступают в первый ИЛИ 22, ко- . вторым входом первого ключа, .первый и торый фиксирует появление единичных второй выходы второго ключа соединены битов на шине и выдает сигнал "1" на пер- соответственно с первыми вторым выходом вый вход И 31. Если при этом на втором:55 третьего ключа и соответственно с первым входе элемента И 31 присутствует также "1", . и вторым входами формирователя относито сигнал "1" с выхода И 31 поступает на тельного биимпульсного сигнала, первый первой вход третьего ИЛИ 32 и если при выход которого через выходной усилитель этом на втором входе третьего ИЛИ 32 при- . соединен с входом канала связи, а второй

его выход через блок запрета передачи сое1743004 динен с входом блока управления передачей, первый выход которого через инвертор . соединен с третьим входом второго ключа, второй и третий выходы блока управления передачей соединены соответственно с 5 й// /с

er Фамя

urw///a г

Ж (оЮорма////я) /////фсй///(Сб)

/ / первым и вторым входами третьего ключа, третий вход которого соединен с вторым входом блока запрета передачи и входом инвертора, причем выход фильтра соединен с входом, ограничителя амплитуд.