Устройство для ввода информации

Иллюстрации

Показать всеРеферат

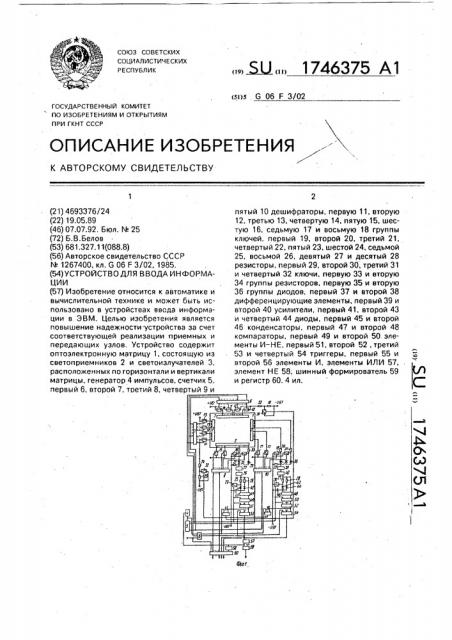

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах ввода информации в ЭВМ. Целью изобретения является повышение надежности-устройства за счет соответствующей реализации приемных и передающих узлов. Устройство содержит оптоэлектронную матрицу 1, состоящую из светоприемников 2 и светоизлучателей 3, расположенных по горизонтали и вертикали матрицы, генератор 4 импульсов, счетчик 5, первый 6, второй 7, третий 8, четвертый 9 и пятый 10 дешифраторы, первую 11, вторую 12, третью 13, четвертую 14. пятую 15, шестую 16, седьмую 17 и восьмую 18 группы ключей, первый 19, второй 20, третий 21, четвертый 22, пятый 23, шестой 24, седьмой 25, восьмой 26, девятый 27 и десятый 28 резисторы, первый 29, второй 30, третий 31 и четвертый 32 ключи, первую 33 и вторую 34 группы резисторов, первую 35 и вторую 36 группы диодов, первый 37 и второй 38 дифференцирующие элементы, первый 39 и второй 40 усилители, первый 41, второй 43 и четвертый 44 диоды, первый 45 и второй 46 конденсаторы, первый 47 и второй 48 компараторы, первый 49 и второй 50 элементы И-НЕ, первый 51, второй 52 , третий 53 и четвертый 54 триггеры, первый 55 и второй 56 элементы И, элементы ИЛИ 57, элемент НЕ 58, шинный формирователь 59 и регистр 60. 4 ил. (Л С

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)ю G 06 F 3/02

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

l ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4693376/24 (22) 19.05.89 (46) 07.07.92. Бюл. М 25 (72) Б.В.Белов (53) 681.327.11(088.8) (56) Авторское свидетельство СССР

N 1267400, кл. G 06 F 3/02, 1985, (54) УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах ввода информации в ЭВМ. Целью изобретения является повышение надежности-устройства за счет соответствующей реализации приемных и передающих узлов, Устройство содержит оптоэлектронную матрицу 1, состоящую из светоприемников 2 и светоизлучателей 3, расположенных по горизонтали и вертикали матрицы, генератор 4 импульсов, счетчик 5, первый 6, второй 7, т0етий 8, четвертый 9 и!

Ж 1746375 А1 пятый 10 дешифраторы, первую 11, вторую

12, третью 13, четвертую 14, пятую 15, шестую 16, седьмую 17 и восьмую 18 группы ключей, первый 19, второй 20, третий 21, четвертый 22, пятый 23, шестой 24, седьмой

25, восьмой 26, девятый 27 и десятый 28 резисторы, первый 29, второй 30, третий 31 и четвертый 32. ключи, первую 33 и вторую

34 группы резисторов, первую 35 и вторую

36 группы диодов, первый 37 и второй 38 дифференцирующие элементы, первый 39 и второй 40 усилители, первый 41, второй 43 и четвертый 44 диоды, первый 45 и второй

46 конденсаторы, первый 47 и второй 48 компараторы, первый 49 и второй 50 элементы И вЂ” НЕ, первый 51, второй 52, третий

53 и четвертый 54 триггеры, первый 55 и второй 56 элементы И, элементы ИЛИ 57, элемент НЕ 58; шинный формирователь 59 и регистр 60. 4 ил.

1746375

55

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах ввода информации в ЭВМ.

Цель изобретения — повышение надежности устройства за счет соответствующей реализации приемных и сканирующих узлов.

На фиг,1 приведена структурная схема устройства; на фиг.2 — временные диаграммы работы устройства; на фиг.3 — пример структуры построения и последовательности сканирования оптоэлектронной матрицы; на фиг,4 — пример матричного включения светоизлучателей.

Устройство содержит оптоэлектронную матрицу 1, состоящую из светоприемников

2 и светоизлучателей 3, расположенных по горизонтали и вертикали матрицы, генератор 4 импульсов, счетчик 5, дешифраторы

6-10 с первой по восьмую группы ключей

11-18, с первого по десятый резисторы 1928, с первого по четвертый ключи 29-32, первую 33 и вторую 34 группы резисторов, первую 35 и вторую 36 группы диодов, первый 37 и второй 38 дифференцирующие элементы, первый 39 и второй 40 усилители, с первого по четвертый диоды 41-44, первый

45 и второй 46 конденсаторы, первый 47 и второй 48 компараторы, первый 49 и второй

50 элементы И-НЕ, с первого по четвертый григгеры 51-54, первый 55 и второй 56 элементы И. элемент ИЛИ 57, элемент НЕ 58, шинный формирователь 59 и регистр 60.

Устройство работает следующим образом.

Генератор 4 импульсов вырабатывает последовательность импульсов (фиг.2,1). которая поступает на тактовый вход счетчика

5 и первый вход третьего дешифратора 8, Счетчик 5 преобразует последовательность импульсов в двоичный код, С выхода младшего разряда счетчика 5 (фиг,2.2) импульсы поступают на входы разрешения первого и второго дешифраторов 6 и 7, управляющие входы первого и второго ключей 29 и 30, первые входы элементов И-НЕ 49,50 и тактовые входы первого 51 и второго 52 триггеров, С остальных выходов счетчика 5 импульсы поступают на входы первого 6. второго 7, четвертого 9 и пятого 10 дешифраторов, и входы группы информационных входов регистра 60.

Данное техническое решение дает возможность как параллельной, так и последовательной работы горизонтальных и вертикальных частей оптоэлектронной матрицы 1. При параллельной работе устройства без юстирования светоизлучателей 3 и светоприемников 2 возможно попадание светового импульса вертикально расположенных светоизлучателей на горизонтально расположенные светоприемники и горизонтальной расположенных светоизлучателей на вертикально расположенные светоприемники. Однако, в реальной оптоэлектронной матрице наложение паразитного светового импульса идет лишь в центре сторон периметра оптоэлектронной матрицы 1, так как световой угол светоизлучателей как правило составляет 70 — 100, причем максимальная мощность излучения приходится на центральную часть, составляющую около

30о, поэтому органиэация сканирования светоизлучателей 3 и светоприемников 2 в последовательности, указанной на фиг.3, полностью решает вопрос о паразитном наложении импульсов, На фиг.3 представлен вариант стратегии параллельного сканирования. СХ вЂ” горизонтальные светоизлучатели, CY вертикальные светоизлучатели, ФХ вЂ” горизонтальные. светоприемники, ФУ вЂ” вертикальные св топриемники, 1,2 последовательность сканирования. Например, параллельно сканируются 1 СХ и 1СУ, 1ФХ и 1ФУ. Начало сканирования 1 СХ правый нижний гол, При срабатывании первого светоизлучателя 1 СХ свет в окно первого светоприемника 1 ФУ. расположенного в середине левой стороны периметра, не попадает, так как угол между лучом первого светоизлучателя 1 СХ, направленного в окно первого светоприемника 1 ФУ, и направлением оси окна первого светоизлучателя 1 СХ составляет 60о (полный световой угол равен

120о). Последний светоизлучатель 1 CX расположен в середине нижней стороны периметра, последний приемник 1 ФУ расположен в левом нижнем углу периметра и, таким образом, угол между лучом данного светоизлучателя, направленного в окно последнего светоприемника 1 ФУ и направлением оси окна последнего светоизлучателя

1 СХ составляет 90 и, таким образом, свет последнего светоизлучателя 1 СХ не попадает в окно данного светоприемника 1 ФУ.

Преимуществом параллельного сканирования является увеличение скорости работы устройства вдвое.

Необходимо отметить, что две группы ключей в управлении светоизлучателями дают возможность включения светоизлучателей матрично (фиг.4), чем обеспечивается уменьшение количества оборудования.

Рассмотрим работу устройства на примере шести тактов работы горизонтальных светоизлучателей 3 и горизонтальных светоприемников 2 оптоэлектронной матрицы 1 при их последовательности сканирования.

1746375

Предположим, что четвертый светоизлучатель 3 по каким-либо причинам (большом времени наработки или после воздействия спецфакторов) значительно уменьшил мощность излучения, Между пя- 5 тым светоизлучателем 3 и пятым светоприемником 2 находится указатель, Переключение и опрос оптических каналов в матрице происходит последовательно во времени подачей соответствующего кода на 10 входы дешифраторов 6 и 9.

В первом такте Т> замыкается первый ключ группы ключей 11 в соответствии с временной диаграммой (фиг.2:3) и первый ключ второй группы ключей 12 (фиг.2.4) и 15 срабатывает первый горизонтальный светоизлучатель 3. Светоприемники 2 как и светоизлучатели 3 включены матрично с той лишь разницей. что ключи шестой группы ключей 16 работают на размыкание. В пер- 20 вом такте замыкается первый ключ пятой группы ключей 15 в соответствии с временной диаграммой (фиг.2,5) и размыкается первый ключ шестой группы ключей 16 (фиг.2.4). Все остальные ключи шестой груп- 25 пы ключей 16 находятся в замкнутом состоянии и ток остальных светоприемников, находящихся в цепи первого ключа пятой группы ключей 16, кроме первого, замыкаетсх на отрицательный полюс источника пи- 30 тания. Оптический сигнал первого светоприемника 2, преобразованный в электрический, через первый диод первой группы диодов 35 поступает на вход первого дифференцирующего элемента 37. Рези- 35 сторы первой группы резисторов 33 предназначены для ограничения тока светоприемников 2. Третий резистор 21 предназначен для обеспечения тока выбранного светоприемника 2. Дифференцирующий 40 элемент 37 выделяет переменную составляющую, которая поступает на вход первого усилителя 39. С выхода усилителя 39 сигнал поступает на первый вход первого компаратора 47 (фиг,2.6) и первые выводы седьмого 45 и восьмого резисторов 25 и 26. С второго вывода седьмого резистора 25 сигнал поступает на анод первого диода 41. С второго вывода восьмого резистора 26 сигнал поступает на катод второго диода 42, далее через 50 диоды 41 и 42 на второй вход первого компаратора 47 и второй вывод первого конденсатора 45 (фиг.2,7). В первую половину такта первый ключ 29 разомкнут в соответствии с временной диаграммой, показанной 55 нэ фиг.2.2 и конденсатор 45 разряжается по цепи — второй диод 42, восьмой резистор 26 (фиг.2.7 2Т) или заряжается по цепи — седьмой резистор 25, первый диод 41 (фиг.2.7

ЗТ). Седьмой и восьмой резисторы служат для ограничения тока заряда (разряда) конденсатора 45. Во вторую половину такта первый ключ 29 замыкает второй вывод седьмого резистора 25 и положительный полюс второго диода 41 на отрицательный полюс источника питания устройства, У ровень сигнала на выходе усилителя 39 во второй половине такта в присутствии указателя такой же, как и в первой и выше в отсутствии указателя, так как уровень сигнала на выходе усилителя 39 в первой половине такта содержит лишь уровень, определяемый разбросом параметров элементов, в основном светоприемников 2. Во второй половине такта с выхода усилителя

39 поступает сигнал с уровнем, являющимся суммой сигналов разброса параметров элементов светоизлучателя 3. Таким образом, сигнал на выходе усилителя 39 во второй половине такта либо такой же как в первой, либо выше, Поэтому во второй половине такта по цепи восьмой резистор 26. второй диод 42 ток не течет (диод 42 закрыт), первый диод 41 также закрыт, так как на положительном полюсе первого диода 41 потенциал ниже, чем на его отрицательном полюсе. В результате сигнал запоминается на конденсаторе 45. Поэтому в первой половине такта на первый и второй входы компаратора 47 поступает одинаковый уровень сигнала, во второй половине такта — одинаковый в присутствии указателя и разной если его нет. Компаратор 47 срабатывает и выдает сигнал в виде импульса на второй вход первого элемента И-НЕ 49 (фиг.2.8).

Сигнал Собщ, поступающий с выхода светоприемника. представляет собой сумму С, +

Сщ + Сл + Ср. где С вЂ” сигнал светоизлучателя, C — шум, С, — постоянная составляющая внешнего светового потока. C> — сигнал, получаемый за счет разброса параметров элементов.

В предлагаемом техническом решении две ступени выделения рабочего сигнала; первая — дифференцирующая цепь 37, отсекающая постоянную составляющую Сп. вторая — седьмой и восьмой резисторы 25 и 26, первый и второй диоды 41 и 42, первый ключ

29, первый конденсатор 45 и первый компаратор 47. вычитающие Ср. С выхода элемента И-ХЕ 49 (фиг.2.9) импульсы поступают на установочный вход первого триггера 51 и устанавливает его в ноль. Первый триггер 51 импульсом с выхода младшего разряда счетчика 5 периодически устанавливается в единицу, Ширина импульсов на выходе первого триггера 51 определяется, в основном, временем нарастания переднего фронта сигналов светоприемников 2. На тактовый вход третьего триггера 53 с второго выхода треть1746375

30

40 его дешифратора 8 поступают тактовые импульсы в соответствии с временной диаграммой. показанной на фиг.2.11. С выхода первого триггера 51 на установочный вход третьего триггера 53 поступает импульс, удерживающий его в состоянии единицы (фиг,2,12), С первого выхода третьего дешифратора на первый вход первого элемента И 55 поступают импульсы в соответствии с фиг.2.13. С выхода элемента И 56 на управляющий вход третьего ключа 31 поступает сигнал в соответствии с фиг,2.14, 1Т, 2Т, 3Т.

На входах и выходе элемента ИЛИ 57 сигналы не изменяются, выход шинного формирователя имеет высокий импеданс и устройство для ввода информации не возбуждает внешнее управляющее устройство.

В четвертом такте в результате деформации светоизлучателя вследствие старения или воздействия спецфакторов уровень сигнала на выходе светоприемника сравним с сигналом Сш, поэтому в начале второй половины четвертого такта на второй вход первого элемента И вЂ” НЕ 49 поступает ноль, на выходе элемента 49 — единица, на выходе первого триггера 51 и втором входе первого элемента И 55 — единица. С первого выхода третьего дешифратора 8 (фиг.213) через первый элемент И 55 сигнал поступает на управляющий вход третьего ключа 31 (фиг.2.14). Ключ 31 закорачивает первый резистор 19 увеличивая ток соответствующего светоизлучателя и, соответственно, мощность его излучения. После появления сигнала на входе светоприемника устройство работает также, как и в предыдущих тактах с той лишь разницей, что после срабатывания первого триггера 51 через первый элемент И 55 происходит размыкание ключа 31, В пятом такте между светоизлучателем и соответствующим светоприемником находится указатель, поэтому с выхода светоприемника поступает сигнал, состоящий из суммы Сш + Cn + Ср. С выхода первой дифференцирующей цепи 37 на вход первого усилителя 39 поступает сигнал Сп + Ср. Так как на первом и втором входах компаратора

47 весь пятый такт присутствуют одинаковые уровни сигналов (фиг.2,6,2,7, 5Т), то на выходе компаратора 47 и выходе элемента

И вЂ” НЕ 49 сохраняется существующий уровень (фиг.2.8, 2.9, 5Т), первый триггер 51 по тактовому входу устанавливается в единицу, с установочного входа третьего триггера

53 снимается удерживающий его в исходном состоянии уровень и по тактовому входу (фиг.2,11, 6Т) устанавливается в ноль (фиг,2,12, 6Т). На втором входе первого элемента И 95 и первом информационном входе регистра 60 устанавливается ноль. На выходе элемента ИЛИ 57, управляющем входе шинного формирователя 59, входе элемента НЕ 58 и входе генератора импульсов 4 устанавливается ноль (фиг.2.15, 6Т).

Генератор 4 импульсов прекращает выработку импульсов (фиг.2.1, 6Т). На выходе шинного формирователя 59 появляется информация о присутствии указателя (фиг,2.16, 6Т). На выходе элемента НЕ 58 и входе разрешения записи регистра 60 устанавливается единица (фиг.2.17, 6Т). В регистр 60 записывается информация, Если внешнее устройство готово принять информацию, то с него на третий вход третьего дешифратора 8 и управляющий вход регистра 60 поступает ноль (фиг.2.18, 6Т). С выхода регистра 60 снимается информация о найденной координате (фиг,2,19, 6Т), После приема информации внешнее устройство снимает ноль с входа устройства, срабатывает третий дешифратор (фиг.2,11, 6Т), По тактовому .:ходу срабатывания третий триггер 53, на е«о входе и первом входе элемента ИЛИ 57 появляется единица, на выходе шинного формирователя 59 и выходах регистра 60 появляется высокий импеданс (фиг.2.16, и 2.19 — 6Т) и запускается генератор импульсов 4 (фиг.2,1, 6Т)..

Вторая половина устройства работает аналогично первой.

Формула изобретения

Устройство для ввода информации, содержащее оптоэлектронную матрицу, состоящую из групп светоприемников и светоизлучателей, расположенных по горизонтали и вертикали матрицы, генератор импульсов, счетчик, первый и второй дешифраторы, первый и второй усилители, первый и второй компараторы, первый и второй триггеры, первый элемент И, регистр, причем выходы регистра являются информационными выходами устройства. а группа входов соединена с группой выходов счетчика и группами входов первого и второго дешифраторов, тактовые входы первого и второго триггеров соединены с выходом младшего разряда счетчика, тактовый вход которого соединен с выходом генератора импульсов, выходы первого и второго усилителей соединены с вторыми входами соответственно первого и второго компараторов, о т л и ч а ю. щ е е с я тем, что, с целью повышения надежности устройства, в него введены третий, четвертый и пятый дешифраторы, с первой по восьмую группы ключей, с первого по десятый элементы нагрузки в виде резисторов, с первого по четвертый ключи, первая и вторая группы элементов нагрузки в виде оезисторов, первая и вторая группы элементов од1746375

5

15

30

50 ностороннеи проводимости в виде диодов, первый и второй дифференцирующие элементы, с первого по четвертый элементы односторонней проводимости в виде диодов. первый и второй накопительные элементы в виде конденсаторов, первый и второй элементы И-КЕ, третий и четвертый триггеры, второй элемент И,элемент ИЛИ, элемент НЕ, шинный формирователь, минусовая шина источника питания устройства соединена с первыми выводами с первого по четвертый резисторов, с первыми выводами первого и второго конденсаторов, с входами с первого по четвертый ключей и входами ключей шестой и восьмой групп, плюсовая шина источника питания устройства соединена с входами ключей первой, третьей, пятой и седьмой групп, шина логического нуля устройства соединена с информационными входами с первого по четвертый триггеров и информационным входом шинного формирователя, выход которого является выходом готовности устройства, а управляющий вход соединен с выходом элемента ИЛИ, управляющим входом генератора импульсов и входом элемента НЕ, выход которого соединен с тактовым входом регистра, управляющий вход которого соединен с третьим входом третьего дешифратора и управляющим входом устройства0, а первый и второй входы соединены соответственно с первым и вторым входами элемента ИЛИ и выходами соответственно третьего и четвертого триггеров, входы установки которых соединены с вторыми входами соответственно первого и второго элементов И и выходами соответственно первого и второго триггеров, установочные входы которых соединены с выходами соответственно первого и второго элементов И вЂ” НЕ, вторые входы которых соединены с выходами соответственно первого и второго компараторов, а первые входы соединены с управляющими входами первого и второго ключей, вторым входом третьего дешифратора и выходом младшего разряда счетчика, тактовый вход которого соединен с первым входом третьего дешифратора, второй выход которого соединен с тактовыми входами третьего и четвертого триггеров, а первый выход соединен с первыми входами первого и второго элементов

И, выходы которых соединены суправляющими входами соответственно третьего и четвертого ключей, выходы которых соединены соответственно с вторыми выводами первого и второго резисторов и первыми выводами соответственно пятого и шестого резисторов, вторые выводы которых соединены с входами ключей соответственно второй и четвертой групп, входы светоизлучателей соединены с выходами ключей первой, второй, третьей и четвертой групп, управляющие входы которых соединены с соответствующими группами выходов первого и второго дешифраторов, входы четвертого и пятого дешифраторов соединены с группой выходов счетчика, а группы их выходов соединены с управляющими входами ключей пятой, шестой, седьмой и восьмой групп соответственно, группы выходов светоприемников соединены соответственно с выходами ключей пятой и седьмой групп и первыми выходами резисторов соответственно первой и второй групп, вторые выводы которых соединены с выходами ключей соответственно шестой и восьмой групп и анодами диодов соответственно первой и второй групп, катоды которых соединены с вторыми выводами соответственно третьего и четвертого резисторов и входами соответственно первого и второго дифференцирующих элементов. выходы которых соединены с входами соответственно первого и второго усилителей, выход первого усилителя соединен с первыми выводами седьмого и восьмого резисторов, выход второго усилителя соединен с первыми выводами девятого и десятого резисторов, второй вывод первого конденсатора соединен с первым входом первого компаратора, катодом первого и анодом второго диодов, катод которого соединен с вторым выводом восьмого резистора, анод первого диода соединен с выходом первого ключа и вторым выводом седьмого резистора, второй вывод второго конденсатора соединен с первым входом второго компаратора, катодом третьего и анодом четвертого диодов, катод которого соединен с вторым выводом десятого резистора, анод третьего диода соединен с выходом второго ключа и вторым выводом девятого резистора.

1746375

1746375 иг 4

Составитель А.Алексеев

Техред М.Моргентал Корректор Н.Бонкало

Редактор Н.Химчук

Производственно-издательский комбинат "Патент", r Ужгород, ул.Гагарина, 101

Заказ 2395, Тираж Подписное

В НИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5