Интегральная схема

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровым интегральным схемам на основе биполярных транзисторов, в частности к ТТЛ. В интегральной схеме повышение помехоустойчивости и обеспечение управления порогом переключения достигаются при введении области р+с концентрацией примеси 5-1018 N 10 под эмиттеры всех транзисторов , за исключением выходного. 2 ил сл с

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4789331/25 (22) 09.02.90 (46) 07.07.92. Бюл. № 25 (71) Научно-производственное объединение

"Интеграл" (72) И,Н.Карпов. И,И,Кисель, И.В,Малый, А.В.Силин, Г.А.Смирнов и В.С,Чувелев (53) 621.382 (088.8) (56) Шило В.Л. Популярные цифровые микросхемы. Справочник. М., Радио и связь, 1987, с.,18.

ЕПВ ¹ 0055908, кл. Н 03 К 19/08, 1982.

Шило В.Л,Популярные цифровые микросхемы. Справочник. M.. Радио и связь, 1987, с.24.

Изобретение относится к полупровод. никовой электронике, а более конкретно к полупроводниковым интегральным схемам на основе биполярных транзисторов.

Известна интегральная схема, включающая выполненные на полупроводниковой подложке в эпитаксиальном слое и-типа первый и второй транзисторы, диод Шоттки и резистор, притчем катод диода Шоттки соединен с входом схемы, а анод подключен к базе первого транзистора, соединенной с шиной питания через резистор, эмиттер первого транзистора соединен с базой второго транзистора, эмиттер которого соединен с общей шиной, а коллектор образует выход.

Недостатком известного решения является пониженная помехозащищенность, обусловленная пониженным порогом переключения схемы.

Известна интегральная схема, включающая первый, второй и третий транзисторы, диод Шоттки и резистор и выполненная на

„, . Ж„, 1746439 А1 (si>s Н 01 1 27/082

@ 1 t 08$ (54) ИНТЕГРАЛЬНАЯ СХЕМА (57) Изобретение относится к цифровым интегральным схемам на основе биполярных транзисторов, в частности к ТТЛ. В интегральной схеме повышение помехоустойчивости и обеспечение управления порогом переключения достигаются при введении областио сконцентрациейпримеси510 <

Шоттки соединен с входом схемы, а анод— с базой первого транзистора, соединенной с шиной питания. Эмиттер первого транзи-, стора соединен с базой второго транзистора через дополнительные первый и второй резисторы, эмиттер второго транзистора соединен через дополнительные третий и четвертый резисторы с базой третьего транзистора, а эмиттер третьего транзистора соединен с общей шиной.

Недостатком известного решения является необходимость в большом количестве дополнительных схемных элементов (резисторов) для обеспечения управления порогом переключения схемы.

Наиболее близкой к предлагаемой является интегральная схема, содержащая первый транзистор, база которого через первый резистор соединена с шиной питания, а с входом схемы — через диод, включенный в направлении к входу схемы.

Коллектор первого транзистора через вто1746439 рой резистор соединен с шиной питания, а эмиттер соединен с базой второго транзистора. Эмиттер второго транзистора соединен с базой третьего транзистора, эмиттер которого соединен с общей шиной. Интегральная схема выполнена на полупроводниковой подложке р-типа проводимости в отделенных друг от друга изолирующими областями участках эпитаксиального слоя и;типа проводимости со скрытыми слоями

E и -типа проводимости. В участках эпитаксиального слоя сформированы области актив+ной и пассивной базы р типа проводимости

+ и эмиттера и -типа проводимости первого, второго и третьего транзисторов.

Недостатком, известного решения явля ется невозможность управления порогом переключения схемы из-за фиксированных значений прямых падений напряжения диода и переходов база — эмиттер первого, второго и третьего транзисторов.

Целью изобретения является обеспечение возможности-управления порогом переключения и повышение помехоустойчивости известной интегральной схемы путем изменения значений прямого падения напряжения переходов база-эмиттер транзисторов.

Указанная цель достигается тем, что в интегральной схеме при формировании области р -базы с концентрацией примеси 5х

+ х10

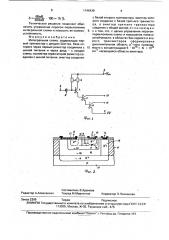

На фиг.1 изображена предлагаемая интегральная схема; на фиг.2 — поперечный разрез активной структуры первого, второго и третьего транзисторов интегральной схемы.

Интегральная схема содержит первый транзистор 1, база которого через первый резистор 2 соединена с шиной питания+ V<

3, а с входом 4 схемы — через диод 5, включенный в направлении к входу 4 схемы. Коллектор транзистора 1 через второй резистор б соединен с шиной питания 3, а эмиттер— с базой второго транзистора 7. Эмиттер транзистора 7 соединен с базой третьего транзистора 8, эмиттер которого соединен с общей шиной 9; Интегральная схема выполнена на полупроводниковой подложке

10 р-типа проводимости в отделенных друг от друга изолирующими областями 1.1 участках эпитаксиального слоя 12 и-типа проводимости со скрытыми слоями 13 n+-типа проводимости. В участках эпитаксиального слоя 12 сформированы области 14, 15, 16 активной базы р- и пассивной базы р -типа проводимости и эммитера n — типа проводимости первого, второго и третьего транзисторов 1, 7 и 8, область 17 образует коллектор транзисторов 1, 7, 8, а область 18

5 — область р -базы под и -эмиттером, сформированную перед формированием и эмиттера одновременно с областью 15

+ пассивной базы р -типа, при этом концентрация примеси р-типа в области 18 находит10 сявпределах510

18 х1Б превышает глубину эмиттера х1э.

Известно, что порОг переключения известной интегральной схемы определяется так:

15 . Vx = ЧБЭ1+ V БЭ2+ чБЭЗ VD, rAe ЧБЭ1, 2, з — прямое падение напряжения база — эмиттер первого, второго и третьего транзисторов;

VD — прямое падение напряжения диода, 20 т.е. практически полностью определяется прямым падением напряжения база-эмиттер транзисторов. Прямое падение напряжения база — эмиттер и-р-и-транзистора при прочих. равных условиях пропорционально

InN (концентрации примеси в р-области ир-перехода). Введение области р -типа.под змиттером приведет к увеличению концент25 рации NA в области перехода и, в свою очередь, к.увеличению прямого падения

30 напряжения НБэ транзисторов. Верхняя граница концентрации примеси 10 см обусловлена снижением пробивного напряжения перехода базы эмиттер транзисторов, а нижняя N > 5 х10 см обусловлена, 35 ухудшением омического контакта к пассив + ной р -базе транзистора, формируемого од+ новременно с .р -областью под эмиттером.

Введение р -области под эмиттером, помимо увеличения напряжения ЧБэ, приведет к

40 уменьшению омического сопротивления базы и дополнительно улучшит частотные свойства транзистора. Поскольку в схеме использованы транзисторы с диодом Шоттки, то уменьшение напряжения ЧБэ за счет

45 уменьшения сопротивления базы несущественно в сравнении с увеличением напряжения ЧБэ за счет изменения концентрации в базе под эмиттером, так как основная часть тока базы протекает через диод Шоттки в

50 коллектор, а не через сопротивление базы.

Так, в п-р-п-.òðàíçèñòîðå интегральной схемы с концентрацией примеси в базе КБ- сФ и эмиттере Мэ= ...см дополнительное легирование области базы под эмиттером

55 до уровня N Б= ...см позволило увеличить ! -3 напряжение 1/Бэ на значение 30 мВ при токе базы I =- .0,5 мА и тем самым повысить помехоустойчивость интегральной схемы к отпирающей помехе 60 мВ, что составило

1746439

Э

+Vee

OV Риг. М

<о Риг. 2.

Составитель В,Кремлев

Редактор А.Алексеенко Техред М.Моргентал Корректор Э.Лончакова

Заказ 2399 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат" Патент",г.ужгород,уд. Гагарина,101 д =, оо-Б- 100 = 15 % .

60мВ

Техническое решение позволяет обеспечить управление порогом переключение интегральной схемы и повысить ее помехоустойчивость.

Формула изобретения

Интегральная схема, содержащая первый транзистор с диодом Шоттки, база которого через первый резистор соединена с шиной питания и через диод — с входом схемы, коллектор через второй резистор соединен с шиной питания, эмиттер соединен с базой второго транзистора, змиттер кото.рого соединен с базой третьего транзистора, а эмиттер третьего транзистора соединен с общей шиной, о т л и ч а ю щ а я5 с я тем, что, с целью управления порогом переключение схемы и повышения помехоустойчивости, в областях баз первого и второго транзисторов сформирована дополнительная область р+-типа проводи10 мости с концентрацией 5 10 < N < 10 см, касающаяся области эмиттера.