Цифровой синтезатор частот

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ll0 ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

Р1 1 И

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4836405/21 (22) 07.06,90 (46) 07,07.92. Бюл. 1Ф 25 (71) Центральное конструкторское бюро

"Алмаз" (72) 8.Г.Аристов (53) 621.374 (088.8) (56) Авторское свидетельство СССР

l4 1307586, М. Кл. 5 Н 03 К 23/66, 1985.

Авторское свидетельство СССР .

hh 1234966, M. Кл. 5 Н 03 1 7/18, 1984— прототип, Ы,, 1746531 А1 (я) Н 03 L7/18, Н 03 К 23/66 (54) ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ (57) Сущность изобретение: устройство содержит генератор 1 опорной частоты, управляемый генератор 2, вы".oäíóþ шину 3, делители 4 и 6 частоты с переменным коэффициентом деления, кодовые входы 5 и 7, счетчики 8 и 12 импульсов, блок 10 элементов Л, цифроаналоговые преобразователи

11 и 13, фильтры 14 и 15 нижних частот, элементы И 16, 17 и 22, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 18, триггеры 19 и 20, элемент

И-НЕ 21. 2 ил.

1746531

15 вход 7, первый счетчик 8 импульсов, регистр 20

9 хранения, блок 10 элементов .И, первый

30

50

Изобретение относится к радиотехнике и может быть использовано для генерации сетки частот в приемопередающей и контрольноо-измерительной an паратуре.

Цег ь изобретения — повышение быстродействия вхождения в синхронизм при одновременном повышении спектральной чистоты выходного сигнала.

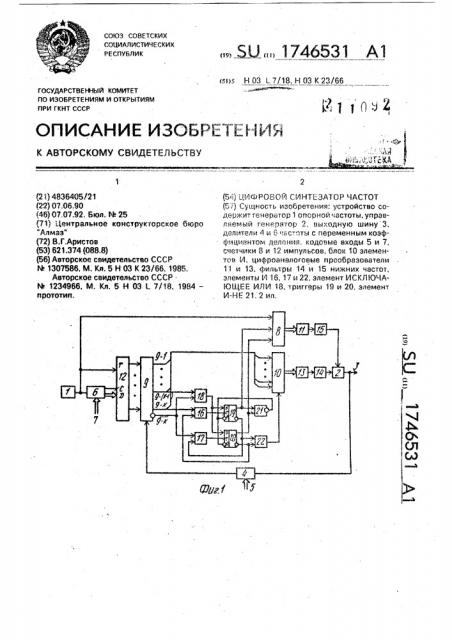

На фиг. 1 приведена структурная элект рическая схема цифрового синтезатора частот; на фиг. 2 — структурная электрическая схема блока элементов И.

Цифровой синтезатор частот содержит генератор 1 опорной частоты, управляемый генератор 2, выходную шину 3, первый де.литель 4 частоты с переменным коэффициентом деления, первый кодовый вход 5, второй делитель 6 частоты с переменным коэффициентом деления, второй кодовый цифроаналоговый преобразователь 11, второй счетчик 12 импульсов, второй цифроаналоговый преобразователь 13, первый 14 и второй 15 фильтры нижних частот, первый

16 и второй 17 элементы И; элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 18, первый 19 и второй

20 триггеры, элемент И-НЕ 21 и третий элемент И 22, Блок 10 элементов И (фиг. 2) содержит К информационных каналов. Младшие (К-1) каналов включают в себя элементы И 23, а старший К-й канал содержит последовательно соединенные элементы HE 24 и ИНЕ 25.

Цифровой синтезатор частот работает следующим образом.

Коэффициенты М и N, поступающие соответственно по кодовым входам 5 и 7 синтезатора частот, в соответствии с принципами ФАПЧ обеспечивают установку частот выходного сигнала управляемого генератора 2 согласно выражению

М

fó.г. = д то.r., где 1о.г — частота опорного генератора 1;

f>.r — частота управляемого генератора

2;

М, N — коэффициенты деления соответственно первого 4 и второго 6 делителей частоты с переменными коэффициентами деления.

Выбор коэффициентов деления основан на использовании алгоритма Евклида, представляющего любое рациоцнальное число в виде конечной ценной дроби.

Последовательное соединение второго счетчика 12 импульсов и регистра 9 хранения образует цифровой фазовый дегектор.

Под воздействием счетных импульсов, поступающих на счетный Т-вход второго счетчика

12 импульсов, опорных импульсов, поступа4г. ющих с частотой топ - нэ С"вход записи

N параллельного кода второго счетчика 12 ìй пульсов и двоичного инверсного кода 2 поступающего на О-входы второго счетчика

12 импульсов, на его выходе формируется двоичный код, величина которого меняется по пилообразному закону в пределах от—

2

N до — .

Частота пилообразного изменения кода на выходе второго счетчика 12 импульсов определяется частотой опорных импульсов топ.

Под воздействием импульсов управляемого генератора 2, поступающих через первый делитель 4 частоты с. переменным коэффициентом деления на С-вход записи параллельного кода регистра 9 хранения, на его выходе формируется двоичный код, пропорциональный разности фаз опорных импульсов и импульсов управляемого генератора.

В режиме синхронизма двоичный код, поступая с выхода регистра 9 хранения через открытый блок 10 элементов И, второй цифроаналоговый преобразователь 13 и первый фильтр 14.нижних частот, поддерживает постоянную величину управляюще-: го напряжения . на первом входе

5 управляемого генератора 2.

При переключении с одной частоты на

f г. другую(например, когда 4г < M ) разность фаз опорных импульсов и импульсов управляемого генератора 2. прошедших через . первый делитель 4 частоты с переменным коэффициентом деления, убывает от цикла к циклу в направлении от 2 л до О. Одновременно уменьшается от цикла к циклу ве. личина двоичного кода на выходе регистра

9 хранения и, следовательно. уменьшается напряжение на выходе первого фильтра 14 нижних час"от 14, вызывая уменьшение частоты управляемого генератора 2. Если полоса захвата . системы фазовой автоподстройки оказывается меньше полосы удержания. то разность фаз опорных им.пульсов и импульсов управляемого генератора 2 скачком изменится от 0 до 2 л.

8 этот момент происходит переключение старшего К-го разряда регистра 9 хранения из "0" в "1" и "1" с выхода элемента ИСКЛЮЧАЮЩЕЕЕ ИЛИ 18 переписывается в первый триггер 19.

1746531

15

25

40

Включается режим сравнения частот.

ka прямом выходе первого триггера 19 появляется "1", а ма инверсном выходе — "0".

Нулевой уровень инверсного выхода оервого триггера 19 запирает второй элемент И

17 и формирует "0" на выходе-третьего элемента И 22, который, поступая ма управляющий вход блока 10 элементов И, осуществляет устамовку нулевого напряже-. ния на -выходе второго цифроаналогового преобразователя 13, соответствующего середине фазовой характеристики детектора.

: Установка нулевого напряжения осуществляется путем формирования "0" нв младших (К-1) выходах и ."1" на старшем К-м выходе блока 10 элементов И.

Единичный уровень прямого выхода первого триггера 19, поступая на вход вычитания первого счетчика 8 импульсов, вызывает изменение его выходного кода и, следовательмо, изменение управляющего напряжения ма втором входе управляемого генератора 2 с максимальной скоростью,определяемой частотой сигмала генератора 1 опорной частоты, Под воздействием измемяющегося управляющего напряжения происходит перестройка частоты управляемого генератора 2 в сторону уменьшения частотной расстройки, что вначале вызывает уменьшение скорости изменения разности фаэ опорных импульсов и импульсов управ-. ляемого генератора, а затем, после изменения направления скорости разности фаз, . происходит ее увеличение в направлении от

Одо 2ж

Когда разность фаз опорных импульсов и импульсов управляемого генератора станет равной л; произойдет переключение старшего К-го разряда регистра 9 хранения иэ "0" в "1" и "0" с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 18 переписывается в первый триггер 19. На прямом выходе первого триггера 19 появляется "О", а на инверсном выходе — "1".

Нулевой уровень прямого выхода первого триггера 19, поступая ма вход вычитания первого счетчика 8 импульсов, осуществляет фиксацию его выходного кода и, следовательно, прекращает изменение управляющего напряжения на втором входе управляемого генератора 2. Выключается режим сравнения частот. Единичный уровень инверсного выхода первого триггера

19 открывает второй элемент И 17 и формирует "1" на выходе третьего элемента И 22, с помощью которой замыкается кольцо

ФАПЧ и осуществляется захват в середине характеристики фазового детектора.

Аналогичным образом происходит переключение с одной частоты ма другую (наf r. пример, при f«> ). В этом случае разность фаз oflopHblx импульсов и импульсов управляемого гемератора 2. прошедших через первый делитель 4 частоты с перемемным коэффициентом деления,.возрастает от цикла к циклу в направлении от О до 2K При скачкообразном иэмемении раэмости фаз опорных импульсов и импульсов управляемого генератора 2 от 2 х до 0 срабатывает второй триггер 20 эа счет переключения имверсмого выхода старшего К го разряда регистра 9. хранения иэ."0" в "1", Синтезатор переходит в режим.сравнения частот. На прямом выходе второго триггера 20 появляется "1", а ма инверсном выходе — "0". Нулевой уровень инверсного выхода второго триггера 20 запирает первый элемент И 16 и формирует "0" ма выходе третьего элемемта И 22. который, поступая ма управляющий вход блока 10 элементов И, осуществляет установку нулевого напряжения ма выходе второго цифроамалогового преобразователя 13, соответствующего середиме фазовой характеристики детектора.

Единичный уровень прямого выхода второго триггера 20, поступая ма вход сложения первого счетчика 8 импульсов, выэывает изменение его выходмого .кода и, следовательно, изменение управляющего напряжения на втором входе управляемого генератора 2 с максимальной скоростью, определяемой частотой сигнала генератора

1 опорной частоты, Под воздействием изменяющегося напряжения происходит перестройка частоты управляемого генератора 2 в сторону уменьшения частотной расстройки, что вначале вызывает уменьшение скорости изменения разности фаэ oAopHblx импульсов и импульсов управляемого генератора. а затем, после измемения маправления скорости разности фаэ. происходит ее увеличение в направлении от 2 л до О.

Когда разность фаз опорных импульсов и импульсов управляемого генератора станет равной апроизойдет переключение имверсмого выхода старшего К-.го разряда регистра 9 хранения из "0" в "1" и "0" с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 18 переписывается во второй триггер 20. На прямом выходе второго триггера 20 появляется "0", а на инверсном выходе — "1". Нулевой уровень прямого выхода второго триггера 20. поступая ма вход сложения первого счетчика 8 импульсов, осуществляет фиксацию его выходного кода и, следова1746531 тельно, прекращзет изменение управляющего напряжения на втором входе.управляемого генератора 2, Выключается режим сравнения частот, Единичный уровень инверсного выхода второго триггера 20 открывает первый элемент И 16 и формирует "1" на выходе. третьего элемента И 22, с помощью которой замыкается кольцо ФАПЧ и осуществляется захват в середине характеристики фазового детектора.

Элемент И-НЕ 21 предотвращает одновременное включение обоих триггеров 19 и 20.

В цифровом синтезаторе частот при сколь угодно узкой полосе пропускания системы полоса захвата равна полосе удержания. При эадзнной полосе пропускания обеспечивается максимальное быстродействие вхождения в синхронизм, поскольку в режиме сравнения частот перестройка частоты управляемого генератора осуществляется с максимальной скоростью, определяемой параметрами системы частотной подстройки, а выключение режима . сравнения частот происходит s тот момент. .когда текущая разность фаз опорных импульсов и импульсов управляемого генератора равна, что соответствует захвату точно в середине фазовой характеристики детектора.

Использование изобретения позволяет получить максимальное быстродействие как в режиме сравнения частот, так и s режиме синхронизма, т.е. эа.минимальное время осуществить переход с одной частоты на другую при высокой спектральной чистоте выходного сигнала, Формула изобретения

Цифровой синтезатор частот. содержащий первый счетчик импульсов, выходы которого. соединены с соответствующими входами первого цифроаналогового преобразователя, последовательно соединенные первый фильтр нижних частот и управляемый генератор. выход которого соединен с выходной шиной, первый делитель частоты с переменным коэффициентом деления, второй счетчик импульсов, счетный вход которого соединен с выходом генератора опорной частоты и тактовым входом второго делителя частоты с переменным коэффициентом деления, отл ич а ю щи и с я тем, что, с целью повышения быстродействия вхождения в синхронизм при одновременном повышении спектральной чистоты выходного сигнала, в него введены

К-разрядный регистр хранения, элемент

ИСКЛЮЧАЮЩЕЕ ИЛИ, первый, второй и третий элементы И, элемент И-НЕ, блок элементов И; второй цифроаналоговый преобразователь, второй фильтр нижних частот, 10 первый триггер и второй триггер, тактовый вход которого соединен с выходом второго элемента И. первый вход которого соединен с инверсным выходом К-го разряда К-разрядного регистра хранения и первым вхо15 дом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с прямым выходом (К-1 -го разряда К-разрядного регистра хранения, выход — с информационными входами первого и второго триггеров, входы

20 сброса которых соединены с выходом элемента И-НЕ, первый и второй входы которого соединены с прямыми выходами соответственно первого и второго триггеров и входами соответственно вычитания и сум25 мирования. первого счетчика импульсов, счетный вход которого соединен с тактовым входом второго делителя частоты с переменным коэффициентом деления, выход и кодовые выходы которого соединены соот30 ветственно с входом записи и информационными входами второго счетчика импульсов, выходы которого через последовательно соединенные К-разрядный регистр хранения, блок элементов И и второй

35 цифроаналоговый преобразователь соединены с входом первого фильтра нижних частот, выход первого цифроаналогового преобразователя через второй фильтр нижних частот соединен с вторым входом управ4р .ляемого генератора. выход которого через первый делитель частоты с переменным коэффициентом деления соединен с входом записи К-разрядного регистра хранения, прямой выход К-ro разряда которого соеди45 нен с первым входом первого элемента И, выход которого соединен с тактовым входом первого триггера, инверсный выход которого соединен с вторым входом второго элемента И и первым входом третьего эле50 мента И. выход которого соединен с управляющим входом блока элементов И, второй вход — с вторым входом первого элемента И и инверсным выходом второго триггера.

1746531

Ю

I ! I . !

Составитель В, Аристов

Редактор Н. Лазоренко Техред М.Моргентал Корректор О. Ципле

Заказ 2403 Тираж Подписное

8НИИПИ Государственного комитета по-изобретениям и открытиям при ГКНТ СССР

113035, Москва. Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина; 101