Мощный интегральный транзистор

Иллюстрации

Показать всеРеферат

Изобретение относится к усилительной технике. Цель изобретения - повышение стабильности и линейности коэффициента усиления по току. В мощном } интегральном транзисторе используются основной 1 и дополнительный 2 транзисторы, дифференциальный 5 и неинвертирующий 6усилители , а также первый 3 и второй 4 резисторы . При этом коллектор и основной эмиттер транзистора 1 являются соответственно коллекторным и эмиттерным выводами устройства , база основного транзистора 1 подключена к выходу усилителя 6, вход которого является базовым выводом устройства и соединен с коллектором транзистора 2, база которого подключена к выходу усилителя 5, основной эмиттер - к основному эмиттеру транзистора 1, дополнительный эмиттер - к инвертирующему входу усилителя 5, неинвертирующий вход которого соединен непосредственно с дополнительным эмиттером транзистора 1 и через резистор 4 с основным эмиттером транзистора 2. Инвертирующий вход усилителя 5 через резистор 4 соединен с основным эмиттером транзистора 1. 1 ил. СП с

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОбРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4808853/09 (22) 02 .04.90 (46) 15.07.92: Бюл. М 26 (71) Институт физйки полупроводников АН

ЛитССР (72) Д.В.Баранаускас, Б.Ю,Юодвалькис,.

В,Н.Иванов и В.В.Иванов (53) 621.375.026(088.8). (56) Авторское свидетельство СССР

N 1307536, кл. Н 03 F 3/26. (54) МОЩНЫЙ ИНТЕГРАЛЬНЫЙ ТРАНЗИ.СТОР

{57) Изобретение относится к усилительной технике. Цель изобретения — повышение стабильности. и линейности коэффициента усиления по току. B мощном 1 интегральном транзисторе используются основной 1 и дополнительный 2 транзисторы, дифференциальный 5 и неинвертирующий бусилиИзобретение относится к микроэлектронике и может быть использовано в мощных интегральных схемах, а также как отдельный транзистор.

Цель изобретения — повышение стабильности и линейности коэффициента усиления по току.

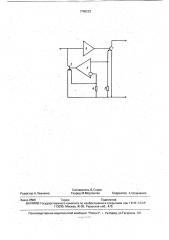

Начертеже представлена принципиальная электрическая схема предлагаемого транзистора.

Мощный интегральный транзистор содержит основной транзистор 1, дополнительный транзистор 2, первый и второй резисторы 3 и 4, дифференциальный и неинвертирующий усилители 5 и 6.

Мощный интегральный транзистор работает следующим образом.

Основной транзистор 1 выполнен с дополнительным эмиттером, дополнительный

„„5U„„1748223 А1

"1,109$

I (J ь -.,,„-". .м . ) тели, а также первый 3 и второй 4 резисторы; При этом коллектор и основной эмиттер транзистора 1 являются соответственно коллекторным и эмиттерным выводами устройства, база основного транзистора 1 подключена к выходу усилителя 6, вход которого является базовым выводом устройства и соединен с коллектором транзистора 2, база которого подключена к выходу усилителя 5, основной эмиттер — к основному эмиттеру транзистора 1; дополнительный эмиттер — к инвертирующему входу усилителя 5, неинвертирующий вход которого соединен непосредственно с дополнительным эмиттером транзистора 1 и .через резистор 4 с ocHQBHbitI4 эмиттером транзистора 2. Инвертирующий вход. усилителя 5 через резистор 4 соединен с основным эмиттером транзистора 1. 1 ил. транзистор 2 также выполнен с дополнительным эмиттером. Входной сигнал через неинвертирующий усилитель 6 поступает на базу основного транзистора 1, при этом в его цепи коллектор — эмиттер протекает ток, который отражается в дополнительном эмиттере, создавая при этом падение напряжения на первом резисторе 3 (URg ), которое поступает на неинвертирующий вход дифференциального усилителя 5 и, будучи усиленным, — на базу дополнительного транзистора 2, отрывая его. Коллекторный ток дополнительного транзистора 2 отражается в цепи его дополнительного эмиттера и создает падение напряжения на втором резисторе 4 (UR4 ). Приняв усилители 5 и 6 за идеальные, из-за отрицательной обратной связи через дополнительный эмиттер дополнительногд транзистора 2 можно счи1748223 тать, что дополнительный транзистор 2 открывается настолько, чтобы падение напряжения UR4 было равно UR . При этом напряжение UR иэ-за отрицательной обратной связи через коллектор дополнительного транзистора 2 устанавливается такой величины, чтобы коллекторный ток этого транзистора был равен току, поступающему на вход устройства. Тогда для устройства в целом можно записать:

0б-эо„Uб-эд, = 06-эо - 0б-эдэ, (1)

ГДЕ 0д-эо,, 0б-эо, — НаПРЯжЕНИЯ баэз-ОСНОВной эмиттер основного и дополнительного транзисторов 1 и 2;

Ue-эд,, Ue-эд, — напряжения база-ропоп15 нительный эмиттер основного и дополнительного транзисторов 1 и 2, Выразив соотношение (1) через площади и токи змиттерных переходов, получим

Io 1 Io 2

Pr 1!и 1 N Pr 2 In I N д1 1 . д2 2 (2) где рТ 1, pf z TBMfl8p8турные потенциалыы основного и дополнительного транэисто- 25 ров1 и 2;

1о,, !д — токи основного и дополнительного эмиттеров основного транзистора 1;

1о,, 1д,— токи основного и дополнительного эмиттеров дополнительного транзи- 30 стора 2;

N1, Nz — соотношения площадей основного и дополнительного транзисторов 1 и 2.

Поскольку 1о, равен входному току устройства (lex) и, приняв pr1 = рт2, можно 35 записать:

41 N1

Io1 = вх (3) ! д2 Nz

Для получения большого усиления вы- 4п полним условия N1» 1, Nz» 1, тогда Ioъ живых, где le x — выходной ток устройства.

Приняв во внимание, что 1д, Вз = Iq R4, выражение (3) можно переписать в виде

Ievx = I ex К, (4)

N1 R4

К =(—

Nz Вз

Как видно из выражения (4), выходной ток устройства имеет линейную зависимость от входного тока, что обеспечивает, высокую точность усиления.

Формула изобретения

Мощный интегральный транзистор; содержащий основной и дополнительный транзисторы одного типа проводимости, а также первый резистор, о т л и ч а ю щ и.й с я тем, что, с целью повышения стабильности и линейности коэффициента усиления по току, введены дифференциальный и неинвертирующий усилители, а также второй резистор, основной и дополнительный транзисторы выполнены с основным и дополнительным эмиттерами, при этой коллектор и основной эмиттер основного транзистора являются соответственно коллекторным и эмиттерным выводами устройства, база основного транзистора подключена к выходу неинвертирующего усилителя, вход которого является базовым выводом устройства и соединен с коллектором дополнительного транзистора, база которого подключена к выходу дифференциально.о усилителя, основной эмиттер — к основному эмиттеру основного транзистора, дополнительный эмиттер — к инвертирующему входу дифференциального усилителя, неинвертирующий вход которого соединен непосредственно к дополнительным эмиттером основного транзистора и через первый резистор с основным эмиттером дополнительного транзистора, инвертирующий вход дифференциального усилителя через второй резистор соединен с основным эмиттером основного транзистора.

1748223

Составитель B.Ñåðîâ

Техред M.Моргентал

Корректор А.Осауленко

Редактор А.Лежнина

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101

Заказ 2509 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям йри ГКНТ СССР

113035, Москва, Ж-35, Раушская наб,, 4/5