Устройство для умножения комплексных чисел

Иллюстрации

Показать всеРеферат

Устройство относится к области вычислительной техники и позволяет перемножать два комплексных числа. Цель изобретения - сокращение аппаратурных затрат - достигается за счет использования только двух блоков умножения. Устройство для умножения содержит семь регистров 1-7, блок 8 управления, два коммутатора 9, 10, два блока 12, 13 умножения, два блока 13, 14 сложения и два элемента И 15, 16. Особенностью устройства является отсутствие преобразователей кода при приеме и выдаче данных на входах и вьГходах устройства. Сомножители подаются на входы устройства в последовательном коде. 2 ил.

союз советских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (si>s G 06 F 7/52

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4847476/24 (22) 02.07.90 (46) 30.07.92, Бюл. ¹ 28 . (71) Одесский политехнический институт (72) А. В. Дрозд, Е. Л. Полин. И. В, Егорова и Ю. А, Дрозд (56) Авторское свидетельство СССР

¹ 1388851, кл, G 06 F 7/49, 1986.

Каляев А. В, Многопроцессорные системы с программируемой архитектурой, M.:

Радио и связь, 1984. с. 182, рис, 5;36. (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ КОМПЛЕКСНЫХ ЧИСЕЛ (57) Устройство относится к области вычислительной техники и позволяет перемно„„. Ж „„1 751748 А1 жать два комплексных числа. Цель изобретения — сокращение аппаратурных затрат— достигается за счет использования только двух блоков умножения, Устройство для умножения содержит семь регистров 1-7, блок

8 управления, два коммутатора 9; 10, два блока 12, 13 умножения, два блока 13, 14 сложения и два элемента И 15, 16. Особенностью устройства является отсутствие преобразователей кода при приеме и выдаче данных на входах и выходах устроиства. Сомножители подаются на входы устройства в последовательном коде, 2 ил.

1751748

Изобретение относится к вычислительной технике и может быть использовано в цифровых устройствах для выполнения операции умножения комплексных чисел.

Цель изобретения — сокращение аппа- 5 ратурных затрат.

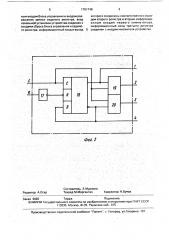

На фиг. 1 приведена функциональная схема устройства; на фиг, 2 — функциональная схема блока управления.

Устройство дпя умножения (фиг, 1) со- 10 держит регистры 1 — 7, блок 8 управления, коммутаторы 9 и 10; блоки 11 и 12 умножения, блоки 13 и 14 сложения. элементы И 15 и 16.

Блок управления (фиг. 2) образуют эле- 15 мент HE 17, триггер 18 и элементы И 19 и

Устройство работает следующим образом, . В начальный момент времени на.вход 20 начальной установки устройства приходит сигнал, устанавливающий устройство в исходное состояние, т.е. обнуляет все регистры множимого и множителя и триггер.в блоке 8 управления. 25

После начальной установки на входы множимого Р и множителя V устройства параллельно поступают соответственно множимое и множитель; причем сначала йх действительные части, а затем мнимые. Под 30 действием тактовых импульсов они продвигаются по соответствующим цепочкам регистров множимого и множителя, Таким образом, в начальный момент времени под действием тактового импульса в первые ре- 35 гистры множимого и множителя записываются действительные части Р1 и V>,. соответственно множимого и множителя.

Со следующим тактовым импульсом они продвигаются во вторые регистры и. т, д., а 40 в первые с этим же тактовым импульсом записываются мнимые части jb u Vz соответственно множимого и множителя.

В первом блока 11 умножения перемножаются сначала действительные, а затем 45 мнимые части множимого и множителя.

Одновременно с мнимыми частями во втором блоке 12 умножения начинают перемножаться действительная часть V j ìíoæèтеля и мнимая часть Д, множимого, а в 50 следующем такте — действительная часть р1 множимого и мнимая часть Vz множителя.

Таким образом, с выхода первого блока

11 умножения на вход первого блока 13 сложения поступают составляющие дейст- 55 вительной части результата Р1 Ч1 и jb

Vz, с выхоДа второго блока 12 умножения на вход второго блока 14 сложения поступают составляющие мнимой части результата

/4 V1 и /3) V2. Через второй коммутатор 10 на выход устройства выдается результат в виде последовательности действительной и мнимой частей, Управляет работой устройства блок 8 управления, который вырабатывает управляющие сигналы для коммутаторов 9 и 10 элементов И 15 и 16.

Формула изобретения

Устройство для умножения комплексных чисел, содержащее первый и второй блоки. умножения, первый и второй блоки сложения и с первого по шестой регистры, входы разрешения записи которых соединены с тактовым входом устройства, вход начальной установки которого соединен с входами сброса первого. второго. третьего и четвертого регистров, выходы первого и второго блоков умнбжения соединены соответственно с первыми входами первого и второго блоков сложения. о т л и ч а ю щ е ес я тем, что, с целью сокращения аппаратурных затрат, в него введены седьмой регистр, два коммутатора, блок управления и два элемента И, выходы которых соединены соответственно с вторыми входами первого и второго блоков сложения, вход множимого устройства соединен с,информационным входом первого регистра. выход которого соединен с информационным входом второго регистра, первым информационным входом первого коммутатора и первым входом первого блока умножения, второй вход которого соединен с выходом третьего регистра и информационным входом четвертого регистра, выход которого соединен с первым входом второго блока умножения, второй вход которого соединен с выходом первого коммутатора, управляющий вход которого соединен с первым выходом блока управления, управляющим входом второго коммутатора и первым входом первого элемента И, второй вход которого соединен с выходом пятого регистра, информационный вход которого соединен с инверсным выходом первого блока сложения и первым информационным входом второго коммутатора, второй информационный вход которого соединен с выходом второго блока сложения и информационным входом шестого регистра, выход которого соединен с первым входом второго элемента И. входы сброса пятого и шестого регистров соединены соответственно с вторым и третьим выходами блока управления, четвертый выход которого соединен с вторым входом второго элемента И, выход второго коммутатора соединен с выходом результата устройства, тактовый вход которого соединен с такто1751748

Составитель Е.Мурзина

Техред M.Mîðãåíòàë Корректор Н.Бучок

Редактор А,Огар

Заказ 2б92 Тираж . Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 вым входом блока управления и входом разрешения записи седьмого регистра. вход начальной установки устройства соединен с входами сброса блока управления и седьмого регистра, информационный вход и выход которого соединены соответственно с выходом второго регистра и вторым информационным входом первого коммутатора, информационный вход третьего регистра

5 соединен с входом множителя устройства,