Устройство для адресации памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для выбора корпуса большой интегральной схемы модуля репрограммируемой памяти и формирования адреса символа применительно к этому корпусу по номеру инструкции или текста, хранящихся в этом модуле Целью изобретения является расширение функциональных возможностей устройства за счет преобразования номера инструкции в требуемый номер корпуса памяти и адрес в рамках корпуса. Цель достигается тем, что в устройство, содержащее первый ждущий генератор, элемент ИЛИ и первый цифровой двоичный счетчик, введены два регистра, четыре двоичных счетчика, две схемы сравнения, два элемента И и второй ждущий генератор 2 ил. СО С

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (s1) s G 06 F 12/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (Л (лЭ фь.

1 о (21) 4794727/24 (22) 21.02.90 (46) 07.08.92. Бюл. N. 29 (71) Севастопольский приборостроительный институт (78) В.С,Говоров, В;К.Маригодов, M,Â,Ïóçàнов и С.В.Есин (56) Блок клавиатуры f5BBB-97-006, Комплект эксплуатационных документов ЩЦМ

3,852.024 ЭД. Лермонтов и/я В-2387.

Устройство вывода информации. Электроника МС 6205, Техническое описание и" инструкция по эксплуатации 3,045.008 TO.

Ровно, и/я А-7208, 1980, с. 22-25. (54) УСТРОЙСТВО ДЛЯ АДРЕСАЦИИ ПАМЯТИ (57) Изобретение относится к автоматике и вычислительной технике и может быть исИзобретение относится к области автоматики и вычислительной техники и может .. быть использовано для выбора корпуса большой интегральной схемы модуля репрограммируемой памяти и формировайия адреса символа применительно к этому корпусу по номеру инструкции или текста, хра-"-:— нящихся в этом модуле.

Известно устройство аналогичного на.значения, содержащее селектор-мульти- плексор, тактовый генератор, генератор строба; цифровой двоичный счетчик и дешифратор.

Наиболее близким к предлагаемому является устройство, содержащее ждущий генератор, элемент ИЛИ и двоичный счетчик.

Недостаток этих устройств состоит в том, что для формирования номера большой интегральной схемы (БИС), входящей в мо2 пользовано для выбора корпуса большой интегральной схемы модуля репрограммируемой памяти и формирования адреса символа применительно к этому корпуСу по йомеру инструкции или текста, хранящихся в этом модуле, Целью изобретения является расширение функциональных возможностей устройства за счет преобразования номера инструкции в требуемый номер корпуса памяти и адрес в рамках корпуса, Цель достигается тем, что в устройство, содержащее первый ждущий генератор, элемент ИЛИ и первый цифровой двоичный счетчик, введены два регистра, четыре двоичных счетчика, две схемы сравнения, два элемента И и второй ждущий генератор, 2 ил, дуль реп рограммируемой памяти (ОРЗУ),.и адреса символа применительно к данной

БИС предлагается использование микро процессора, т.е. выполйенйе устройств по принципу гибкой логики, что значительно усложняет и удорожает их, Цель изобретения — расширение функциональных возможностей устройства за счет возможности преобразования номера инструкции в требуемый номер корпуса памяти и адрес в рамках корпуса.

Эта цель достигается тем, что в устройство, содержащее ждущий генератор, элемент ИЛИ и двоичный счетчик, введены два регистра, четыре счетчика, две схемы сравнения, два элемента И, ждущий генератор, причем первый синхровход устройства подключен к синхровходу первого регистра, входам начальной установки счетчиков с

1753476 первого по четвертый и к входу запуска первого ждущего генератора, выход которого подключен к счетному входу четвертого счетчика, выходы которого подключены к выходам адреса символа устройства и к входам первого элемента И, выход которого подключен к входу установки в ноль четвертого счетчика и к счетному входу третьего счетчика, выход которого подключен к выходу номера корпуса памяти устройства, выходы второго счетчика подключены к входам второго элемента И, выход которого подключен к входу установки и в ноль второго счетчика и счетному входу йервого счетчйка, выход которого подключен к первому входу первой схемы сравнения, вход номера инструкции устройства подключен к информационному входу первого регистра. выход которого подключен к второму входу первой схемы сравнения, выход которой подключен к входу индикации завершения определения номера корпуса памяти устройства, второй синхровход устройства подключен к синхровходу второго регистра, входу начальной установки пятого счетчика и к входу запуска второго ждущего генератора, вход номера символа в инструкции устройства подключен к информационному входу второго регистра, выход которого подключен к первому входу второй схемы сравнения, выход которой подключен к выходу индикации завершения формирования адреса устройства и к входу останова второго ждущего генератора, выход которого подключен к второму входу элемента ИЛИ и счетному входу пятого счетчика, выход которого подключен к второму входу второй схемы сравнения.

Сущность изобретения состбит в том, что устройство, выполненное по принципу жесткой логики, позволяет управлять модулем репрограммируемой памяти без усложнения структуры устройства при любом количестве инструкций, которые хранятся в модуле РПЗУ с целью их отображения и с возможностью замены БИС РПЗУ кодов устаревщйх символов.

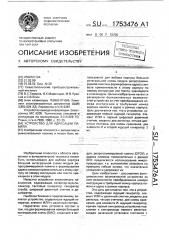

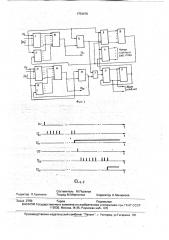

На фиг. 1 дана структурная схема устройства; на фиг. 2 — эпюры сигналов, поясняющие работу устройства.

На схеме обозначены первый 1 регистр, первый 2, второй 3, третий 4 и четвертый 5 цифровые двоичные счетчики, первый ждущий генератор 6, элемент ИЛИ 7, первый 8 и второй 9 элементы И, первый блок 10 сравнения, второй регистр11, пятый цифровой двоичный счетчик 12, второй ждущий генератор 13 и второй цифровой блок 14 сравнения.

Устройство (фиг. 1) работает в .следующей последовательности.

Сигнал U< (фиг. 2), поступающий от МПИ по первому управляющему входу устройст-.

5 ва, подводится к управляющему входу первого регистра 1 и первому входу первого 2, второго 3 и третьего 4 цифровых двоичных счетчиков, а также к первому входу четвертого цифрового двоичного счетчика 5. Под

10 воздействием этого сигнала в счетчик 2 засылается единица, а счетчики 3 — 5 устанавливаются в нуль. Под воздействием сигнала . U> в регистр 1 по информационным входам засылается номер инструкции (Щ (по пер-.

15 вой группе информационных входов устройства).

Сигнал U< подводится также к первому входу первого ждущего генератора. и запускает его. С выхода генератора 6 снимаются

20 импульсы Uo>, которые поступают на второй (счетный) вход счетчика 3 и через элемент

ИЛИ 7 — на второй (счетный) вход счетчика

5, Выходы счетчика 3 замыкаются на вхо25 ды первого 8 элемента И. Когда содержимое счетчика 3 становится равным Ng, с выхода элемента И 8 снимается сигнал, который подводится к второму(счетному) входу счетчика 2 и увеличивает его содержимое на

30 единицу. Этот же сигнал с выхода элемента

8 подводится к третьему (второму управляющему) входу счетчика 3 и сбрасывает его в нуль.

Импульсы Ug> с выхода генератора 6

55 через элемент ИЛИ 7 подводятся к второму (счетному) входу счетчика 5. Когда его содержимое становится равным N>,йв, с выхода второго элемента И 9 снимается сигнал, который подводится к третьему входу счетчика

5 и сбрасывает его в нуль. Этот же сигнал с выхода элемента 9 подводится к второму (счетному) входу счетчика 4 и увеличивает

его содержимое на единицу.

Рассмотренный процесс продолжается до тех пор, пока содержимое счетчика 2 не станет равным содержимому регистра 1. В этом случае с выхода первого 10 цифрового блока сравнения снимается сигнал Uci, который подводится к второму входу генератора 6 и срывает его генерацию. В результате в счетчике 4 фиксйруется номер корпуса БИС РПЗУ, в котором находится инструкция, номер которой равен (N } и находится в регистре 1. а в счетчике 5 — адрес первого символа в инструкции применительно к данному номеру корпуса БИС

РПЗУ. Выход блока 10 является первым управляющим выходом устройства.

Сигнал Uc> с выхода блока 10 подводится к MAM. Передний фронт этого сигнала 1753476 пускает его. С выхода генератора 13 снима- 15 вертого счетчика, выходы которого подключены к выходам адреса символа устройства и к входам первого элемента И, выход котоются импульсы Ugz, которые подводятся к второму (счетному) входу счетчика 12, Эти рого подключен к входу устайовки в "0" четвертого счетчика и к счетному входу же импульсы Uaz через элемент ИЛИ 7 с выхода генератора 13 поступают на второй (счетный) вход счетчика 5, Этот процесс ripo - 20 третьего счетчика, выход которого подключен к выходу номера корпуса памяти устройства, выходы второго счетчика подключены к входам второго элемента И, выход которого.ïoäêëþ÷åH к входу установки в "0" втородолжается до тех пор, пока содержимое счетчи:.а 12 не станет равным содержимому: регистра 11. 8 этом случае с выхода второго

14 цифрового блока сравнения снимается

25 сигнал Un, который подводится к второму

ro счетчика и счетному входу первого входу генератора 13 и срывает его генера- счетчика, выход которого подключен к перцию. В результате в счетчике 5 фиксируется вому входу первой схемы сравнения, вход адрес символа s данной инструкции, кото- номера инструкции устройства подключен к рая хранится в корпусе БИС РПЗУ, номер которого находится в счетчике 4. Выход блоинформационному входу первого регистра, выход которого подключен к второму входу

30 первой схемы сравнения, выход которой ка 14 является вторым управляющим выходом устройства. Сигнал Ucz поступает к: подключен к входу индикации завершения

МПИиинформируетегообокончаниидан- определения номера корпуса памяти устного процесса. ройства, второй синхровход устройства под35

Если йв = 160, т.е. 10100000 в цифровом ключен к синхровходу -второго регистра, двоичном коде, то элемент 8 представляет входу начальной установки пятого счетчика собой элемент И с двумя входами, на один и к входу запуска второго ждущего генераиз которых замыкается шестой выход счет- тора. вход номера символа в инструкции чика 3, а на второй — восьмой. устройства подключен к информационному

Если йь=160, à N1=51, то ¹N1= 81160, 40 входу второго регйстра; выход которого т.е. 1111111100000 в цифровом двоичном подключен к первому входу второй схемы сравнения, выход которой подключен к выкоде. 8 этом случае элемент 0 представляет ходу индикации завершения формирования. адреса устройства и k вход бстанова вторособой элемент И с восемью входами, которые замыкаются соответственно на шестой — тринадцатый выходы счетчика 5, . 45 го ждущего генератора, выход которого подФ ормула и зоб ре те н и я . ключен к второму входу элемента ИЛИ и .Устройство для адресации памяти, со- счетномувходупятогосчетчика, выходкотодержащее ждущий генератор, элемент ИЛИ рого подключен к второму входу второй схемы сравнения

50 и.двоичный счетчик, о т л и ч а ю щ е е с я тем. что, с целью расширения функциональинформирует МПИ об окончании процесса ных возможностей устройства за счет возпреобразования номера инструкции. От можности преобразования номера инструкМПИ по первому управляющему входу уст-, ции в требуемый номер корпуса памяти и ройства поступает сигнал Uz. который под- адрес в рамках корпуса, в него введены два водится к управляющему входу второго 5. регистра, четыре счетЧйка, две схемы сраврегистра и к первому входу пятого 12 циф- нения, два элемента И, ждущий генератор, рового двоичного счетчика. Под воздействи- причем первый синхровход устройства подем этого сигнала в счетчик 12 засылается ключен к синхровходу первого регистра, единица,. а в регистр 11 по информацион- входам начальной установки счетчиков с ным входам (по второй группе информаци- 10 первого по четвертый и к входу запуска перонных входов устройства) засылается номер ваго ждущего генераТора, . вйход которого символа (Мс) в данной инструкции..-: подключен к счетному входу второго счетчиСигнал Uz подводится также к первому ка и к первому входу элемента ИЛИ, выход входу второго 13 ждущего генератора и за- которого подключен к счетному входу чет1753476

1 ° ° Ь °

,; ШШ

° °

° л

Составитель M,Пузанов

Техред M,Mîðråíòàë Корректор Н,Милюкова

Редактор Л,Гратилло

Заказ 2769 Тираж . Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

- 113035, Москва, Ж-35, Раушская нэб., 4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101