Устройство для приема двоичных сигналов с непрерывной фазовой модуляцией

Иллюстрации

Показать всеРеферат

Изобретение относится к технике передачи и приема информации. Целью изобретения является упрощение устройства. В качестве модулятора предлагается использовать устройства, обеспечивающие непрерывность фазы передаваемого сигнала на всем интервале передачи соотношения. Высокая помехоустойчивость достигается за счет оптимальной посимвольной обработки принимаемого группового сигнала с учетом межсимвольной частотно-фазовой связи. Критерием оптимальности является минимум полной ошибки при приеме двоичных сигналов, 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУ6ЛИК (я)э Н 04 1 27/20

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗО6РЕТЕНИЯМ И ОТКРЫТИЯЧ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Ф л

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4?05057/09 (22) 14.06.89 (46) 07.08.92. Бюл.N. 29 (71) Московский авиационный институт им.

Серго Орджоникидзе и Научно-исследовательский институт точных приборов (72) П.П.Загнетов, А.Н,Ложкин и В,M.Волков (56) Авторское свидетельство СССР

М 1690211, кл. Н 04 1 27/20, 1989. (54) УСТРОЙСТВО ДЛЯ ПРИЕМА ДВОИЧНЫХ СИГНАЛОВ С НЕПРЕРЫВНОЙ ФА. ЗОВОЙ МОДУЛЯЦИЕЙ

Изобретение относится к технике передачи и приема информации, а именно к устройствам приема сигналов C межсимвольной связью.

Цель изобретения — упрощение устройства.

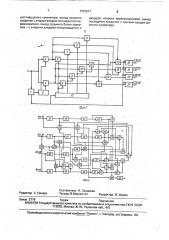

На фиг,1 и 2 изображена. структурная электрическая схема предлагаемого устройства.

Устройство содержит блок 1 фазовой asтоподстройки несущей и тактовой частот, формирователь 2 несущей, первый, второй, третий, седьмой, четвертый, восьмой, пя. тый, девятый, шестой, десятый, перемножители 3 — 12, первый сумматор 13, первый вычитатель 14, второй вычитатель 15, второй сумматор 16, генератор 17 опорных сигналов, первый — четвертый интеграторы 18 — 21, двенадцатый, девятнадцатый, восем- надцатый, двадцатый, двадцать второй, шестнадцатый, одиннадцатый, семнадцатый,,, SU,, 1753617А1

2 (57) Изобретение относится к технике передачи и приема информации. Целью изобретения является упрощение устройства. В качестве модулятора предлагается испольэовать устройства, обеспечивающие непрерывность фазы передаваемого сигнала на всем интервале передачи соотношения. Высокая помехоустойчивость достигается за счет оптимальной посимвольной обработки принимаемого групповоro ñèãíàëa с учетом межсимвольной частотно-фазовой связи.

Критерием оптимальности является минимум полной ошибки при приеме двоичных сигналов, 2 ил. тринадцатый, перемножители 22 — 30, одиннадцатый сумматор 31, четырнадцатый перемножитель32, двадцатый, двадцать первый, пятнадцатый перемножители 33—

35, первый, пятый, девятый, двенадцатый, второй, шестой, десятый, тринадцатый,третий, седьмой. одиннадцатый, шестнадцатый; четырнадцатйй, четвертый, восьмой, семнадцатый, пятнадцатый блоки 36 — 52 задержки, третий, двенадцатйй, десятый, четвертый, тринадцатый, седьмой; восьмой, пятый, шестой, четырнадцатый, шестнадцатый, пятнадцатый, девятый сумматоры 53—

65, решающий блок 66.

Устройство работает следующим образом, На вход устройства поступает аддативная смесь y(t) последова-.ельности сигналов

S (t); J = 1,8 и белого гауссового шума n(t) со спектральной плотностью N<. Сформированная с помощью модулятора последовательность сигналов, Si(k - kt) представk =-1 ляет собой цепь Маркова второго у(г)- g S (r-kT) f п(т);) =1,().

k=1

Поступающий на вход устройства сигнал y(t) переносится на низкую частоту с помощью квадратурного преобразователя, образованного первым и вторым перемножителями, на вторые входы которых поступают опорные квадратурные 84 колебания сов в,д и stn t()

Полученные таким образом квадратурные низкочастотные составля)ощие входного сигнала y(t) поступают на входы перемножителей, на вторые входы которых поступают опорные низкочастотные сигналы с выходов генератора 17 опорных сигналов. Son)(t), t = 1,4, после чего в сумматорах

13 и 16 и блоках 14 и 15 вычитания вычисляются суммй и разности квадратурных составляю цих, опорные сигналы с выходов генератора 17 имеют длительность Т и синхронизированы с помощью блока 1 с началом приема последовательности. На выходе корреляторов, образованных премножите.лями 3 — 12, сумматорами 13 и 16, блоками

14, 15 вычитания и интеграторами I8-21 со сбросом, образу)отся величины, равные логарифму условной вероятности наличия сигнала St(t) = 1,8 в йринимаемой смеси y{t), Поскольку сигналы $!(1) 1 =. 1,8 попарно противоположны, то используются четыре опорных НЧ сигнала.

Правило вынесения решения о знаке принятого информационного символа заключается в сравнении с порогом разности апостериорных вероятностей

inP(Si 1) - fnP(SI 1) 0

При этом апостериорные вероятности определя)отся как

P ($1*(t)) =- {(Р ($1) „+ Р ($8) к-2) Р (»)K-1(! ($1)к-2 + Р{$2)к-2)Р(ЯВ)к-1}Р($1)к

{ (P(S1)K + z+P(S5)K+z)xP(Sf)K+1+{Ð($6}к+2 +

+ ($2) к+2(Р (Я 5) к+1)+{(P ($3) к-2 +

+Р($6)к-2)! ($3)к-1 + (Р($5)к-2 + P(S4)к-2)х хР($6)к-1}Р($3)K{(P($3)K+2 + Р($7)к+1)Р($3)к+1 +

+(Р($4)К+2 + Р($8)К+2)Р(Я7)К+1} + вь(Р($2)К-2 +

+Р($7)к-2)хР(Я4)к- f + (P(S1)K-2 + Р(ЯЩк-2)

Р(Я5)к-1}Р(Я6)к х{(Р(ЯЗ)к+2+ P(Sf)K+2)P($3)K+f +

+(P(S8)K+z + Р($4)к+2)Р($7)к+1) + {(Р($4)к-2 +

+P(S5)K-z)xP(Sz}K-1 + (Р($6) к-2 + Р($3) К-2)Р ($7)к-1}xP(S8)к{(Р($1)к+2 + P {Я5)к+2)Р(Я 1)к +

+(P(S6) к+2 + Р($2) к+2) P(S5) к+1}. i1)

P(Sz*(t)) ={(Р($1) к-2 + P(S8) K-2)P(S5)K-1 (Р($) - Р($1) -z)P($4)K-1} P(Sz) к{(Р($ 1) K+z

+P(S5)K+zJP(S8)к+1 + (P ($2)к+2 +

+PCS6)K+zJP(S4)к+1) + {(P($3)K+z +

Р($6)к-2)Р($7)к-1 + (P(S5)K-2 + P($4)K z)x хР($2)к-1}Р($4)к{(Р($3)к+2 + P($7)K+2)P($6)K+f +.

"(" (- 4)к+2 + Р($8)к+2)Р($2)к+1} + {(Р($1)к-2 +

+Р($8)к-2)ХР($1)к-1 + (P($7)K.2 + P($»Kz)

P(S8)K-1}Р{$5)кх{(Р($3)к+2 + P($7}K.z)P(S6)K+f +

+(Р($8)к+г + Р($4)к+г)хР(Яг}к+1) + (Р($5)к- +

+P(S4)K-2)Р(Я6)к-1 4 (P(S3)K z + Р($6)кр)

P(S3)K 11 ($7)к {(P($1)к+2+ P($5)K+z)xP($8)K+f +

+(P{Sz)K+z + P(S6)K+2lP{S4)K+f j. (2)

Интеграл обработки одного сигнала

S1(t) составляет 5Т, т.е. учитывается значение двух предыдущих и двух последующих за определяемым сигналом.

На выходах блоков 36, 40, 44 и 49 находятся величины, представляющие собой логарифм условной вероятности пР($1)к, наличие сигнала Sf(t) в моменты времени (K -2}T, (К -1)Т, КТ, (К+ 1)Т, (K+ 2)Т аналогично для tnPSz(t); блоки 37, 41, 45 и 50. — для получения величин !пР(Я2)к-2, tnP(Sz)K1, InP(Sz)K, InP($z)K+f, inP(Sz)K+f, блоки 38, 42;

47, 51 — для пОлучвния !пР($5)К-2, tnP(S5)K-1, tnP(S5)K, tnP(S5)K+f, InP(S5)K+z, а блоки 39, 43, 48, 52 — для запоминания !и Р($6)к-2, !Р($6)к-f, InP(S6)K, !пР($6)к+1, InP($6)K+z.

Дальнейшее вычисление организовано по формулам (1) и (2) с учетом их логарифмирования. В результате вычислений на выходе сумматора 64 вычисляется разность логарифмов апостериорных вероятностей принятия сигналов SI(t) и S)(t), Ц = 1,8, соответствующих передачи + 1, которая затем подается на вход решающего блоков, выносящего решение о знаке принятого информационного символа.

Формула изобретения

Устройство для приема двоичных сигналов с непрерывной фазовой модуляцией, содержащее четыре перемножителя, четыре интегратора, генератор опорных сигналов, блок фазовой автоподстройки несущей и тактовой частот, четырнадцать сумматоров, . два вычитателя, четырнадцать блоков задержки и решающий блок, выход которого является выходом устройства, первые входы первого и второго перемножителей и вход блока фазовой автоподстройки несущей и тактовой частот явля)отся входом устройства, первый выход блока фазовой автоподстройки несущей и тактовой частот соединен с входом генератора опорных сигналов,отл ича ю ще е сятем, что, с целью упрощения устройства, введены формирователь несущей, двадцать перемножителей, три блока задержки, причем второй выход блока фазовой автоподстройки несущей и тактовой частот соединен с входом формирователя несущей, первый и второй выходы которого соединены с вторыми входами

1753617 первого и второго перемножителей, выход ro блока задержки — с первыми входами первого перемножителя — с первым входа- шестнадцатого и семнадцатото перемножими третьего-шестого перемножителей, вы- телей, вторые входы которых соединены с ход второго перемножителя соединен с выходом восьмого блока задержки, выход первыми входами седьмого-десятого пере- 5 шестого блока задержки — с вторыми входамножителей, первый выход генератора ми семнадцатого перемножителя и пятого опорных сигналов соединен с вторыми вхо- сумматора, выход которого соединен с пердами третьего и седьмого перемножителей, вым входом десятого сумматора, второй второй — четверть и выходы генератора вход которого и выход соединены соответопорных сигналов соединены соответствен- 10 ственно с выходом тринадцатого перемноно с вторыми входами четвертого и восьмо- жителя и входом одийнадцатого сумматора, го, пятого и девятого, шестого и десятого . второй вход которого и выход соединены перемн жителей, выходы третьего и седь- соответственно с- выходбм четырнадцатого мого перемножителей — с входами первого перемножителям входом двейадцатаго сумсумматора, выходы четвертого и восьмого 15 матора, второй и третий входы которого соперемножителей — с входами первого вычи-. единены соответственйо с выходами тателя, выходы пятого и девятого перемно- третьего и девятого сумматоров, второй жителей — с входами второго сумматора, вход которого соединен с выходом восьмого выходы шестого и десятого перемножите- сумматора, второй вход которого соединен лей — с входами второго вычитателя, выходы 20 с выходом четырнадцатого блока задержки, второго вычитателя, второго сумматора, выход пятого блока задержки — c первыми первого вычитателя и первого сумматора входами восемнадцатого и девятйадцатого соединены с первыми входами соответст- перемножителей; выход двенадцатого певенно первого — четвертого интеграторов, ремножителя — с вторым входом девятйадвторые входы которыхсоединеныс первым 25 цатого и первым входом двадцатого выходом блока фазовой автоподстройки не- перемножителей, вторые входы последнего сущей и тактовой частот, выход первого ин- и восемнадцатого перемножителей соедитегратора соединен с первым входом нены с выходом четвертого сумматора, вытретьего сумматора и через последователь- ход двенадцатого блока задержки — c но соединенные первый — четвертый блоки 30 вторым входом, четвертого сумматора, вызадержки соединены с первым входом ход тринадцатого блока задержки — с перодиннадцатого перемножителя, выход вто- вым входом тринадцатого сумматора, рого интегратора — с первым входом две- второй вход которого и выход соединены н адца то го и ерем н ожител я и через соответственно с выходом двадцатого перепоследовательно соединенные йятый — 35 множителя и третьим входом третьего сумвосьмой блоки задержки с первым входом матора, выход восемнадцатого тринадцатого перемножителя, второй вход перемножителя — с первым входом четыркоторого соединен с выходом одиннадцато- надцатого сумматора, выход которого соего перемножителя; выход третьего интегра-" динен с первым входом" пятнадцатого тора — с первым входом четвертого 40 сумматора, выход которого соединен с вхосумматора и через последовательно соеди- дом решающего блока, выход двенадцатого ненные девятый — одиннадцатый блоки за- сумматора — c вторым входом пятнадцатого держки с первым входом пятого сумматор" сумматора, выход девятнадцатого перемновыход четвертого интегратора — с вторым жителя — с третьим входом восьмогосуммавходом двенадцатого перемножителя и че- 45 тора, выход шестнадцатого блока рез последовательно соединенные двенад- задержки — с вторым входом шест входом шестого сумцатый -пятнадцатый блоки задержки с матора, выход которого соединен с первы. первым входом шестого сумматора, выход ми входами шестнадцатого сумматора и. первого блока задержки соединен с вторым двадцатого перемножителя, второй вход и входом третьего сумматора и первым вхо- 50 выход которого соединены соответственно дом седьмого сумматора; второй вход кото- с выходом семнадцатого перемножителя и рого соединен с выходом десятого блока вторым входом четырнадцатого сумма за е жки мматора, мог д р, а выход — с первым входом вось- выход семнадцатого блока задер о.сумматора и через последовательно третьим входом двадцатого перемножителя соединенные шестнадцатый и семнадцатый 55 и первым входом двадцать первого переблоки задержки, четырнадцатый и пятнад- множителей, второй вход последнего и перцатый перемножители с первым входом де- вый вход двадцать второго перемножителя вятого сумматора, выход третьего блока соединены с выходом шестнадцатого д р соединен с вторым входом один- множителя, выход двадцать первого переперенадцатого перемножителя, выход четверто- множителя с вторым входом

1753617

Q7vz1

Составитель Н. Лазарева

Техред M.Mîðråíòàë Корректор И. Шулла

Редактор С. Пекарь

Заказ 2776 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101 шестнадцатого сумматора, выход которого соединен с вторым входом пятнадцатого перемножителя, выход седьмого блока задержки — с вторыми входами четырнадцатого и

5 двадцать второго перемножителей, выход последнего соединен с третьим входом девятого сумматора.