Устройство для контроля информации

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах управления технологическими процессами и в системах автоматизированного проектирования. Целью изобретения является повышение достоверности контроля. В устройство введены шифратор, два блока сравнения, элемент ИЛИ, три триггера, два элемента И, что обеспечивает предотвращение выдачи устройством неверных результатов контроля, искаженных произвольной записью информации в блоки памяти. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

j (я)5 6 06 Р 11/26

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ I

t, 1!

" 4 :;. :,...;

1р4 б. blip "" ." @,2Фъ ",Ф Ъ 4, «и» ааФ: (21) 4798496/24 (22) 01.03,90 (46) 15.08.92, Бюл. N 30 (71) Московский институт инженеров гражданской авиации (72) С. Ж. Кишенский, Н. С. Вдовиченко, А;

Я. Крекер и О. Ю. Христенко(56) Авторское свидетельство СССР

М 1081637, кл. 0 06 F 3/00, 1984..

Авторское свидетельство СССР

К 1399774, кл. G 06 Е 15/46, 1988. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИНФОРМАЦИИ

Изобретение относится к области автоматике и вычислительной техники и может быть использовано в системах управления технологическими процессами.

Цель изобретения — повышение достоверности контроля.

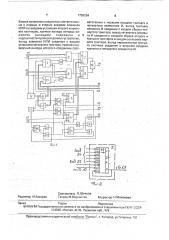

На фиг, 1 приведена структурная схема устройства; на фиг. 2 — структурная схема блока памяти.

Устройство содержит мультиплексор 1, группу 2 блоков памяти, счетчик 3, дешифратор 4, триггер 5, генератор тактовых импульсов 6, элементы 7 и 8 И, мультиплексор

9, группу элементов 10 ИЛИ, счетчики 11 и

12, дешифратор 13, элемент 14 ИСКЛЮЧАЮЩЕЕ ИЛИ, шифратор 15, блоки сравнения

16 и 17, 18, 19, 20, элементы 21 и 22 И, элементы 23 ИЛИ, группы входа контролируемой информации 24 устройства, входы

25 и 26 задания начальных условий устройства, синхровход 27 устройства, вход 28 за„, Ы„„1755284 А1 (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах управления технологическими процессами и в системах автоматизированного проектирования.

Целью изобретения является повышение достоверности контроля. В устройство введены шифратор, два блока сравнения, элемент ИЛИ, три триггера, два элемента И, что обеспечивает предотвращение выдачи устройством неверных результатов контроля, искаженных произвольной записью информации в блоки памяти. 2 ил, дания режима работы устройства, адресные входы 29 устройства, выход 30, контрольный выход устройства, выходы 31 и 32 адресов анализируемых слов устройства, выход 33 кода числа тактов контроля устройства, выходы 34 и 35 индикации.

Устройство работает следующим образом.

В исходном состоянии в блоки памяти 2 записана некоторая начальная информация с входов 24 устройства, Параллельная запись информации во все разряды соответствующего блока памяти осуществляется следующим образом: на входы данных регистра Д1-Д4 подается информация, на вход

V2 подается единичный сигнал, и запись информации в регистр осуществляется фронтом импульса на входе 29 соответствующего блока 2.

В устройстве реализованы два основных режима контроля информации: режим

45 последовательного контроля и режима выборочного контроля. В этих режимах на входах блоков 2 памяти устанавливается нулевой потенциал. После общего сброса и запуска генератора 6 по вхоцу 28 (цепл общего сброса не показаны) через элемен — И

7 на входы выборки дешифраторов 4 и 13 поступают импульсы с генератора 6, которые появляются на выходах дешифратора, соответствующих кодам, содержащимся соответственно в счетчикях 3 и 11. Эти сигнэлы используются в блоках памяти 2 в качестве сдвиговых. Адресные сигналы с выходов счетчиков 3 и i1 поступают так>ке на мультиплексоры 1 и 9, коммутируя HB ux выходы поразрядно информацию с выходов соответствующих блоков памяти; на выходе элемента ИСКЛЮ lAl0LLl,ЕЕ ИЛИ 14 в случае несовпадения значений отдельных рэзрядов сравниваемых слов данных появляются единичные импульсы длитель ностью тактового периода. Одновременно информация с выходэ блока памяти 2 записывается в младший его разряд, обеспечивая неразруша ащее считывание и:",формации из блока памяти, В режиме последовательного контроля осуществляется попарное сравнение содержимого BGGx блоков памяти. После обгцего сброса устройства счетчики 3, 11, l2, триггеры 18, 19 и 20 обнулены,а триггер 5 — в единичном состоянии, Триггер 5 разрешает после запуска устройства прохождение одного импульса с генератора через элемент

И 8 на вход сброса триггера 5 и на счетный вход счетчика 11, инкрементируя Gf о содержимое. Таким образом, обеспечивается содержимое "0" и "1" соответственно счетчиков 3 и 11. Это содержимое определяет адреса информационных слов в первой паре сравниваемых блоков памяти 2.

При переходе три гера 5 в нулсвое состояние элемент И 8 закрывается и открывается элемент И 7, разрешая праха>кдение следующих импульсов с генератора на входы выборки дешифраторов 4 и 13, Начинается этап сравнения двух слов в блоках памяти2. Через К+1 импульс(где К-разрядность слов в блоках памяти 2) счетчик 12 обнуляется и выдается сигнал переполнения, который поступает на вход установки в единицутриггера 5. Элемент И 8 пропускает опять один импульс, инкрементируя содержимое счетчика 11 и вновь устанавливает триггер 5 в нулевое состояние, обеспечивал сравнение следу.ащей пары слов, Таким образом, перебор участвующих в сравнении блоков 2 памяти осуществляется счетчиками 3 и 11. Первоначально эти счетчики находятся соответственно в состояниях "0" и "1 после первого импульса пере-. полнения со счетчика 12 — в состояниях "0" и "2" и т,д., да дости>кения состояний "0" и

"n-I". Затем с выхода переполнения счетчика 11 поступает сигнал, инкрементирующий содержимое счетчика 3 и начинающий новый цикл сравнения — "1" с "0", и т.д. — до "1" с "и-1", Так продолжается до тех пор, пока не произойдет сравнение всех пар блоков памяти 2. При этом на выходах 31 и 32 в л абой момент времени содержатся адреса сравниваемых слов, на выходе 33-номер такта (номер разряда) сравниваемой пары слов, а на контрольном выходе 30 — единичный сигнал в случае несовпадения соответствующего разряда сравниваемых слов.

В режиме выбо„ î÷íîãî контроля счетчика 3 и 11 путем подачи сигнала управления на вход 27 переводятся в режим параллельной звписи, и в них записываются требуемые адреса по входам соответственно 25 и 26. Далее процесс сравнения производится аналогично описанному, Возможен и вывод из устройства некоторой информации в неизменном виде, без сравнения, Для этага необходимо записать в адин из блоков памяти нулевое слово и в режиме выборочного контроля осуществить контроль требуемого слова, сравнивал его с нулевым.

Устройство обеспечивает также запись новой информации в произвольный блок памяти в требуемые MQMGHTbl времени. Если запись информвции в некоторый блок памяти производится в момент времени, когда этот блок не участвует в поразрядном сравнении, искажений результатов контроля не возникает в принципе. Если же зап|лсь производится в блок памяти, участвующий в данный момент времени в сравнении, устранение искажений результатов контроля в устройстве осуществляется следующим образом.

Запись новой информации в некоторый блок памяти 2 производится путем установки нового слова на входах Д1-Д4/Дк при

К-разрядных слов данного блока указанным. При этом сигнал с входа 29 устройства поступает также на соответствующий вход шифратора 15, преобразующего позиционный код на входах в выходной двоичный код, Этот двоичный код представляет собой адрес блока 2 памяти, в который в данный момент записывается информация. Этот адрес сравнивается в блоках сравнения 16 и

17 с адресами блоков, участвующих в контроле в момент записи и формируемых соответственно счетчиками 3 и 11. Если он не совпадает ни с одним из двух адресов, искажения информации (результатов) произойти

1755284 не может, и при данной ситуации работа венно с группами адресных входов первого устройства не отличается от описанной, Ес- и второго мультиплексоров и группами ин ли же адрес с выхода шифратора 15 совпа- формационных входов первого и второгодедает с одним из адресов — в счетчике 3 или шифраторов, группы

11, результаты контроля данной пары слов 5 контролируемой информации устройства удутневерными,так какe результатезапи- соединены соответственно с группами инси новой информации сравнение данной па- формационных входов соответствующих ры частично произведется со старым блоков памяти, входы синхронизации котословом, а частично — с новым. При этом рых соединены соответственно с выходами появляется положительный сигнал с выхода 10 соответствующих элементов- ИЛИ группы, авно" соответствующего блока сравне- первые и вторые входы котор ния или, устанавливающий в единич- с выходами первого и второго дешифратоное состояние соответственно триггеры 19 ров, стробирующие входы которых соединеи 20, сигнализируя о том, что данный этап ны с выходом первого элемента И, вхо ы сравнения содержит неверный результат, и, 15 управления записью блоков памяти группы кроме того, указывая какой конкретно блок соединены с групйой адресных входов запамяти изменил содержимое в результате . писью устройства, выход i-ro блока группы записи новой информации, блоков памяти, (где = 1-п, n — число слов в

Одновременносигнал "Равно" поступа- контролируемой информации) соединен с ет через элемент ИЛИ 23 на вход установки 20 одноименными информационными входами триггера 18, который закрывает элемент И первого и второго мультиплексоров, выходы

22 и открывает элемент И 21, При этом сфор- которых соединены с первым и вторым вхомированный вдальнейшем сигнал перепал- дами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вынения с выхода счетчика 12 сбрасывает в ход которого является контрольным нулевой состояние триггер 18, но не уста- 25 выходом устройства, синхровход устройстнавливает триггер 5, запрещая инкременти- ва соединен с синхровходами первого и вторование счетчика 11. Таким образом, этап рого счетчиков, суммирующий вход первого контроля, в котором получен неверный ре- счетчика соединен с выходом переполнения зультат из-за записи новой информации в второго счетчика, вход задания один из блоков памяти, повторяется. 30 р е ж и.м а р.а б о т ы у с т р о и с тУстройство позволяет реализовать по- ва соединен с входом запуска генератор следовательный и выборочный режимы ра- тактовых импульсов, выход которого соедиботы контроля информации и режим ненсо счетным входом третьегосчетчика,с непосредственного вывода данных. При первыми входами первого и второго элеэтом в устройстве предотвращается выдача 35 ментов И, разрядные выходы третьего счетпользователю неверных результатов конт- чика являются выходами кода числа тактов роля, искажЕнных произвольной записью контроляустройства,выходвторогоэлеменинформации в блоки памяти, обеспечиваю- та И соединен с входом суммирования втощей, в свою очередь, отсутствие процессов рого счетчика и с входом сброса первого старения информации вследствие ceoespe- 40 триггера, прямой и инверсный выходы котоменной записи новых данных практически рого соединены соответственно с вторыми без задержки в соответствующие блоки па- входами второго и первого элемента И, мяти, группы информационных входов первого и

Сигналы о нарушении процесса контра- второго счетчиков являются первой и втоля поддерживаются до тех пор, пока поль- 45 рой группами входов задания начальныхусзователю не будет выдан результат ловий,устройства, отличающееся тем, (корректный) сравнения содержимого дан- что, с целью повышения достоверности конной пары блоков памяти; эти сигналы сни- троля, в него введены шифратор, два блока маются одновременно с установкой всравнения,,элемент ИЛИ, три триггера, два единичное состояние триггера 5. 50 элемента И, причем группа адресных входов устройства соединена с группой инфорФ ор мул а и зоб р ете н и я мационных входов шифратора, группа устройство для контроля информации, выходов которого соединена с первыми содержащее два дешифратора, группу эле- группами входов первого и второго блоков ментов ИЛИ г пп группу блоков памяти, два 55 сравнения, вторые группы. входов которых мультиплексора, три счетчика, два элемента соединены соответственно с группами выИСКЛ ЮЧАЮ Е

И, генератор тактовых импульсов, элемент ходов первого и второго счетчиков, являюЮЩЕЕ ИЛИ, первый триггер, щихся соответственно выходами адреса причем группы разрядных выходов первого первого и второго анализируемых слов усти второго счетчиков соединены соответст- ройства, выходы "Равно" первого и второго

Составитель B,Шиянов

Техред М.Моргентал Корректор H.Mèëþêîâà

Редактор И,Касарда

Заказ Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 блоков сравнения соединены соответственно с, первым и вторым входами элемента

ИЛИ и с входами установки второго и третьего триггеров, прямые выходы которых являются выходами индикации о 5 корректности проверки данных устройства, выход элемента .ИЛИ соединен с входом установки четвертого триггера, прямой и инверсный выходы которого соединены соответственно с первыми входами третьего и четвертого элементов И, выход третьего элемента И соединен с входом сброса четвертого триггера, выход четвертого элемента И соединен с входами сброса второго и третьего триггеров и входом установки первого триггера, выход переполнения третьего счетчика соединен с вторь:ми входами третьего и четвертого элементов И.