Интегральная схема

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровым интегральным схемам на основе комплементарных МОП-транзисторов. Изобретение позволяет повысить степень интеграции и устойчивость к -защелкиванию интегральных схем, содержащих комплементарные МОП-транзисторы и биполярные п-р-птранзисторы. В предложенной интегральной схеме повышение степени интеграции и устойчивости к защелкиванию достигается формированием общего скрытого слоя второго типа проводимости, соединенного с шиной питания с помощью одной дополнительной области второго типа проводимости , для р-канального МОП-транзистора, первого n-p-n-транзистора, резистора, и формированием общего скрытого слоя первого типа проводимости, соединенного с общей шиной с помощью дополнительной области первого типа проводимости для рканальных МОП -транзисторов и за счет мзоляции элементов диэлектрическими областями. 3 ил. .

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 Н 01 1 27/04

ГОСУДАРСТВЕ).(НЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНЙЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (21) 4725508/25 (22) 26.07,89 (46) 15,08.92. Бюл. М 30 (72) А,В. Силин, А.И. Белоус и Г.M. Стадник (56) Патент США ЬВ 4651190, кл, Н 01 L 27/10, 1987, Авторское свидетельство СССР

N 1347181, кл. Н 03 К 19/00, 1987.

Электронйка, 1984; Ь 22, с. 23. (54) ИНТЕГРАЛЬНАЯ СХЕМА (57) Изобретение относится к цифровым ин= тегральным схемам на основе комплементарных MOll-транзисторов. Изобретение позволяет повысить степень интеграцйи и устойчивость к защелкиванию интегральных схем, содержащих комплементарнйе

Изобретение относится к полупроводниковой электронике, а более конкретно к полупроводниковым интегральным Схемам на основе комплементарных МОП-транзисторов.

Известна интегральная схема, выполненная на йолупроводниковой подложке и содержащая ячейки, включающие р- и п-канальные МОП-транзисторы, сформированные в полупроводниковых областях и- и р-типов, имеющих геометрию колонок и образующих матрицу.

Недостатком известного устройства является повышение быстродействия при работе на большую нагрузку, связанйое с невысокими выходными токами; обуславливающими резкую зависимость быстродействия комплементарных МОП-ячеек от емкости нагрузки, Указанный недостаток устраняется в интегральной схеме, содержащей ячейки на основе комплементарных МОП-транзйсто,, И„, 1755338 А1

МОП-транзисторы и биполярные n — р-итранзисторы. В предложенной интегральной схеме повышение степени интеграции и устойчивости к защелкиванию достигается формированием общего скрытого слоя второго типа проводимости, соединенного с шиной питания с помощью одной дополнительной области второго типа проводимости, для р-канального МОП-транзистора, первого п-р-п-транзистора, резистора, и формированием общего скрытого слоя первого типа проводимости, соединенного с общей шиной с помощью дополнительной области первого типа проводимости для рканальных МОП транзисторов и за счет изоляции элементов диэлектрическими областями. 3 ил.

1 ров с двухтактным выходом на биполярных и-р-и- транзисторах, которые позволяют увеличить выходные токи перезаряда емкости нагрузки ячейки, уменьшить зависимость быстродействия от емкости нагрузки и увеличить быстродействие интегральной схемы.

Недостатком известного устройства является пониженйая степень интеграции, связанная с необходимостью введения в ячейку дополнительн:.х биполярных п р-итранзисторов, увеличивающих ее площадь.

Наиболее близкой к предлагаемой является интегральная схема, включающая ячейки, содержащие rro-меньшей мере два и-канальных МОП-транзистора, один р-канальный MOll-транзистор, два биполярных и-р — пгранзистора, коллектор одного из которых соединен с шиной питания, один резистор, шины питания, общие шины, Интегральная схема выполнена на полупроводниковой подложке первого типа прово1755338 димости в изолированных диэлектриком полупроводниковых областях со скрытыми слоями первого типа проводимости, в которых сформированы и-канальные МОП-транзисторы, и второго типа проводимости, в которых сформированы р-канальный МОПтра зистор, резистор и биполярные и-р-птранзисторы. На планарной поверхности интегральной схемы сформированы также металлизированные шины питания и общие шины, Недостатком этой схемйявляется пониженная степень интеграции, связанная с увеличением площади ячейки из-за введения в нее дополнительных элементов (и — рп-транзисторов, резистора), а также пониженная устойчивость к защелкиванию, связанная с увеличением броское тока в шинах питания и общих шинах, вызванным увеличением выходных токов ячейки..

Целью изобретения. является повышение степени интеграции известной интегральной схемы путем уменьшения площади, занимаемой ячейкой, и поеыШение устойчивости известной интегральной схемы к защел ки ва нию.

Укаэанная цель достигается тем; что в известной интегральной схеме полупроводниковые области с р-канальным МОП-транзистором, резистором и первым и-р-и-транзистором сформированы над общим скрытым слоем второго типа проводимости, выведенном на планарную поверхность интегральной схемы посредством дополнительной области второго типа проводимости, выполненной под шиной питания и соединенной с ней, а сопротивление области удовлетворяет соотношению

0П скр

R("ИВ—

rye U».« — прямое падение напряжения р-и-перехода сток-карман р-канального

МОП-транзистора; ! Р— ток стока р-канального МОП-транзистора; фд — коэффициент усиления тока базы первого п-р-п-транзистора.

Полупроводниковые области с и-канальными. МОП-транзисторами сформированы под общим скрытым слоем первого типа проводимости, выведенном на пленарную поверхность интегральной тиристорной структуры КМОП элемента, тем самым повышается устойчивость интегральной схемы к защелкиванию.

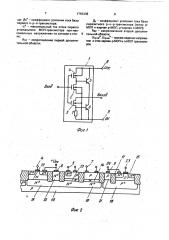

На фиг. 1 изображена электрическая схема ячейки интегральной схемы; на фиг.

2 — активная структура интегральной схемы, поперечный разрез; на фиг. 3 — топалогическая схема активной структуры интегральной схемы, Интегральная схема включает ячейки 1, содержащие по меньшей мере два и-каналь5 ных МОП-транзистора 2 и 3, один р-канальный МОП-транзистор 4, два биполярных и-р-и-транзистора 5 и 6, один резистор 7, шины 8 питания U, общие 9 шины QV (фиг. 1).

10 Интегральная схема (фиг. 2 и 3) выполнена на полупроводниковой подложке 10 первого (р) типа проводимости в изолированных диэлектриком 11 полупроводниковых областях 12-14, 16 и 17. В областях 15

15 и 16 со скрытым слоем первого (р) типа проводимости 18 сформированы и-канальные

МОП-транзисторы 2 и 3, в областях 12-14 со скрытым слоем второго типа проводимости

19 сформированы соответственно р-каналь20 ный МОП-транзистор 4, первый и-р-и-транзистор 5, резистор 7. В области 17 со скрытым слоем второго (n) типа проводимости 20 сформирован второй п-р-и-транзистор 6, На планарной поверхности

25 интегральной схемы сформированы металлизированные шины 8 питания и общие шины 9, В интегральной схеме полупроводниковые области 12-14 с р-канальным МОП-транзистором 4, первым n—

30 р-и-транзистором 5 и резистором 7 сформированы над общим скрытым слоем второго(п+) типа проводимости 19, выведенном на планарную поверхность интегральной схемы посредством дополнительной

35 полупроеоднйковой области 21 второго (и) типа проводимости, выполненной под шиной 8 питания и соединенной с ней, Полупроводниковые области 15 и 16 с и-канальными транзисторами 2 и 3 сформи40 рованы над общим скрытым слоем 18 первого(р+) типа проводимости, выведенном на планарную поверхность интегральной схемы посредством дополнительной полупроводниковой области 22 первого (р+) типа

45 проводимости, размещенной под общей шиной 9 и соединенной с ней.

Формирование общего скрытого слоя

19 второго типа проводимости для полупроводниковых областей р-МОП транзистора 4, 50 резистора 7, первого и-р-и-транзистора 5 позволяет сформировать к нему только одну дополнительную полуп ров одни ко вую область 22 второго типа проводимости вместо трех, но обеспечить выполнение трех функ55 ций: подключить область кармана второго типа проводимости 12 к шине питания, подключить источник питания 8U«к коллектору первого биполярного Il р-и транзистора 5 и создать обратное смешение полупроводниковой области 14 с резистором 7, Такое со1755338

25

35

50 вмещение функций в одной сформулированной области 22 позволяет исключить два контакта к скрытому слою 19 второго типа проводимости, уменьшить площадь, занимаемую ячейкой 1, и повысить степень интеграции интегральной схемы. Так как при этом коллектор первогб и-р-п-транзистора

5 и область кармана 12 р-МОП транзистора подключены с шиной 8 питания через сопротивление Вз дополнительной области 12 второго типа проводимости, которое подключено параллельно переходу база-эмиттер паразитного р-и-р-транзистора тиристорной структуры и через него протекает увеличенный выходной ток заряда емкости нагрузки ячейки, обеспечение выполнение условия

0п ск (2) с PN где U}}p.gK - прямое падение напряжения на переходе сток-ка рман р-МОП транзистора

4;

I<Р— ток стока р-MOll транзистора 4;

pN — коэффициент усиления тока базы первого и-р-и-транзистора 5. не позволит создать на сопротивлении Йз при заряде емкости нагрузки ячейки напряжения, достаточного для отпирания параэитного р-и-р-транзистора и тиристорной структуры, что повышает устойчивость интеграл ьной схемы к защел киванию. При обеспечении условия (2) возможно размещение дополнительной области 22 в любом месте ячейки. При размещении ее под шиной 8 питания площадь ячейки уменьшится на значение площади области 22, что позволяет повысить степень интеграции интегральной схемы, Одновременное размещение областей 15 и 16 и и-канальных

МОП-транзисторов над общим скрытым слоем 18 первого типа проводимости позволяет также сформировать к ней одну дополнительную область 21 для подключения карманов первого типа проводимости и МОП транзисторов 2 и 3 к общей шине 9 вместо двух, а выполнение условия (2)— снять ограничение на значение сопротивления дополнительной области 21, являющей-. ся сопротивлением R< в базе паразитного и-р — и-транзистора тириеторной структуры и разместить ее под общей шиной 9, уменьшив тем самым площадь ячейки, что повышает степень интеграции интегральной схемы. 5

Таким образом, использование изобретения позволяет повысить степень интеграции и повысить устоЙчивость защелкиванию известной интегральной схемы, содержащей комплементарные

МОП-транзисторы и биполярные р-и--ртранзисторы, . Формула изобретения

Интегральная схема, включающая ячейки, содержащие по мейьшей мере первый и второй п-канальные МОП-транзисторы, рканальный MOIL-транзистор, первый и второй биполярные п — р-п-транзисторы, резистор, при этом коллектор первого п-ри-транзистора подключен к шине питания, змиттер — к выходу и коллектору второго транзистора, а база — к стокам р-канального

МОП-транзистора и первого и-канального

МОП-транзистора, исток первого иэ которых подключен к шине питания, исток второго -- к общей шине, а их затворы — к входу ячейки, эмиттер второго и-р-и-транзистора соединен с общей шиной, а база через резистор — с общей шиной и истоком второго и-канального МОП-транзистора. сток,.второго подкл}очен к выходу ячейки, а затвор— к входу ячейки, выполнены на полупроводниковой подложке первого типа проводимости в изолированных областях со скрытыми слоями первого типа проводимости, в которых сформированы п-канальные МОП-транзисторы, и скрытыми слоями второго гипа проводимости, в которых сформированы рканальный МОП-транзистор, резистор и биполярные n — p — n-транзисторы со сформированными на планарной поверхности металлизированными общими шинами и шинами питания, от л и ч а ю щ а я с я тем, что, с целью повышения степени интеграции путем уменьшения площади, занимаемой ячейкой, и повышения устойчивости интегральной схемы к защелкиванию; полупроводниковые области с р-канальным

МОП-транзистором, резистором и первым

n — р — n-транзистором сформированы над общим скрытым слоем второго типа проводимости, имеющим выход на планарную поверхность схемы посредством первой дополнительной полупроводниковой области второго типа проводимости, выполненнол под шиной питания и соединенной с ней, полупроводниковые области с и-канальными MOIL-транзисторами сформированы над общим скрытым слоем первого типа проводимости, имеющим выход на планарную поверхность интегральной схемы посредством второй дополнительной полупроводниковой области первого типа проводимости, размещенной под общей шиной и соединенной с ней, а сопротивления первой и второй дополнительных областей отвечают соотношению (PN !к кк } Pp RS2 < Unp.èê

1755338 где ф " — коэффициент усиления тока базы первого и-р-и-транзистора;

tc — максимальный ток стока первого р-канального МОП-транзистора при максимальных напряжениях на затворе и стоке;

As> — сопротивление первой дополнительной области;

Д> — коэффициент усиления тока базы паразитного р-п-р-транзистора (исток pMOll n-карман р-МОП, р- карман и-МОП);

Rsz — сопротивление второй дополни5 тельной области;

Unp. êp, Unp — прямое падение напряжения и сток карман р-МОП и л-MOfl транзисторов.

1755338

Составитель А. Силин

Текред М.Моргентал

Корректор И, Шулла

Редактор Е. Копча

Производственно-издательский комбинат "Патент", r, Ужгород, ул.Гагарина, 101

Заказ . 2897 Тираж . Ьщписное

ВНИИПЙ Государственного комитета по изобретениям и открытиям при KHT СССР

113035. Москве, Ж-35, Раушская наб., 4/5