Сумматор по переменному модулю

Иллюстрации

Показать всеРеферат

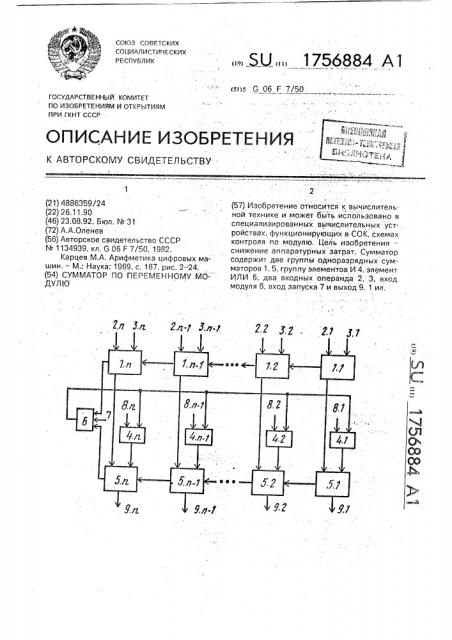

Изобретение относится к вычислитель ной технике и может бьГть использовано в специализированных вычислительных устройствах , функционирующих в СОК, схемах контроля по модулю, Цель изобретения - снижение аппаратурных затрат. Сумматор содержит две группы одноразрядных сумматоров 1, 5, группу элементов И 4, элемент ИЛИ 6, два входных операнда 2, 3, вход модуля 8, вход запуска 7 и выход 9. 1 ил

COIO3 CORF1СКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)с G 06 F 7/50

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

5р мй

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

I (21) 4886359/24. (22) 26,11.90 (46) 23,08.92. Бюл. ¹ 31 (72) А.А.Ол енев

{5G) Авторское свидетельство СССР

N 1134939, кл, 6 06 F 7/50, 1982, Карцев М,А. Арифметика цифровых машин, — M. Наука; 1969, с. 187, рис. 2 — 24, (54) СУММАТОР ПО ПЕРГМЕННОМУ МОДУЛ l0

„„Я3 ÄÄ 1756884 А1 (57) Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных устройствах, функционирующйх в СОК, схемах контроля по модулю. Цель изобретения— снижение аппаратурных затрат. Сумматор содержит две группы одноразрядных сумматоров 1, 5, группу элементов И 4. элемент

ИЛИ 6, два входных операнда 2, 3, вход модуля 8, вход запуска 7.и выход 9, 1 ил.

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных устройствах функционирующих в СОК, схемах контроля па модулю.

Известен сумматор па модулю, содержащий первый и второй узлы формирования обратного кода, блок суммирования, элемент И, формирователь импульсов, триггер, группу элементов И.

Недостатком известного устройства является большое количество оборудования.

Наиболее близким к предлагаемому по технической сущности является одноразрядный сумматор комбинационного типа с переменным основанием и, содержащий 2 группы по п одноразрядных сумматоров, две группы элементов И, группу элементов

ИЛИ, инвертор и элемент ИЛИ, информационными входами операндов являются входы верхнего ряда одноразрядных сумматоров, выходы которых соединены с входами нижней линейки одноразрядных сумматоров, на другой вход которого подается переполнение (";6-и) и со вторыми входами первой группы элементов И, переносы в старший разряд старших разрядов обоих рядов сумматоров являются входами элемента ИЛИ, выход которого через инвертор соединен с первыми входами первой группы элементов И и первыми входами второй группы элементов И, выходы первой и второй групп элементов И являются входами элементов ИЛИ, выход элементов ИЛИ являются выходом устройства, Недостатком известного устройства является большое количество оборудования, .

Целью изобретения является снижение аппаратурных затрат, . Цель достигается тем, что в известном устройстве, содержащем две группы одноразрядных двоичных сумматоров, группу элементов И и элемент ИЛИ, йричем, первые и вторые йнфармационные входы одноразрядных датчиков сумматоров первой группы соединены со входами соответствующих разрядных значений соответственно первого и второго операндов устройства, вход переноса каждого одноразрядного двоичного сумматора первой группы кроме первого, сое, "нен с выходом переноса предыдущего .дноразряднога двоичного сумматора тай же группы, выходы суммы одноразрядных двоичных сумматоров первой группы соединены с первыми информационными входами соответствующих одноразрядных двоичных сумматоров второй группы, выходы суммы которых соединены с выходами результата сумматора. вход переноса каждого одноразрядного двоичного сумматора второй группы, кроме первого соединен с выходом переноса предыдущего одноразрядного сумматора той же группы, выходы переноса последних

5 одноразрядных двоичных сумматоров первой и второй групп соединены соответственно с первым и вторым входами элемента

ИЛИ, выход которого соединен с первыми входами элементов И группы, введены новые

10 связи, вторые входы элементов И группы соединены со входами соответствующих разрядных значений модуля сумматора, а выходы — со вторыми информационными входами соответствующих одноразрядных

15 двоичных сумматоров второй группы, третий вход элемента ИЛИ соединен со входом запуска сумматора, Элемент ИЛИ устройства выполнен трехвходовым.

20 В основу работы предлагаемого устройства положено следующее:

25 где Si — сумма, с4 и Pi — операнды, р,— модул ь (основание).

Возьмем модуль М = 2" (где ri — количество разрядов, необходимых для представления max(pJ, такой что М >.р, тогда выражение (1) можно представить в виде

Sr= I а +/3 +ep,! +, (2) 35 где p =- М -p — код переполнения модуля р, до модуля М, а

0, 1а;+Р; ср, 1, f aj +$3 «р

ai+Pi+p >М, если а +ф «р

rxi+Pi+p <.M, если а;+ф <р, 45

Таким образом, выражений (2) позволяет реализовать на двоиччом и-разрядном сумматоре сумматор по переменному моду лю.

На чертеже пр;;аедена функциональная схема сумматора по переменному модулю.

Сумматор по переменному модулю соДержит первую группу из п-одноразрядных сумматоров 1.1 — 1.п, вторую группу из и

55 одноразрядных сумматоров 5,1-5 и; группу элементов И 4,1 — 4.п, элемент 6 ИЛИ, информационные входы операндов а; и /3; 2,1 — 2.п и 3.1 -З.п, информационный вход кода

Т В ЗТсУм + Тили Ти

I переполнения 8,1 -- 8.п, вход "запуска сум- /1ериод смены кодов oflt .pëHäÎll долме < матора" — 7, выход устройства 9.1 — 9.n. быть равен

Одноразрядные сумматоры 1.1 — 1,n . функционально известные элементы. На входы элементов 1.1 — 1,п подаются инфор- 5 мационные входы операндов а и /3j . Для смены модуля в динамике вычислиЭлементы И 4.1 — 4,п функционально тельного процесса необходимо подать нл известные элементы. На входы этих элемен- входы 8.1 — 8.п новый код переполнения. тов подаются код переполнения 8.1 — 8,п и Преимущества предлагаемого устройвыход элемента 6 ИЛИ. 10 ства следующие. По сравнению с базовым

Элемент 6 ИЛИ функционально извеСт- . объектом удалось снизить аппаратурные заный элемент, на входы его подаются выходы траты на и элементов И и и элементов ИЛИ, переноса в старший разряд старших одно- где и — количество раЗрядов сумматора. Быразрядных сумматоров 1,1 — 1.п и 5.1 — 5..п и стродействие при этом значительно не повход "Запуска сумматора" 7.. 15 низилось, Одноразрядные сумматоры 5.1 — 5.п Преимущество предлагаемого устройфункционально известные элементы. Ha ствадостигается изменением связей между первый вход их подается выход сумматоров кодом переполнения, группой элементов И, 1.1 — 1,п, на второй выход подается выход второй группой сумматоров и элементом группы элементов И 4.1 — 4.п. 20 ИЛИ, введением нового входа "Запуск сумВыходы переноса J-Tblx сумматоров в матора". обеих линеиках подключены ко входу пере- Таким образом, отмеченное преимущеноса 0+1)-го с ммато а, ство выгодно отличает предлагаемое устУстройство работает следующим обра- ройство от базового объекта. зом, 25

Коды операндов al upi поступают с ин- Ф о р м у л а и з о б р е т е н и я формационных входов,2.1 -2.п и 3.1-3.п на входы сумматоров 1,1. — 1.п. Код переполне- Сумматор по переменному модулю, сония 8.1 — 8.п поступает на второй вход эле- держащий две группы одноразрядных двоментов И 4,1 — 4.п. На элемент ИЛИ 6 30 ичных сумматоров, группу элементов И и подается сигнал "Запуск сумматора", кото- элемент ИЛИ, причем первые и вторые инрый открывает прохождение кода перепол- формационные входы одноразрядных двонения через элементы И 4.1 — 4.п на вторые ичных сумматоров первой группы входы сумматоров 5.1 —. 5.п. на первые: вхо-. соединены с входами соответствующих разды которых поступает результат ai+ pl 35 рядных значений соответственно первого и

Код суммы я (лч + +р (через втоРого опеРандов УстРойства, вход пеРевремя переходных процессов в сумматорах носа каждого одноразрядного двигателя

1.1-.1.п и 5,1 — 5.п появится на выходах СУ матоРа пеРВОЙ ГРУппы. КРОме пеРВОГΠ— @+n д Од р и

40 н необходимо сложение с кодом переполне- од оРазРЯдного двоичного сУмматоРа той ния что и.происходит так как элементы И же гРУппы выхолы СУммы ОДНОРазрЯДных

4 1 — 4.п открыт поданйым сигналом "За- Д оичных сУмматоРов пеРвой гРУппы соедипуск сумматора" и возможны переносы из нены с ервыми информаЦио""ь ми в одастаршего разряда 1,п и 5.п сумматоров. Ilo- . ми соответствУющих одноРазРЯдных д ootnsaavvx xсумматоров второи группы. выхо

45 в ич результат суммирования по модулю ф. Ды сУммы котоРых соеДинены с BblxoQBt4M

/ (О то п ерен оса резуль а а сумма ора, вход переноса каждого Одноразрядног двоичного умматор еслисигнал Запусксумматора-„,ть,тона 50,"„ „Р", РУппы Р е пеРвого, соединен с выходе через время перехо ных процессов 50 выхоДом пеРеноса пРеДыДУЩе о ОДнОРазрядного двоичног умматор o ® Руп

Поэтому для обеспечения работоспособности устройс а необходимо, чтобы на вход 7 "Запуска сумматора" подавался сигнал длительностью Т где Т = 2Тсум + Тиди+

55 внн

+ Ти, где Тсум — время переходных процес° где = сУм +или,,ИЛ И g bl>

Составитель А,Оленев

Техред M.Ìoðãåíòàë Корректор Е,Папп

Редактор 0,Хрипта

Заказ 3088 Тираж Подписное

ВНИИПИ Государств нного комитета по изобретениям и открытиям при ГКНТ СССР

113035. Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 щих разрядных значений модуля сумматора, а выходы — c вторыми информационными входами соответствук>щих одноразрядных двоичных сумматоров второй группы, третий вход элемента ИЛИ соединен с входом запуска сумматора.