Пересчетная схема в коде фибоначчи

Иллюстрации

Показать всеРеферат

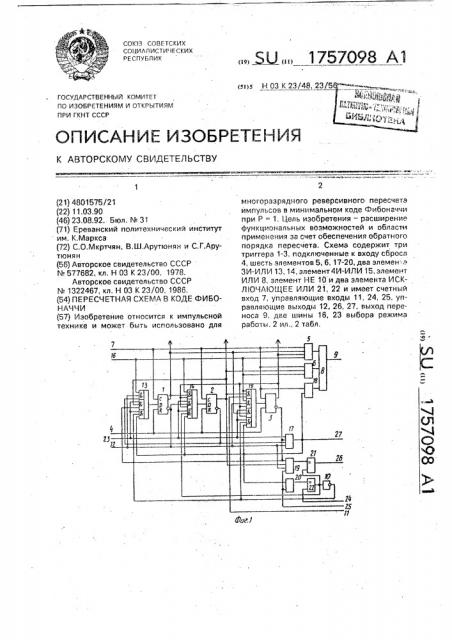

Изобретение относится к импульсной технике и может быть использовано для многоразрядного реверсивного пересчета импульсов в минимальном коде Фибоначчи при Р 1. Цель изобретения - расширение функциональных возможностей и области применения за счет обеспечения обратного порядка пересчета. Схема содержит три триггера 1-3, подключенные к входу сброса 4, шесть элементов 5, 6, 17-20, два элемен Р ЗИ-ИЛИ 13,14,элемент4И-ИЛИ 15, элемент ИЛИ 8, элемент НЕ 10 и два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 21, 22 и имеет счетный вход 7, управляющие входы 11, 24, 25, управляющие выходы 12, 26, 27, выход переноса 9, две шины 16, 23 выбора режима работы.2 мл , 2 табл.

СООЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)л Н ОЗ К 23/48, 23/5

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

15 (21) 4801575/21 (22) 11,03.90 (46) 23.08.92. Бюл. ¹ 31 (71) Ереванский политехнический институт им. К.Маркса (72) С,Î.Мкртчян, В,Ш.Арутюнян и С.Г,Арутюнян (56) Авторское свидетельство СССР

¹ 577682, кл, Н 03 К 23/ОО, 1978, Авторское свидетельство СССР

¹ 1322467, кл. Н 03 К 23/00, 1986. (54) ПЕРЕСЧЕТНАЯ СХЕМА В КОДЕ ФИБОНАЧ IN (57) Изобретение относится к импульсной технике и может быть использовано для

„„БЫ„„1757098 А1 многоразрядного реверсивного пересчета импульсов в минимальном коде Фибоначчи при P = 1, Цель изобретения — расширение функциональных возможностей и области применения за счет обеспечения обратного порядка пересчета. Схема содержит три триггера 1-3, подключенные к входу сброса

4, шесть элементов 5, 6, 17-20, два элемен; э

ЗИ-ИЛИ 13, 14„элемент 4И-ИЛИ 15, элемент

ИЛИ 8, элемент НЕ 10 и два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 21, 22 и имеет счетный вход 7, управляющие входы 11, 24, 25, управляющие выходы 12, 26, 27, выход переноса 9, две шины 16, 23 выбора режима работы. 2 ил., 2 табл, 1757098

)0 t5

Изобретение относится к импульсной технике и может быть использовано для многоразрядного реверсивного пересчета импульсов в минимальном коде Фибоначчи

flpM P = 11.

Известна псресчетная схема в коде Фибоначчи, содержащая в каждом разряде счетный триггер, элементы И и элементы

ИЛИ.

Недостатками этой схемы являются сложность и узкие функциональные возможности, заключающиеся в пересчете только в прямом порядке, Наиболее близким па технической сущности к предлагаемой является пересчетная схема в коде Фибаначчи, содержащая первый, второй и третий триггеры, входы сброса которых объединены и подключены к входу сброса пересчетной схемы, первый и второй элементы И, первые входы которых и синхровхады всех триггеров объединены и подключены к счетному входу пересчетнай схемы, элемент ИЛИ, первый и второй входы которого соединены с выходами соответственно первого и второго элементов И, а выход — с выходом переноса пересчетной схемы, элемент НЕ, первый управлиащий вход и первый управляющий выход, а второй и третий входы первого элемента И подключены соответственно с прямыми выходами первого и третьего триггеров, второй вход второго элемента И вЂ” с прямым выходом второго триггера, Недостатками известной схемы явля атся узкие функциональные возможности и область применения, заключающиеся в пересчете только в прямом порядке.

Цель изобретения — расширение функциональных возможностей и области применения путем обеспечения пересчета также в обратном порядке пересчета, Поставленная цель достигается тем, чта пересчетная схема в коде Фибоначчи, содержащая первый, второй и третий триггеры, входы сброса которых объединены и подключены к входу сброса пересчетнай схемы, первый и второй элементы Л, первые входы которых и синхровходы всех триггеров объединены и подключены к счетному входу пересчетной схемы, элемент ИЛИ, первый и второй входы которого соединены с выходами соответственно первого и второго элементов И, а выход — с выходом переноса пересчетной схемы, элемент НЕ, первый управляющий вход и первый управляющий выход, а второй и третий входы первого элемента И подключены соответственно к прямым выходам первого и третьего триггеров, второй вход второго элемента И вЂ” к прямому выходу второго триггера, дополнительно содержит первый и второй элементы ЗИ-ИЛИ, элемент 4И-ИЛИ, выходы которых соединены с 0-входами соответственно первого, второго и третьего триггеров, первую шину выбора режима работы, соединенную с четвертым входом первого элемента И, с третьим входом второго элемента И, с первыми входами первых структур и первого и второго элементов ЗИ-ИЛИ и с первыми входами первой и второй структур И элемента 4И-ИЛИ, третий, четвертый, пчтый и шестой элементы И, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, вторую шину выбора режима работы, второй и третий управляющие входы, второй и третий управляющие выходы, причем выход третьего элемента И соединен с вторым входом четвертого элемента И, с первым входом шестого элемента И, с третьим управляющим выходам и с третьими входами третьих структур И первого и второго элемента ЗИИЛИ и четвертой структуры И элемента 4ИИЛИ, первый вход четвертого элемента И соединен со счетным входом пересчетной схемы, а выход — с третьим входом элемента

ИЛИ, вторая шина выбора режима работы соединена с первыми входами вторых и третьих структур И первого и второго элементов ЗИ-ИЛИ, третьей и четвертой структуры И элемента 4И-ИЛИ и с первым входом третьего элемента И, инверсный выход первого триггера соединен с четвертым входом третьего элемента И и с третьим входом пятого элемента И, с первым управля ащим выходам и с вторыми входами (первой структуры И второго элемента ЗИ-ИЛИ) вторых структур И второго элемента ЗИ-ИЛИ и элемента 4И-ИЛИ, инверсный выход второго триггера соединен с третьими входами третьего элемента И и первой структуры И первого элемента ЗИ-ИЛИ, а инверсный выход третьего триггера — с вторым входом третьего элемента И, с первым входом пятого элемента И и с третьим входом второй структуры И первого элемента ЗИ-ИЛИ, второй вход пятого элемента И соединен с прямым выходом второго триггера, а выход — с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, четвертый вход пятого элемента И и второй вход шестого элемента И соединены с вторым управляющим входом пересчетной схемы, а первый управляющий вход — с вторым входом второго элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с входом элемента НЕ, с вторым входам третьей структуры И второго элемента ЗИ-ИЛИ и с вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход первого элемента И С КЛ Ю ЧАЮ!ЦЕ Е ИЛ И соединен с первым управляющим выходом

1757098

Х пересчетной схемы, а выход элемента HE— с вторыми входами третьей структуры И первого элемента ЗИ-ИЛИ и четвертой структуры И элемента 4И-ИЛИ, прямой выход первого триггера соединен с вторыми 5 входами первой структуры И второго элемента ЗИ-ИЛИ и третьей структуры И элемента 4И-ИЛИ, прямой выход второго триггера соединен с вторыми входами второй структуры первого элемента ЗИ-ИЛИ, 10 первой структуры И элемента 4И-ИЛИ, прямой выход третьего триггера соединен с третьими входами первой и второй структур

И второго элемента ЗИ-ИЛИ, второй и третьей структур И элемента 4И-ИЛИ, а пер- 15 вый управляющий вход — с третьим входом первой структуры И элемента 4И-ИЛИ, На фиг. 1 представлена функциональная схема при Р = 7; на фиг. 2 — порядок подключения нескольких пересчетных схем 20 для наращивания разрядности, Пересчетная схема в коде Фибоначчи содержит D-триггеры 1-3, шину вход 4 сброса, первый 5 и второй 6 элементы И, счетный вход 7, элемент ИЛИ 8, выход 9 переноса, 25 элемент HE 10; первый управляющий вход

11, первый управляющий выход 12, элементы ЗИ-ИЛИ 13 и 14, элемент 4И-ИЛИ 75, первую шину 16 выбора,режима работы, третий 17, четвертый 18, пятый 19 и шестой 30

20 элементы И, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 21 и 22, вторую 23 шину выбора режима работы, второй 24 и третий 25 управляющие входы, второй 26 и третий 27 управляющие выходы. 35

Для наращивания разрядности общей схемы ряд пересчетных схем обьединяются следующим образом, Выход 9 переноса каждой пересчетной схемы соединяется со счетным входом 7 последующей пересчет- 40 ной схемы первый 12 и второй 26 управляющие выходы — соответственно с первым 11 и вторым 24 управляющими входами предыдущей пересчетной схемы, а третий управляющий выход 27 — с третьим управляющим 45 входом 25 последующего модуля, первый 16 и второй 23 шины выбора режима работы, а также входы 4 сброса обьединяются.

Пересчетная схема функционирует следующим образом. 50

В исходном состоянии D-триггеры 1-3 пересчетной схемы находятся в нулевых состояниях. Для его работы в прямом порядке счета на первую шину 16 выбора режима прикладывается единичный логический 55 потенциал, а на вторую шину 23 выбора режима — нулевой логический потенциал.

На входах первой структуры И первого элемента ЗИ-ИЛИ 13 присутствуют единичнйе логические потенциалы с первой шины 16 выбора режима работы в инверсных выходов первого 1 и второго 2 триггеров, на втором входе первой структуры И второго элемента ЗИ-ИЛИ 14 — нулевой логический потенциал с прямого выхода первого триггера 1, а на вторых входах первой и второй структуры И элемента 4И-ИЛИ 15 — с прямых выходов соответственно второго 2 и третьего 3 триггеров. По поступлении первого тактового импульса на выходе общей схемы, содержащей три пересчетные схемы, устанавливается код 100000000, Перед поступлением второго тактового импульса на выходе элемента ЗИ-ИЛИ 73 присутствует потенциал логического нуля, на выходе элемента ЗИ-ИЛИ 14 — потенциал логической единицы, а на выходе элемента

4И-ИЛИ 15 — потенциал логического нуля, Второй тактовый импульс устанавливает на выходе общей схемы код 010000000, Перед поступлением третьего тактовогЬ импульса на выходах элементов ЗИ-ИЛИ 13 и ЗИ-ИЛИ 14 присутствует потенциал логического нуля, а на выходе элемента 4И-ИЛИ

15 — потенциал логической единицы, так как на первый вход его первой структуры И поступает единичный логический потенциал с первой шины 76 выбора режима работы, на второй вход — с прямого выхода второго триггера 2, а на третий вход — с первого управляющего входа )1. Третий тактовый импульс устанавливает. на выходе общей схемы код 001000000.

Перед поступлением четвертого тактового импульса на выходе элемента ЗИ-ИЛИ 13 присутствует единичный логический потенциал, так как на входы его первой структуры И поступают единичные логические потенциалы с первой шины 16 выбора режима работы и с инверсных выходов первого 1 и второго 2 триггеров.

На выходе элемента ЗИ-ИЛИ 14 присутствует нулевой логический потенциал, так как на третий вход его первой структуры И поступает нулевой логический потенциал с инверсного выхода третьего триггера 3, На выходе элемента ЗИ-ИЛИ 15 присутствует единичный логический потенциал, так как на выходы его второй структуры M поступают единичные логические потенциалы с первой шины 16 выбора режима работы, с инверсного выхода первого триггера .. и с прямого выхода третьего триггера 3. Четвертый тактовый импульс устанавливает на выходе общей схемы код 101000000, Перед поступлением пятого тактового импульса на втором, третьем и четвертом входах первого элемента И 5 первой пересчетной схемы присутствуют единичные логические потенциалы с первой шины 16

1757098

40 выбора режима работы, с прямых выходов первого 1 и третьего 2 триггеров, На выходах элементов ЗИ-ИЛИ 13 и 14 и ЗИ-ИЛИ 15 первой пересчетной схемы присутству ат нулевые логические потенциалы, Пятый тактовый импульс устанавливает на выходе общей схемы код0001000000. так как тактовый импульс проходит через элементы И 5, ИЛИ 8 и выход 9 переноса первой пересчетной схемы и поступает нэ счетный вход 7 второй пересчетной схемы, на выходе элемента ЗИ-ИЛИ t3, в котором перед поступлением пятого тэктавага импульса присутствует единичный логический потенциал, На первом управляющем выходе 12 второй пересчетной схемы и первом управляющем входе 11 первой пересчетнай схемы устанэвливается нулевой логический потенциал. В этом случае происходит изменение порядка пересчета первой пересчетной схемы, Первая пересчетная схема в шестом и седьмом тактах функционирует аналогично первому и второму тактам. В восьмом такте первая пересчетнал схема переходит в нулевое состояние. Т.е. изменение порядка пересчета данной пересчетной схемы в режиме прямого счета происходит в случае изменения состолнил первого триг гера 1,последующей пересчетной схемы, В дальнейшем рабата общей схемы в прямом порядке пересчета аналогична описанному, Для работы общей схемы в режиме обратного порядка пересчета нэ первую шину

16 выбора режима работы прикладывэетсл нулевой логический потенциал, э нэ вторую шину 23 выбора режима работы, нэ второй управляющий вход 25 первой пересчетной схемы, нэ второй 24 и третий 25 управляющие входы третьей пересчетной схемы— единичный логический потенциал, В исходном состоянии О-триггеры I-3 пересчетных схем находятся в нулевых состояниях и на выходе второго элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ 22 и на втором управля ощем выходе

26 третьей пересчетной схемы присутствует нулевой логический потенциал, На выходе второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 22 второй пересчетной схемы и íà его втором управляющем выходе 26 присутствует единичный логический потенциал, э нэ выходе второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 22 первой пересчетной схемы — нулевой логический потенциал. На выходе элемента ЗИИЛИ 13 первой пересчетной схемы да поступления первого тактового импульса присутствует единичный логический потенциал, так кэк на первый, второй и третий входы его третьей структуры поступают единичные логические потенциалы соответственно с второй шины 23 выбора режима работы, с выходэ элемента НЕ 10 и с выхода третьего элемента И 17, нэ входы которого единичные логические потенциалы поступают с инверсных выходов всех триггеров пересчетной схемы, На выходе второго элемента ЗИ-ИЛИ 14 присутствует нулевой логический потенциал, э нэ выходе элемента

4И-ИЛИ 15 — единичный логический потенциал, тэк кэк нэ входах его четвертой структуры И присутствуют единичные логические потенциалы соответственно с второй шины 23 выбора режима работы, с выхода элемента НЕ 10 и с выхода третьего элемента И 17.

Нэ выходах элементов ЗИ-ИЛИ 13 и 4ИИЛИ 15 второй пересчетной схемы присутствуют нулевые логические потенциалы, нэ выходе элемента ЗИ-ИЛИ 14 — единичный логический потенциал, тэк кэк на входах его третьей структуры И присутствуют единичные логические потенциалы соответственно с второй шины 23 выбора режима работы, с выхода второго элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ 22 и с выхода третьего элементэ И 17, Нэ выходах элементов ЗИ-ИЛИ 13 и 14 и

4И-ИЛИ <5 третьей пересчетной схемы присутствуют соответственно единичный, нуле, вой и единичный потенциалы аналогично первой пересчетной схеме, Первый тактавый импульс проходит через элементы И 18 и ИЛИ 8 первого и второго пересчетных схем и устанавливает нэ выходе общей схемы кад101016101. Перед поступлением второго тактового импульса нэ выходах первого 13 и второго 14 элементов ЗИ-ИЛИ первой пересчетиой схемы присутствует нулевой логический потенциал, а на выходе элемента 4И-ИЛИ 15 — единичный логический потенциал, так как нэ выходах его третьей структуры И присутствуют единичные логические потенциалы соответственно с второй шины 23 выбора режима работы, с прямых ВыхОдОВ первого 1 и TpeT68f 0 3 триггеров.

Пересчетная схема в ходе Фибаначчи при прямом и обратном счете представлена втэбл.1 и2, Второй тактовый импульс устэнэвливает на выходе общей схемы кад 001010161

Третий, четвертый и пятый импульсы устанавливают на выходе общей схе иы соатветственно коды 010010161, 166010161 и

000010101, т,е, происходит пересчет импульсон в коде Фибоначчи в обратном порядке, Перед поступлением шестого тактового импульса на первом входе элемента И 18, третьем упрэвляющем выходе 26 и нэ выходе второго элемента И СКЛ ЮЧАЮЩЕ Е ИЛИ

22 первой пересчетной схемы присутствует

1757098

10 входу пересчетной схемы, элемент ИЛИ, первый и второй входы которого соединены с Bb!õîäàìè соответственно первого и вто.рого элементов И, з выход — c выходом пе5 реноса пересчетной схемы, элемент НЕ, первый управляющий вход и первый управляющий выход, второй и третий входы первого элемента Vi подключены соответственно к прямым выходам первого и третьего

10 триггеров, второй вход второго элемента И вЂ” к прямому выхоцу второго триггера, о т л и ч а ю щ а я -., я тем, что, с целью расширения функциональных возмо>кностей и области

- применения за с .ет обеспечения обратного

15 порядка пересчета, дополнительно содержит первый и второй элементы ЗИ-ИЛИ, элемент 4И-ИЛИ, выходы которых соединены с D-входами соответственно первого, . второго и третьего триггеров, первую шину

20 выбора режима работы, соединенную с четвертым входом первого элемента И, с третьим входом второго элемента ЗИ-ИЛИ, с первыми входами первых структур И первого и второго элементов ЗИ-ИЛИ и с первы25 ми входами первой и второй структур И элемента 4И-ИЛИ, третий, четвертый, пятый и шестой элементы И, первый и второй элементы ИСКЛ 10ЧА10ЩЕЕ ИЛИ, вторую шину выбора режима работы, второй и третий уп30 равляющие входы, причем выход третьего элемента И соединен с вторым входом четвертого элемента И, с первым входом шестого элемента И. с третьим управляющим выходом и с третьими входами третьих

35 структур И первого и второго элементов И и четвертой структуры И элемента 4И-ИЛИ, первый вход четвертого элемента И соединен со счетным входом пересчетной схемы, а выход — с третьим входом элемента ИЛИ, 40 вторая шина выбора режима работы соеди- нена с первыми входами вторых и третьих структур И первого и второго элементов ЗИИЛИ, третьей и четвертый структур И эле45

50 единичный логический потенциал, а на втором управляющем входе 24 — нулевой логический потенциал. На третьем управляющем входе 25 второй перес гетной схемы присутствует единичный логический потенциал, Шестой тактовый импульс проходит через элементы И 17, И 18, ИЛИ 8 и выход 9 переноса первой пересчетной схемы и поступает на счетный вход 7 второй пересчетной схемы, и на выходе общей схемы устанавливается код 010100101, Седьмой и восьмой тактовые импульсы устанавливают на выходе общей схемы соответственно коды 100100101 и 000100101..

Перед поступлением девятого тактового импульса на втором управляющем входе

24 и первом входе четвертого элемента И 18 первой пересчетной схемы присутствует единичный логический потенциал.

Девятый тактовый импульс устанавливают на выходе общей схемы код

101000101, С десятого по четырнадцатые такты работы общей схемы аналогичны его работе с первого по пятый такты. Четырнадцатый тактовый импульс устанавливает на выходе общей схемы код 000000101,.

Перед поступлением пятнадцатого тактового импульса на первом 24 и втором 25 управляющих входах второй пересчетной схемы присутствуют единичные логические потенциалы соответственно с второго управляющего выхода 26 третьей пересчетной схемы и с второго управляющего выхода 27 первой пересчетной схемы, а на первом управляющем входе 24 первой пересчетной схемы — нулевой логический. потенциал, Таким образом, пятнадцатый тактовый им пульс устанавливает на выходе общей пересчетной схемы код 010101001, так как тактовый импульс проходит через элементы И 18, ИЛИ 8 и выход 9 переноса первой и второй пересчетных схем и поступает на счетный вход 7 третьей пересчетной схемы.

В дальнейшем функционирование общей пересчетной схемы аналогично описанному, Таким образом, состояние, в которое должна устанавливаться данная пересчетная схема после обнуления, определяется состоянием предыдущего и последующих пересчетных схем.

Формула изобретения

Пересчетная схема в коде Фибоначчи, содержащая первый, второй и третий триг- 5 геры, входы сброса которых обьединены и подключены к входу сброса пересчетной схемы, первый и второй элементы И, первые входы которых и синхровходы всех триггеров объединены и подключены к счетному, мента 4И-ИЛИ и с первым входом третьего элемента И, инверсный выход первого триггера соединен с четвертым входом третьего элемент И и с, третьим входам пятого элемент И, с первым управляющим выходом и с вторыми входами первой структуры И первого элемента ЗИ-ИЛИ и элемента 4И-И ПИ, инверсный выход второго триггера cr, динен с третьими входами третьего элемента

И и первой структуры И -первого элемента

ЗИ-ИЛИ, а и-!версный выход третьего триггера соединен с вторым входом третьего элемента И, с первым входом пятого элемента И и с третьим входом второй структуры И первого элемента ЗИ-ИЛИ, второй вход пятого элемента И соединен с прямым выходом второго триггера, а выход — с пермента ЗИ-ИЛИ и четвертой структуры И weмента 4И-ИЛИ, прямой выход первого триггера соединен с вторыми входами первой структуры И второго элемента ЗИ-ИЛИ и

5 третьей структуры И элемента 4И-ИЛИ, прямой выход второго триггера соединен с вторыми входами второй структуры первого элемента ЗР-ИЛИ и первой структуры И элемента 4И-ИЛИ, прямой выход третьего триг10 гера соединен с третьими входами первой и второй структур И второго элемента ЗИИЛИ, второй и третьей структур И элемента

4И-ИЛИ, а первый управляющий вход — с третьим входом первой структуры И элемен1Ь та 4И-ИЛИ, вым входом первого элемента ИСКЛ(ОЧАЮЩЕЕ ИЛИ, четвертый вход пятого элемента

И и второй вхоц шестого элемента И соединены с вторым управляющим входом пересчетной схемы, а первый управляющий вход — с вторым -входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с входом элемейта НЕ, с вторым входом третьей структуры И второго элемента ЗИИЛИ и с вторым входом первого элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первь!м управляющим выходом пересчетной схемы, а выход элем нта НŠ— с вторыми входами третьей структуры И первого элеТаблива

Прлмой счет

Веса разрядов

Веса разрядов

Такт

Такт

Такт

Беса разрядов

1 2 3 5 8 13 21 34 55

2 3 5 18 13 21 34 55

1 2 3 5 8 13 21 34 55

1 мод 2 и. 3 и

1 м ° 2 м. 3 и. и. Зм

2

4

6

8

:10

11

12

13

14 ! У ! б !

t8

f9

2.1

22

23

24

26 г7

28

29

0О000С

101(000

000.100

190 О 0.1.

01 0010

00101 О

000001

010001

00 t Î01

101001

000101

00101

01 01 01

0!ОООО

0001 О

0 0 0

О 0 О

О 0 0 а О О

О О О

О О О

О О О

0 О 0

О О О

О 0 О

0 О О

О О О а О 0

0 О О

О 0 О

О 0 О

О 0 О

О О О

0 О 0

О 0 О

0 0 О

f О 0

1 О 0

1 0 О

1 0 0

1 О О

1 О О

1 О О а о

1 О О

1 0 0

3t 0!

32 00

33 10

34 Gв

35 10

36 О

37 00

38 1 О

39 О О

40 10

41 01

42 00

43 10

44 01

45 00

46 10

47 00

48 1 О

49 01

50 00

51 10

52 00

53 l;.0

54 0 1

55 00

56 10

57 01

58 00

59 10

60 00

61 10

000 О

ОООО

01 00

0 100

001 0

001 0

001Î

1 О О

0001

0001

0001

1001

001

0101

010f

0101

ОООО

1000 .1000

0100

О О

1 О О

О О

О 1 О

О 1 О

О 1 0

О 1 О

О 1 О

0 1 0

О 1 .О

0 1 О

О 1 0

О 1 0

О I О

О 1 О

О 1 О

О 1 О

О 1 О

О 1 О

О 1 0

О 1 0

О 1 О

О 1 О

О 1.0

О О

О Î 1

О О

О 0 1

0 0 t

О 0 1

О О 1

62 01010

63 ОООО!

64 10001

65 01001

66 00101

67 1010!

68 Оооао

69 10000

70 00100

7г 10!Оо

73 00010

74 10010

75 01010

76 ОООО О

77 10000

78 01000

80!О!00

81 ООО(О

82 10010

83 01010

84 Оооо>

85 10001

86 0!001

87 00101

88 10101

89 00000

90 10000

О О О 1

О О О 1

О. 0 О

О О О 1

О О 0 1

0 О О 1 ! О 0

0 0

О О 1

1 О О 1

1 О 0 1

О О 1

1 О О 1

1 О 0 .

0 1 О 1

О t G 1

О t О

О 1 О 1

О l О 1

0 1 О 1

О 1 О 1

О 1 О 1

О 1 О 1

О 1 О 1

0 1 0 1

О 1 О 1

О 1 О 1

0 О О О .

О О Î О

1757098

Таблица 2

Обратный счет

Такт

Веса р! такf

Такт Веса разрядов зеса,разрядов азрядов

8 13213455

5 8 13 21 34 55

123

813213455

235

1.2 3

1 мод

2 м, 3 и °

1 м

2 м. 3 м

2 3 м °

° ° °

Составитель В. Арутюнян

Техред М.Моргентал Корректор С, Юско

Редактор В, Данко

Заказ 3099 Тираж Подписное

ВНИИПИ Государственного комитета г!о изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

О 000

1 О !

2001

3 О 1 0

100

5 000

6 0 1 0

7 10 О

8 000

8 1 01

10 .О 1 1

010

t2 100

13 ООО!

4 01О

15100

16 О О О!

7 101

18 О О 1

19 01 О

20100

21 000

22 101

23 001

24 01 О

25 1 00

26000 27 0 1 О

28.100

29000

30 101

0 1 0

О l o l 00 ! О О

О О О

1 О 1

1 01

I О

001

О О 1

О О

О О 1

001

О 1 О

О 1 О

О О

1 О О

000

О 0

1 О

1 О

О

1 О

1 О

1 О

1 О

1 О

1 О

1 О

1 0

1 О

О О

О О

О О

О О

О О

О О

О О

О О

О О

О 0

О О

О О

0 О

О О

О О

О О

О О

03100!

32 010

1 34 000

350tо

1 37 000

1 38 101

1 39 .00

40 010

1 41 100

1 42 000

1 43 101

1 44 00!

1 45 010

46 100

1 47 000

l 48 010

1 49 .1 О О ! 50 000

51 101

1 52 001

1 53 010

54 10 0

1. 55 О ОО

57 001

I 58 010

1 59 100

6о Ооо

1 61 01 О

000 О 0

00000 ! О 1 О

1 О 1 0 1

1010!

00101

ОО! 0

001 0

001 О

001 О 1

010 О 1

010 О 1

010 О 1

010 0 1

010 О 1

10001

10001

1 О 0 0

0000!

000 О

000 О 1

00001

000 О 1

D 1 О 1 О

010 1 О

0 l 0 1 0

О 1 О О

100 1 0

1 62 1

1 63 О

1 64 1

1 65 О

О 66 О

О 67

О 68 0

О 69 О

0 70 1

О 71 О

О 72 1

0 73 О

О 74 О

О 75 1

О 76 О

О 77 I

О 78 0

О 79 0

О 80 1

О 81 О

О 8? О

0 83 1

О 84 О

О 85 1

0 86 О

0 87 0

О 88 1

О 89 О

0 90 1

О

1 000

0 01.0

О l 00

ОООО

010!

0101

1001

0001

0001

О 1 О 0

0101

О О

О I О

О 1 О

0 1 0

О 1 О

О 1 О

О 1 О

1 0 О

1 О О

1 О О

О О

1 О 0

1 0 О

1 0 О

1 О О

О О О

О О О

О О О

О О 0

О О О

О О О

О 0 О

О О О

О О О

0 О О

О О О

О О О

О О О

О 1 О

О

О

0

О

О

О

О

0

О

О

О

О

О

О

О

О

О

О

О

О

О

О