Устройство цикловой синхронизации многоканальных систем связи

Иллюстрации

Показать всеРеферат

Изобретение относится к многоканальной связи. Цель изобретения - повышение помехоустойчивости цикловой синхронизации за счет обнаружения и устранения влияния пропусков элементов на стыке двух сигналов на процесс синхронизации. Для этого устройство цикловой синхронизации многоканальных систем связи содержит аналого-цифровой преобразователь (АЦП), решающий блок, задающий генератор, счетчик-шифратор , демультиплексор, регистры, триггер, два элемента И, многовходовый элемент ИЛИ, счетчик-делитель, выходной регистр, группу многовходовых элементов И, элемент ЗАПРЕТ. Сущность изобретения заключается в том, что На основе поразрядного перемножения кодов ошибки синхронизации исправляются случайные пропуски элементов принимаемой последовательности сигналов, независимо от их местоположения , а регулярные воспринимаются как ошибки синхронизации и корректируются, в результате чего уменьшается влияние случайных искажений сигнала на процесс установления цикловой синхронизации ПСС в базе Уолша. 3 ил. 1 табл. (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ РЕСПУБЛИК

„,5U„„1757116 Ai (я)ю H 04 1 7/08, H 04 J 3/06

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ. 1 2 (21) 4799717/09::: аналого-цифровой преобразователь (АЦП), (22) 05,03,90 .:: решающий блок, задающий генератор, счет(46) 23,08.92. Бюл. N 31....чик-шифратор, демультиплексор, регистры; (72) В;И.Корыстин, С.П.Белов, Л.И,Корысти- триггер, два элемента" И, многовходовый . на и Л.Н.Оселедько - элемент ИЛИ, счетчик-делитель, выходной (56) Авторское свидетельство СССР -::: регистр, группу многовходовых элементов

N. 1387859, кл. Н 04 L7/08. Н 04 J 3/06, 1986; И, элемент ЗАПРЕТ. СущноСть изобретения (54) УСТРОЙСТВО ЦИКЛОВОЙ СИНХРО- заключается втом,4онаосновепоразрядНИЗАЦИИ МНОГОКАНАЛЬНЫХ СИСТЕМ ного перемножения кодов ошибкй синхроСВЯЗИ ..:;.: ниэации исправляются случайные пропуски (57) Изобретение относится к многоканаль- элементов принимаемой последовательноной связи. Цель изобретения — повышениЕ сти сигналов, независимо от их местополопомехоустойчивости цикловой синхрониза-" жения, а регулярные воспринимаются как цйи за счет обнаружения и устранения вли- ошибки синхрониаации и корректируются, в яния пройусков элементов на стыке двух результате чего уменьшается влияние слусигналов на процесс синхронизации. Для чайныхискаженийсигналанапроцессустазтого устройство цикловой синхронизацйи новления цикловой синхронизации ПСС s многоканальных систем связи содержит . базе Уолша. 3 ил.. 1 табл. юееА

Изобретение относится к многоканаль- Устройство цикловой синхронизации ной связи и может использоваться в систе- содержит аналого-цифровой преобразовамах многоканальной связи с кодовым тель(ALIJl) 1, решающий блок 2, задающий (Я разделенйемиспользующихсявканалахне- генератор (ЗГ) 3, счетчик-шифратор 4, десущих функций Уолша.. : —, мультиплексор5, регистрыб,трйггер7, пер- в

Целью изобретения является повыше- вый 8 и второй 9 элементы И. д ние помехоустойчивости цикловой синхро- многОвходовый элемент ИЛИ 10, счетчик- О низации за счет обнаружения и устранений делитель 11, выходной регистр 12, группу влияния пропусков элементов настыкедвух . многовходовых элементов И 13 и элемент сйгнзлов на процесс синхронизации, ЗАПРЕТ 14, . .. а

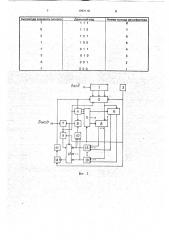

На фиг. 1 представлена функциональная схема устройства цикловой синхрониза-: Решающий блок содержит дешифратор ции многоканальных систем связи; на фиг. 2 15, первый и второй элементы ИЛИ 16 и 17, — структурная электрическая схема решаю- первый и второй триггеры 18 и 19; первый и щего блока; на фиг. 3 — временные диаграм- второй элементы ЗИ 20 и 21 и элемент ИЛИмы., поясняющие принцип работы НЕ 22. устройства цикловой синхронизации мйого- Устройство работает следующим обраканальных систем связи. зом.

1757116

Последовательность чередующихся четных и нечетных ПСС в базисе Уолша из будут приняты. а в первый регистр 6 запишутся соответствующие этому три единицы (фиг. Зд).

По окончании цикла интегрирования из канала связи поступает на вход АЦП 1.

Пусть N=8. При этом таблица кодов АЦП примере (фиг. За) имеет амплитуду 4-3, соответственно на выходе АЦП 1 появится 1 0 1, 10 щей реализации ПСС (триггер 18 устанавлиЭтот код дешифруется дешифратором 15 и на его выходе (шестом) появляется логический сигнал "1", который поступает через вается в "1". а счетчик-шифратор 4 формирует следующий адрес, в данном слувторой элемент ИЛИ 17 на первый вход второго элемента ЗИ 21. Одновременно с чае 0...0 1, под управлением которого в демультиплексоре 5 информационный вход этим на второй вход второго элемента ЗИ 21 коммутируется на второй выход), Начинает20 Количество регистров 6 определяется этого тактовый импульс проходит через открытый второй элемент ЗИ 21 и элемент помеховой обстановкой в канале связи, На

ИЛИ jjg 22 на информационные входы всех фиг, 3 для простоты пояснения алгоритма регистров б. Однако запись "0" произойдет в первый регистр б (фиг. Зв, д), так как счетвыбран пример для двух регистров 6, Во второй реализации ПСС поражено чик-шифратор 4 находится в нулевом состо25 импульсной помехой два элемента. Реализация имеет вйд+1, -3, +5, +1, +1, +3. +3, -1, янии и на адресных . входах

30 шется информация 0,1,0,1,0,1,1,1 (фиг, 3e) мационный вход и первый выход демультиплексора 5 йодается на управляющий

Три последующих элемента реализации отвход последовательного ввода пеового ре- носятся к противоположному ilCC и на дангистра 6. Одновременно с записью первого ном интервале ийтегрирования не могут тактового импульса в первый регистр 6 пер- быть приняты, т .е. они определяют ошибку вый триггер 18 устанавливается в "0" и тем синхронизации. По окончании второго циксамым закрывается первый элемент ЗИ 20 ла интегрирования на выходе счетчика 11

Это предотвращает прием противоположного ПСС йа данном интервале приема. появится второй ИКЦ. Поскольку работа устройства рассматривается для двух регистАналогично происходит прием следуюров 6, то.после второго ИКЦ на выходе щих элементов четного ПСС. Например, за переноса счетчика-шифратора 4 появляется элементом +3 происходит прием элементов импульс. Одновременно с этим в многовхо-1, -1 и+3, Информаций о йх прйеме записы- довых элементах И 13 пройсходит операция вается в первый регистр 6 логическими 0" поэлементного перемножения содержимо(фиг. Зд). Предположигл, что последний зле- го всех регистров 6 (в нашем примере двух). мент четного ПСС с амплитудой -1 поражен

Содержимое первого регистра 6 0000 1111 импульсной йомехой и не принят. Тогда так- . и содержимое второго регистра 6 0 t010111 товый импульс, прйходящий на интервал перемножаются назлементахИ13,навыхопораженногоэлеменга, не проходит на вход дах которых пОявляется код 00000111 (фиг, первого регистра 6 и в йего запишется логи- Зж). На данном примере видно, как искажеческая "1", что свидетельствует о пропуске 50 ния, вйОсимые импульсными помехами, исправляются в устройстве. Причем в первой реализации ПСС импульсной помехой пораэлемента сигнала.

Далее на входы дешифратора 15 поступают элементы нечетного ПСС, которые дают отклики н а""е го не чет и ьГх вых одах; жен последний элемент четного ПСС.

С выходов элементов И 13 код 00000111 (фиг, Зж) поступает на выходы элемента

Логические "1" с указанйь!x аихбдов через

55 первый элемент ИЛИ 16 поступают на пер- ИЛИ 10, в котором осуществляется его про.вый вход первого элемента ЗИ 20. Однако верка на наличие или отсутствие ошибки элемент ЗИ 20 закрыт "0" с вйхода первого синхронизации. Каждый такт ошибки синхтриггера 18. Поэтому три последующих эле-- рбйизации вносит в код единицу. В нашем мента нечетного ПСС -3, -3 +1 (фиг. За) не случае на выходе многовходового элемента приведена.

Первый принятый элемент входной последовательности ПСС в рассматриваемом поступает тактовый импульс с выхода ЗГ 3 (фиг. Зб). На третьем входе второго элемента ЗИ 21 присутствует логическая "1" с выхода второго триггера I 9. В результате демультиплексора 5 присутствует код 0...0.

Последовательйость тактовых. импульсов записи с выхода ЗГ 3 (фиг, Зб) через инфорсчетчика-делителя 11 на управляющий вход решающего блока 2 и счетный вход счетчика-шифратора 4 поступает импульс конца цикла (ИКЦ) (фиг. Зг). В результате этого блок 2 разблокируется для приема следуюся второй цикл приема реализации ПСС, Информация о принятых и пропущенных элементах сигнала записывается во второй регистр б, а на вход АЦП 1 поступает+1.0, +5,0, +1, +3, +3, -+ (фиг. 3a). По аналогии с предыдущим циклом приема во второй регистр 6 запи1757116

ИЛИ 10 появляется единица (фиг. Зк), кото- вход которого является входом устройства, рая открываетпервыйзлемент И 8. Поддей- а выходы АЦП подключены к входам решаствием. второго ИКЦ на выходе прямого ющего блока, первый и второй элементы И, переноса. счетчика-шифратора4 появляется элемент ИЛИ, триггер, счетчик-делитель, импульс (фйг. Зи), который проходит через 5 счетчик-шифратор.элементЗАПРЕТи задаоткрытый элемент И 8 на единичный вход ющий генератор. выход которого подклютриггера 7, устанавливая его в "1", и на уп- . чен к стробирующему входу решающего равляющий вход параллельного ввода вы- блока, первому, входу второго элемента И и ходного регистра 12, где происходит запись в"оду элемента ЗАПРЕТ, при этом выход инвертированного кода ошибки синхрони- 10 счетчика-делителя подключен к нулегаму зации (111110100). Единичный потенциал с входу триггера, о т л и ч а ю щ е е с я тем, выхода триггера 7 (фиг. Зл) поступает. на что, с целью повышения помехоустойчивоэапрещающие входы решающего блока 2, сти цикловай синхронизации эа счет обнасчетчика-шифратора 4 и первый вход второ- ружения и устранения влияния пропусков го элемента И 9. Блоки 2 и 4 блокируются, а 15 элементов на стыке двух сигналов на проэлемент И 9 открывается, Через открытый цесс синхронизацйи, введены N регистров, второй элемент И 9 на управляющий вход К многавходавых элементов И, выходной последовательного вывода начинают посту- регистр и демультипликатор, к адресным патьтактовые импульсы с выхода ЗГ3(фиг. входам которого подключены выходы счетЗм), поддействием которых происходит Счи- 20 чика-шифратора, к запрещающему входу котывание информации. С выхода выходного тарога, а также к управляющему входу регистра 12 инвертированный код ошибки решающего блока подключен выход прямосинхронизации (11111000) подается на ин- го переноса счетчика-делителя и является версный вход элемента ЗАПРЕТ 14. Эле- . выходам устройства, а выход решающего мент ЗАПРЕТ 14 закроется на лять тактов 25 блока подключен к первым инфармацион(па числу единиц в инвертированном коде ным входам N регистров, к вторым инфорошибки синхронизации), следовательно, мацианнь|м входам которых подключены пять импульсов ЗГЗ не поступят на счетный выходы демультиплексора, к управляющему вход счетчика-делителя 11. В результате входу которого подключен выход задающаэтого фаза последовательности ИКЦ на вы- 30 га генератора, при этом выходы разряда . N ходе счетчика-делителя 11;стров подключены к входам соответстпять тактовых интервалов (фиг. 3) и совпада- вующих мнагавходовых элементов И, г .вдет с фазой принимаемой последовательно-. ды которых подключены к инверсным сти ПCC, Цикловая синхронизация входам вьходнага регистра ичереззлемент установлена. - .. :. 35 ИЛИ к первому входу первого элемента И, к

По окончании третьего цикла йнтегри- второму входу которого подключен выход рования (он оказался длиннее на пять так- прямого переноса счетчика-делителя, к тîBûх интервалав) на выходе - счетному входу которого, а также к второму счетчика-делителя 11 появляется третий входу второго элемента И и запрещающему

ИКЦ, под действием которого триггер 7 ус- 40 входу решающего блока подключен выход танавливается в "0". Решающий блок 2 и триггера, к единичному входу которого и счетчик-шифратор 4 разблокируются. Счи- управляющему входу выходного регистра тывание информации из выходного регист- подключен выход первого элемента И, а выра 12 прекращается, Начинается новый ход второго элемента И подключен к управцикл работы устройства цикловай синхро- 45 ляющему входу параллельного ввода низации. -- " - выходного регистра, выход которого подФ о р.м у л а и з о б р е т е н и я ключен к инверсному входу элемента ЗАУстройство. циклавой синхронизации ПРЕТ, выход которого подключен к входу многоканальных систем связи, содержащее счетчика-делителя. аналого-цифровой преобразователь (АЦП), 50

1757116

Ф:т. I

Фиг.?

ЮгпумаАще аачахи в. °

l йо.!..в ь ..4 г

OOOO fg 4 о оооо в 00000000OI IOI If и к

Фиг. 3

Составитель Г.Лерантовйч

Редактор О.Юрковецкая Техред M.Ìîðãåéòçë

Корректор О.Юрковецкая

Заказ 3100 . Тираж .. Подписное

ВНИИПИ Государственного комйтета по изобретениям и открытиям прй ГКНТ СССР

113035, Москва, Ж-35, Раушская наб.. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарйна. 101