Селектор импульсов по длительности

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано для допускового контроля длительности импульсов в системах автоматики, телемеханики и передачи дискретных сигналов. Целью изобретения является обеспечение возможности оперативной перестройки границ селекции. Селектор импульсов по длительности содержит генератор 1 тактовых импульсов , элементы И 2 и 10, счетчик 3 импульсов, инвертор 4, дешифраторы 5 и 6, выходные шины 11, 15 и 16, триггер 12, сумматор 14 по модулю 2, входную шину 17 Поставленная цель достигается за счет введения регистров 7-9 памяти, переключателя 13, блоков 18 и 19 вычитания кодов, блоков 20-22. сравнения кодов, регистров 23 и 24 сдвига, групп 25 и 26 элементов И, элементов ИЛИ 27 и 28, кодовых шин 29 - 31, шин 32 - 34 управления, инвертора 35 и образования новых функциональных связей . 1 з.п.ф-лы, 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (л!)5 Н 03 К 5/26

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4833777/21 (22) 15.03.90 (46) 30.08.92, Бюл.3Ф32 (71) Московский институт инженеров гражданской авиации (72) С.Ж.Кишенский, С.В,Каменский, В.Б.Панова и О.Ю,Христенко (56) Авторское свидетельство СССР

М 849476, кл, Н 03 К 5/26, 1979.

Авторское свидетельство СССР

N 1403359, кл, Н 03 К 5/26, 1986, (54) СЕЛЕКТОР ИМПУЛЬСОВ ПО ДЛИТЕЛЬНОСТИ (57) Изобретение относится к импульсной технике и может быть использовано для допускового контроля длительности импульсов в системах автоматики, телемеханики и. Ж,, 1758865 А1 передачи дискретных сигналов. Целью изобретения является обеспечение воэможности оперативной перестройки границ селекции. Селектор импульсов по длительности содержит генератор 1 тактовых импульсов, элементы И 2 и 10, счетчик 3 импульсов, инвертор 4, дешифраторы 5 и 6, выходные шины 11, 15 и 16, триггер 12, сумматор 14 по модулю 2, входную шину 17, Поставленная цель достигается за счет введения регистров 7 — 9 памяти, переключателя 13, блоков 18 и 19 вычитания кодов, блоков 20 — 22, сравнения кодов, регистров 23 и 24 сдвига, групп 25 и 26 элементов И. элементов ИЛИ 27 и 28, кодовых шин 29—

31, шин 32 — 34 управления, инвертора 35 и образования новых функциональных связей. 1 з.п,ф-лы, 2 ил.

1750065

20

25 лектора

55

Изобретение относится к импульсной .технике и может быть использовано для допускового контроля длительности импульсов в системах автоматики, телемеханики и передачи дискретных сигналов.

Известен селектор импульсов по длительности, содержащий генератор тактовых импульсов, два элемента И, формирователь импульсов, блок задержки, два дешифратора и счетчик импульсов.

Недостатками известного селектора являются длительное время перенастройки и узкие функциональные возможности.

Наиболее близким по технической сущности является селектор импульсов по длительности, содержащий генератор тактовых импульсов, два элемента И, счетчик импульсов, три дешифратора, два блока задержки, инвертор, триггер, формирователь гимпульсов и сумматор по модулю два

Недостатком известного селектора является невозможность оперативной перенастройки границ селекции импульсов, что ограничивает возможности применения сеЦелью изобретения является обеспечение возможности оперативной перестройки границ селекции.

Поставленная цель достигается тем, что в селектор импульсов по длительности, содержащий первый инвертор, вход которого соединен со входной шиной, а выход — с входом сброса счетчика импульсов, счетный вход которого соединен с выходом первого элемента И, первый вход которого соединен с выходом генератора тактовых импульсов, а также первый и второй дешифраторы, второй элемент И, выход которого соединен с первой выходной шиной. а первый вход — с выходом триггера, сумматор по модулю два, выход которого соединен со второй выходной шиной, причем выход триггера соединен с третьей выходной шинои, введены с первого по третий регистры памяти, первый и второй регистры сдвига, первый и второй блоки вычитания кодов, первая и вторая группы элементов И, первый и второй элементы ИЛИ, второй инвертор, с первой по третью кодовые шины, с первой по третью шины управления и с первого по третий блоки сравнения кодов, входы первой группы входов каждого из которых поразрядно соединены с выходами счетчика импульсов, входы второй группы входов первого блока сравнения кодов поразрядно соединены с выходами первого регистра памяти и также поразрядно с входами первой группы входов первого блока вычитания Kopos, выходы которого поразрядно соединены со входами первого дешифраторв, а входы второй группы входов поразрядно соединены,со входами второй группы входов второго блока сравнения кодов, также поразрядно — с выходами второго регистра памяти и также поразрядно с входами первой группы входов второго блока вычитания кодов, выходы которого поразрядно соединены с входами второго дешифратора, а входы второй группы входов — поразрядно с выходами третьего регистра памяти и также поразрядно со входами второй группы входов третьего блока сравнения кодов, выход которого соединен с R-входом триггера и через второй инвертор — со вторым входом первого элемента И, S-вход триггера соединен с первым входом сумматора по модулю два, с выходом второго блока сравнения кодов и с информационным входом второго регистра сдвига, выходы которого соединены с входами первой группы входов второй группы элементов И, а тактовый вход — с выходом генератора тактовых импульсов и с такто8blM входом первого регистра сдвига, информационный вход которого соединен с выходом первого блока сравнения кодов, а выходы — поразрядно со входами первой группы входов первой группы элементов И, входы второй группы входов которой пораз.рядно соединены с выходами первого дешифратора, а выходы — со входами первого элемента ИЛИ, выход которого соединен с вторым входом сумматора по модулю два, причем выходы второго дешифратора поразрядно соединены с входами второй группы входов. второй группы элементов И. выходы которой поразрядно соединены с входами второго элемента ИЛИ, выход которого соединен с вторым входом второго элемента И, причем информационные входы с первого по третий регистров памяти соединены соответственно с первой по третью кодовыми шинами, а входы записи — соответственно с первой по третью управляющими шинами.

Кроме того, в селектор импульсов по длительности введен переключатель, BKfllo ченный между выходом первого инвертора и входом сброса счетчика импульсов, причем второй вход переключателя соединен с входной шиной.

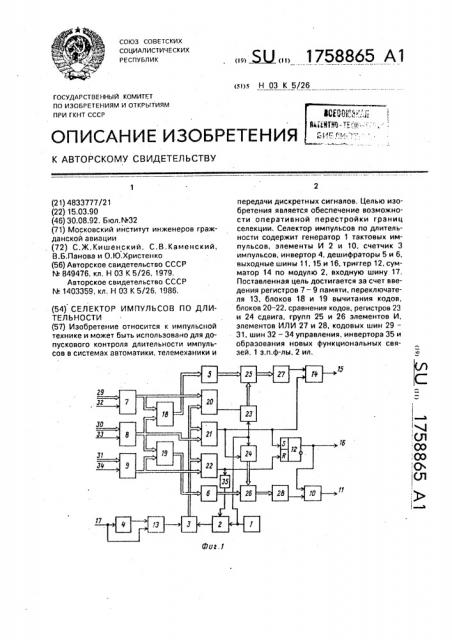

На фиг.1 приведена структурная электрическая схема селектора импульсов по длительности; на фиг.2 — временные диаграммы, поясняющие его работу.

Селектор импульсов по длительности содержит генератор 1 тактовых импульсов, первый элемент 2 И, первый счетчик 3 импульсов, первый инвертор 4, первый и второй дешифраторы 5 и б, первый, второй и третий регистры 7 — 9 памяти, второй зле1758865 мент 10 И, первую выходную шину 11, триггер 12, переключатель 13, сумматор 14 по модулю два, вторую и третью выходные ши-ны 15 и 1б, входную шину 17, первый и второй блоки 18 и 19 вычитания, с первого 5 по третий блоки 20 — 22 сравнения кодов, первый и второй регистры 23 и 24 сдвига, первую и вторую группы 25 и 26 элементов

И, первый и второй элементы 27 и 28 ИЛИ, с первой по третью кодовые шины 29 — 31, 10 с первой по третью шины управления 32— . 34, второй инвертор 35.

Устройство работает следующим образом.

До начала работы селектора в регистры 15 памяти 7, 8 и 9 заносятся соответственно двоичные коды значений Nu, No и Мв, которые пропорциональны соответственно г„— минимально допустимой длительности импульса, то — номинальной длительности им- 20 пульса .и тв — максимально допустимой длительности импульса, т.е, удовлетворяющие соотношениям;

25 тн < Го < гв, тн = Йн Tr, го = No Tã,,; тв = Ив Тт, где Тт — период импульсов с выхода генератора 1. Выбранные значения кодов устанав- 30 ливаются на кодовых шинах 29 — 31 и записываются в регистры памяти подачей импульсов записи на шины управления соответственно 32 — 34. После записи указанНоА информации на выходах блоков 35 вычитания 18 и 19 формиру1отся соответственно двоичные коды разностей lot = то TH и тэ2 = Тв То.

Переключатель 13 может быть выполнен виде мехэническог0 переключателя, 40 при анализе импульсов положительной полярности его выход подключается к входной шине 17, а для импульсов отрицательной полярности — к выходу инвертора 4, таким образом, при отсутствии импульса с выхода переключателя 13 снимается нулевой потенциал, удерживающий счетчик 3 импульсов в сброшенном состоянии, В момент поступления на входную шину 7 импульса (временные диаграммы фиг.2 50 приведены для импульсов положительной полярности) на выходе переключателя 3 появляется потенциал логической "1 "(фиг.2а). снимающий блокировку со счетчика 3, который начинает подсчат импульсов с генера- 55 тора 1, При длительности входного импульса т и, удовлетворяющей соотношению гс, < г 1 <

< хв, после поступления на вход счетчика 3

Nu тактовых импульсов, срабатывает блок

20 сравнения кодов (фиг,2б), на его выходе

"Равно" формируется сигнал, который записывается в младший разряд регистра сдвига

23 и продвигается по регистру 23 тактовыми импульсами. В любой момент времени лишь в одном разряде (не более) регистра сдвига

23 содержится логическая "1" (как и в регистре сдвига 24). Число выходов дешифраторов 5 и б равно максимально возможным значениям соответственно Not = (to — Tè)ITã и Ивр = (тв — ro)ITr, Число разрядов регистров сдвига 23 и 24, а также соответственно число элементов И в группах 25 и 26 также равно соответственно N3t и No2. Регистры сдвига организуют управляемую задержку импульсов; i-й выход дешифратора и выход

i-го разряда регистра сдвига подключены к входам i-го элемента И соответствующей группы.

Таким образом, для выбранных значений Ич и No сигнал положительного потенциала снимается лишь с одного из выходов дешифратора 5 и при достижении "1", соответствующей данному входному импульсу, соответствующего разряда, формируется положительный сигнал на выходе соответствующего элемента И группы 25 {фиг.2в), поступающий через элемент ИЛИ 27 на первый вход сумматора l4 по модулю два. Таким образом, формируется управляемая задержки импульса твт, регулируемая установкой значений NH u No.

При поступлении на вход счетчика 3 No тактовых импульсов срабатывает блок сравнения кодов 21 (фиг.2г). Импульс с его выхода поступает на второй вход сумматора 14.

Наличие сигналов на обоих входах сумматора 14 в соответствии с операцией сложения по модулю два не вызывает формирования на его ьыходе сигнала (фиг.2д), Одновременно сигнал с выхода "Равно" блока 21 устанавливает триггер 12 в единичное состояние (фиг.2е) или подтверждает его и на информационный вход регистра сдвига

24, в котором продвигается аналогично вышеописанному. реализуя задержку h2 = Тв— — го. После этой задержки импульс с выхода регистра сдвига 24 поступает на вход элемента И 10 (фиг.2ж). открытого для данного случая по второму входу положительным потенциалом с выхода триггера 12 и на выходе элемента И 10 (и шины 11) появляется сигнал, (фиг,2з), указывающий на то, что длительность импульса находится в пределах (To, тв)

При длительности входного импульса ги > тв (фиг,2, импульс т2) аналогично вышеописанному срабатывают блоки сравнения

1758865

20 и 21, через заданные времена задержки на выходах элементов 27 и 28 формируются импульсы. Аналогично, с выхода сумматора

14 импульс не формируется. Однако, в момент времени тв, соответствующий по- 5 ступлению на вход счетчика 3 NII тактовых импульсов, срабатывает по выходу "Равно" блок сравнения 22, сбрасывающий триггер

12 в нулевое состояние, чем запрещается формирование импульса на выходной шине 10

11, Нулевой сигнал с выхода второго инвертора 33 запрещает дальнейшее поступление тактовых импульсов на счетчик 3, в результате чего счетчик 3 остается в состоянии N8 до окончания текущего импульса, 15 после чего сбрасывается сигналом с переключателя 13 до начала следующего импульса. Наличие отрицательного перепада напряжения на выходе триггера и на шине

16 указывает на попадание входного им- 20 пульса в соответствующий диапазон длительностей, При выполнении условия т < ти < го .срабатывает блок 20. выходной импульс которого через интервал времени т, формиру- 25 ется на выходе блока 25 и поступает на вход блока 14. Однако, в данном случае не формируется импульс с выхода "Равно" блока

21, так как входной импульс заканчивается раньше этого момента, чта вызывает форми- 30 рование импульса, на выходе сумматора 14, указывающего на то, что длительность входного импульса попадает в соответствующий диапазон длительностей.

При длительности входного импульса 35 ти < r< счетчик 3 устанавливается в нулевое состояние окончанием этого импульса раньше, чем сработает блок 20 сравнения кодов.

Поэтому сигналы на выходных шинах 11, 15 и 16 не формируются, что указывает на по- 40 падание входного импульса в соответствующий диапазон длительностей.

Таким образом, селектор позволяет установкой значений N, Np и М автоматически регулировать значения задержки t i и 45

t3z, что обеспечивает автоматическую настройку селектора на выбранные границы селекции беэ изменения параметров какихлибо блоков селектора. Наличие переключателя 13 обеспечивает возможность анализа 50 как положительных, так и отрицательных входн ых импул ьсав.

Формула изобретения

1. Селектор импульсов по длительности, 55 содержащий первый инвертар, вход которого соединен с входной шиной, а выход — с входом сброса счетчика импульсов, счетный вход которого соединен с выходом первого элемента И. первый вход которого соединен с выходом генератора тактовых импульсов, а также первый и второй дешифратары, второй элемент И, выход которого соединен с первой выходной шиной, а первый вход — с выходом триггера, сумматор по модулю два, выход которога соединен с второй выходной шиной, причем выход триггера соединен с третьей выходной шиной, о т л и ч а юшийся тем, что, с целью обеспечения возможности оперативной перестройки границ селекции. в него введены с первого па третий регистры памяти, первый и второй регистры сдвига, первый и второй блоки вычитания кодов, первая и вторая группы элементов И, первый и второй элементы ИЛИ, второй инвертор, с первой па третью кодовые шины, с первой по третью шины управления и с первого по третий блоки сравнения кодов, входы первой группы входов каждого из которых поразрядно соединены с выходами счетчика импульсов, входы второй группы входов первГ а блока сравнения кодов поразрядно соединены с выходами первого регистра памяти и также поразрядно с входами первой группы Входов первого блока вычитания кодов, выходы которого поразрядно соединены с входами первого дешифратора, а входы второй группы входов поразрядно соединены с входами второй группы входов втарогаблокасравнения кодов, также поразрядно — с выходами второго регистра памяти и также поразрядно с входами. первой группы входов второго блока вычитания кодов, выходы которого поразрядно соединены с входами второго дешифратара, а входы второй группы входов — поразрядно с выходами третьего регистра памяти и также поразрядно с входами второй группы входов третьего блока сравнения кодов, выход которого соединен с Rвходом триггера и через второй инвертар— с вторым входам первого элемента И, причем S-вход триггера соединен с первым входом сумматора по модулю два, с выходом второго блока сравнения кодов и с информационным входом второго регистра сдвига, выходы которого соединены с входами первой группы входов второй группы элементов И, а тактовый вход — с выходом генератора тактовых импульсов и с тактовым входом первого регистра сдвига, информационный вход которого соединен с выходом первого блока сравнения кодов, а выходы— поразрядно с входами первой группы входов первой группы элементов И, входы второй группы входов которой поразрядно соединены с выходами первого дешифратара, а выходы — с входами первого элемента

ИЛИ, выход которого соединен с вторым

1758865

Фие Г

Составитель С.Кишенский

Редактор О.Спесивых Техред М.Моргентал Корректор П,Гереши

Заказ 3012 Тираж Подписное

ВКИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35. Раушская наб., 4!5

Производственно-нзда1ельский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 входом сумматора по модулю два, причем выходы второго дешифратора поразрядно соединены с входами второй группы входов второй группы элементов И, выходы которой поразрядно соединены с входами второго элемента ИЛИ, выход которого соединен с вторым входом второго элемента И, причем информационные входы с первого по третий регистров памяти соединены соответственно с первой по третью кодовыми шинами, а входы записи — соответственно с первой по третью управляющими шинами.

2. Селектор по п.1, отличающийся тем, что, с целью обеспечения возможности

5 селектирования входных импульсов с активным уровнем как логической "1", так и логического "0", в него введен переключатель, включенный между выходом первого инвертора и входом сброса счетчика импульсов, 10 причем второй вход переключателя соединен с входной шиной.