Времяимпульсный компаратор

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в составе контрольно-измерительных и управляющих систем. Целью изобретения является обеспечение возможности анализа соответствия длительности импульсов в импульсной последовательности заданному интервалу длительностей. Времяимпульсный компаратор содержит формирователь 1 импульсов, входную шину 2, генератор 3 тактовых импульсов, блоки 4 и 5 синхронизации , элементы И о - 10, элемента ИЛИ 14, элемент 15 задержки, регистр 16 сдвига, цифровые компараторы 18 и 19, триггер 20. коммутатор 22, счетчики 24 и 25 импульсов, выходные шины 28 и 29. Поставленная цель достигается за счет введения элементов И 11 - 13, регистра 17 сдвига, триггера 21, коммутатора 23. счетчика 26 импульсов, сумматора 27 и образования новых функциональных связей.2 ил

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

PFСПУБЛИК (51)5 K 03 К 5/26

ГО СУДА Р СТО Е ННЫ И КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ и

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4833781/21 (22) 28.03.90 (46) 30.08.92. Бюл. ¹32 (71) Московский институт инженеров гражданской авиации (72) С.Ж.Кишенский, С.В.Каменский, В.П.Панова и О.Ю.Христенко (56) Авторское свидетельство СССР № 1081785, кл. Н 03 К 5/26, 1982.

Авторское свидетельство СССР № 1403361, кл. Н 03 К 5/26, 1986. (54) ВРЕМЯИМПУЛЬСНЫЙ КОМПАРАТОР (57) Изобретение. относится к импульсной технике и может быть использовано в составе контрольно-измерительных и управляющих систем. Целью изобретения является Ы 17588б7 А1 обеспечение возможности анализа соответствия длительности импульсов B импульсной последовательности заданному интервалу длительностей. Времяимпульсный компаратор содержит формирователь 1 импульсов, входную шину 2, генератор 3

TBKTo8blx импульсов, блоки 4 и 5 синхронизации, элементы И 6 — 10, элемента ИЛИ 14, элемент 15 задержки, регистр 16 сдвига, цифровые компараторы 18 и 19, триггер 20, коммутатор 22, счетчики 24 и 25 импульсов, выходные шины 28 и 29. Поставленная цель достигается за счет введения элементов И

11 — 13. регистра 17 сдвига. триггера 21, коммутатора 23, счетчика 26 импульсов, сумматора 27 и образования новых функциональных связей. 2 ил

1758867

Изобретение относится к импульсной технике и может быть использовано в составе контрольно-измерительных и управля ощих систем, Известен времяимпульсный компаратор, содержащий формирователь импульсов, триггер, элемент ИЛИ, элемент задержки, первый и второй счетчики, пять элементов И.

Недостатком известного компаратора является низкое быстродействие и узкие фун кционал ьн ые возмо>кн ости.

Наиболее близким по технической сущности к заявляемому является времяимпульсный ком паратор, содержащий формирователь импульсов, дна счетчика, элемент ИЛИ, элемент задержки, триггер, пять элементов И, два блока синхронизации, два коммутатора, два цифровых компаратора и генератор тактовых импульсов.

Недостатком известного компаратора является отсутствие возможности анализа соответствия длительностей импульсов в последовательности заданному интервалу длительностей, поскольку его функциональные воэможности ограничиваются сравнением длительностей импульсов последовательности с некоторым фиксированным эталонным значением и не допускают сравнения с интервалом значений.

Целью изобретения является обеспечения возможности анализа соответствия длительности импульсов в импульсной последовательности заданному интервалу длительностей, Поставленная цель достигается тем, что во времяимпульсный компаратор, содер>кащий формирователь импульсов, вход которого соединен с входной шиной, а первый и второй выходы — с информационными входами соответственно первого и второго блоков синхронизации, первый и второй тактовые входы которых соединены соответственно с первым и вторым выходами генератора тактовых импульсов, первый выход которого соединен с первым входом первого элемента И, второй вход которого соединен с первым входом второго элемента И и прямым выходом первого триггера, S-вход которого соединен с выходом первого блока синхронизации, а R-вход — с выходом элемента ИЛИ и входом элемента задержки, выход которого соединен с тактовым входом первого регистра сдвига и входом сброса первого счетчика импульсов, выходы которого поразрядно соединены с входами первого коммутатора, выходы которого поразрядно соединены с входами третьего элемента И, прямой выход которосо соединен с информационным входом

55 прямой выход третьего элемента И соединен с вторым входом элемента ИЛИ.

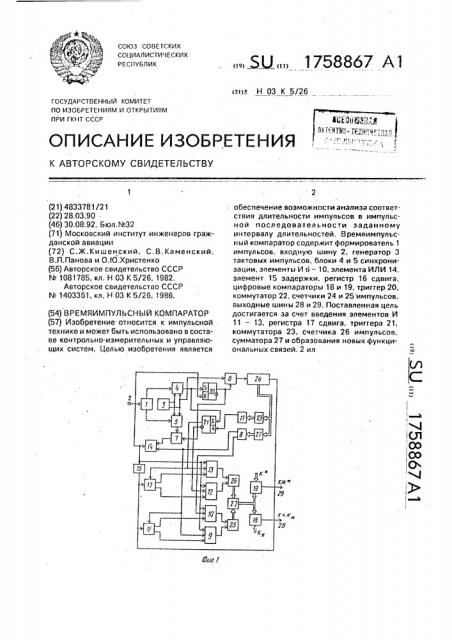

На фиг,1 представлена структурная электрическая схема времяимпульсного компаратора; на фиг,2 — временные диаграммы, поясняющие работу устройства.

Времяимпульсный компаратор содержит формирователь 1 импульсов, входную шину 2, генератор 3 тактовых импульсов, первый и второй блоки 4 и 5 синхронизации, первого регистра сдвига, причем выход второго блока синхронизации соединен с вторым входом нторого элемента И, выход которого соединен с первым входом элемента ИЛИ, выход которого соединен с первыми входами четвертого и пятого элементов И, вторые входы которых соединены соответственно с прямым и инверсным выходами третьего элемента И, третьи входы — соответственно с инверсным и прямым выходами первого регистра сдвига, а выходы — соответственно с суммирующим и вычитающим входами второго счетчика импульсов, выполненного реверсивным, причем входы первых групп входов первого и второго цифровых компараторон соединены соответственно с первой и второй установочными шинами, входы вторых групп входов поразрядно обьединены, а выходы соединены соответственно с первой и второй выходными шинами, введены второй коммутатор. второй триггер, второй регистр памяти, третий счетчик импульсов, выполненный реверсивным, с шестого по восьмой элементы И и сумматор, выходы которого поразрядно соединены с входами второй группы цифрового компаратора, входы первой группы входов — поразрядно с выходами второго счетчика импульсов, входы второй группы входов — поразрядно с выходами третьего счетчика импульсов, вычитающий и суммирующий входы которого соединены соответственно с выходами седьмого и восьмого элементов И, первые входы которых соединены с выходом элемента ИЛИ, вторые входы — соответственно с инверсным и прямым выходами второго триггера, а третьим входы — соответственно с прямым и инверсным выходами второго регистра сдвига, тактовый вход которого соединен с выходом элемента задержки, а информационный вход — с прямым выходом второго триггера, S-вход которого соединен с выходом первого блока синхронизации, à R-вход — с выходом шестого элемента И, входы которого поразрядно соединены с выходами

Второго коммутатора, входы которого поразрядно соединены с выходами первого счетчика импульсов, счетный вход которого соединен с выходом первого элемента И

1758867 с первого по восьмой элементы 6 — 13, элемент 14 ИЛИ, элемент 15 задержки, первый и второй регистры 16 и 17 сдвига, первый и второй цифровые компараторы 18 и 19, первый и второй триггеры 20 и 21, первый и 5 второй коммутаторы 22 и 23, первый, второй и третий счетчики 24 — 26 импульсов, сумматор 27, первую и вторую выходные шины 28 и 29.

Устройство работает следу»ощим обра- 10 зом, На шину 2 поступают прямоугольные импульсы различной длительности. Формирователь 1 формирует на первом выходе, соединенном с блоком 4 синхронизации, ко- 15 роткий импульс по переднему фронту входного импульса, а на втором выходе— короткий импульс по спаду входного импульса. Генератор 3 формирует на выходах импульсы прямоугольно»л формы высокой 20 частотой с периодом То, сдвинутые относительно друг друга по фазе на время То/2.

Блоки 4 и 5 синхронизации осуществляют привязку входных импульсов к тактовым; сигнал о начале (или окончании) входного 25 импульса выдается на выход соответствующего блока синхронизации в момент поступления сигнала с генератора 3, причем с того выхода, который не соединен с входом элемента И 6. Количество входов элементов 30

И 8 и 11 равно количеству разрядов счетчика

24 (m). Элемент И 8 кроме прямого выхода имеет второй (инверсный) выход. Элемент

15 задерживает импульсы на время, достаточное для прохождения сигналов через 35 элементы 9 — 13. Регистры 16 и 217 — регистры сдвига, их разрядность равна и, где и — число сравнений последовательных импульсов в импульсной последовательности, учитываемые при принятии решения время- 40 импульсным компаратором. Цифровой КоМпаратор l8 формирует на выходе единичный сигнал при К < К*, где К вЂ” код числа на выходе сумматора 27, К+ — число, установленное на первой установочной ши- 45 не. Аналогично, цифровой компаратор 19 формирует единичный сигнал на выходе при К > К*, где К* — число. установленное на второй установочной шине. Коммутаторы 22 и 23 могут представлять собой, например, 50 группы двухпозиционных переключателей, подключающие выбранные прямые или инверсные выходы соответствующих разрядов счетчика 24 к выходам коммутаторов. . При соответствующей настройке на выхо- 55 дах элементов И 8 (прямом) и 1 формируются положительные сигналы при выполнении соответственно условий г» > s»» и 1» > т»ь Счетчики 25 и 26 — реверсивные, их емкость должна быть достаточной для записи числа и, Длительности текущих входных интервалов времени т»» (импульсов) сравниваются (в цифровой форме) с заданными границами допустимых длительностей: нижней т» и верхней Ts, результат каждого сравнения записывается в регистры 16 и 17: при т > t, "1" записывается в регистр 16, при т»» < гн— в регистр 17, при т» < т„< т» в оба регистра записываются нулевые значения. С помощью регистров 16 и 17 в счетчиках 25 и 26 соответственно формируются значения чисел КБ и К»», равные соответственно количеству(из п последних сравнений) результатов

"Больше т " и "Меньше г»,". эти числа суммируются на сумматоре 27, на выходе которого формируется. число К = К + К ("НЕ в допуске"), сопоставляемое на компараторах 18 и

19 с заданными нижней К* и верхней K границами допустимого числа несовпадений. При К < К*, К > К* и К < К К соответственно принимаются решения "Меньше", "Больше" и "Равно" ("В допуске").

Таким образом. решение формируется по "скользящей выборке" — результатам последних по времени и сравнений.

В исходном состоянии блоки 16, 17, 20, 21, 24 — 26установлены в нуль. Коммутаторы

22 и 23 соответственно обеспечивают срабатывание элементов И 8 и 11 при содержимом счетчика 24 N» = т lТО и М =- гПо. На первой и второй установочных шинах (вторых группах входов компараторов 18 и 19) установлены двоичных коды чисел К* и К+ в течение всего сеанса работы.

В момент появления предлагаемого фронта импульса на входной шине 2 устройства (фиг.2а) на первом выходе формирователя 1 формируется короткий импульс (фиг.2б), поступающий на информационный вход блока 4 синхронизации. Ближайший по времени тактовый импульс с второго выхода генератора 3 (фиг.2д) формирует выходной импульс на выходе блока 4, устанавливающий в единичное состояние триггеры 20 (фиг.2e} и 21 (фиг.2ж), в результате чего открывается элемент И 6 (фиг.2з) и тактовые импульсы с первого выхода генератора 3 (фиг.2г) поступают на счетчик 24. Открывается также элемент И 7.

В момент окончания входного импульса формируется короткий импульс на втором выходе формирователя 1 (фиг.2в). В интервале времени между импульсами с первого и второго выходов формирователя 1 в счетчике 24 подсчитываются N тактовых импульсов, соответствующих длительности входного импульса ти = и Т>.

1758867

Если l> > т, (фиг.2, момент времени 1э), то N> > N и, следовательно, после некоторого тактового импульса будет выполнено условие Ng = Ne. В результате формируется единичный сигнал на прямом выходе weмента И 8 (фиг.2н), который, проходя через элемент ИЛИ 14 (фиг,2м), устанавливает триггер 20 в нулевое состояние, прекращая поступление импульсов с генератора 3 на счетчик 24, Этот же импульс способствует закрытию элемента. И 7 (фиг,2л), а также, проходя через открытый положительным потенциалом на инверсном выходе регистра 16 элемент И 9, поступает на суммирующий вход реверсивного счетчика 25; задерживаясь на элементе 15 задержки, эот импульс сдвигает содержимое регистра 16 на один разряд, записывая в младший разряд регистра 16 "1" с выхода элемента И 8; в этот же момент времени устанавливается в нулевое состояние счетчик 24. Поскольку число N< всегда меньше числа N (на эти числа соответственно настроены коммутаторы 22 и 23), то до срабатывания элемента

И 8 срабатывает элемент И 11 (фиг.2и) — в момент времени тя, и устанавливает триггер

21 в нулевое состояние, Таким образом, при формировании импульса с выхода элемента

15 задержки в данном случае в младшие разряды регистров 16 (фиг,2о) и 17 (фиг.2п) записываются соответственно "1" и "0".

Приходящий в данном случае импульс с выхода блока 5 синхронизации (фиг,2к) через элемент И 7 (фиг.2л) не проходит, Если тп < ти < т, (фиг,2в, импульс, начинающийся в момент времени t>), то при N =

Мн срабатывает элемент И 11, устанавливает триггер 21 в нулевое состояние, а импульс а выхода блока 5 поступает раньше, чем сработает элемент И 8. При этом импульс с блока 5 проходит через элемент ИЛИ 14, сбрасывает триггер 20, закрывая элемент И

6, и не изменяет содер>кимое счетчиков 25 и

26 (элементы 9 и 13 закрыты по вторым входам, а элементы 10 и 12 — по третьим входам). Импульсы с выхода элемента задержки 15 в регистры 16 и 17 записываются нулевые значения.

При т1 < тв (фиг.2. момент тр) сигнал с выхода блока 5 формируется раньше, чем сигнал на выходе элемента И 11, в результате чего икрементируется содержимое счетчика 26 через открытый элемент И 13, в регистр 17 импульсом с элемента 15 записывается "1", а в регистр 16 — "0". В данном случае триггер 21 остается в единичном состоянии (фиг,2ж) и в дальнейшем (до анализа следующего импульса последоватепьности) не оказывает влияния на работу устройства, Аналогично обрабатываются все импульсы последовательности: ти1, т 12 и т.д. В результате в счетчике 25 формируется число

К>, равное количеству результатов "Больше" среди презультатов измерений,,в счетчике

26 — число Кн, равное количество результатов "Меньше"; на сумматоре 27 — число К =

=К + Кв, равное количеству результатов "Не

10

Аналогично работает счетчик 26; при этом элементы 12 и 13 соединены соответственно с вычитающим и суммирующим входами счетчика 26 (аналогично тому, как выходы элементов 9 и 10 соединены соответственно с суммирующим и вычитающим входами счетчика 25).

Таким образом, устройство позволяет сформировать "зону допуска" при анализе каждого интервала времени (импульса), и анализировать соответствие каждого импульса последовательности по длительности выбранной зоне допуска, Возможно и осуществление раздельнога контроля (по содержимому счетчиков 25 и 26 конкретных

55 в допуске". На выходных шинах 28 и 29 совокупность сигналов (саотве гствен Но S1 и

S2) определяет результат текущего анализа и смежных, импульсов (интервалов време15 ни). При К > К*, Яг = 1, S> = 0; так кодируется решение "Меньше". При К < К*, S) = $2 = 0: так кодируется решение "В допуске". В регистрах 16 и 17 хранятся результаты анализа по и последним интервалам времени.

20 Так работает устройство для первых и интервалов времени (импульсов). Последующая работа устройства требует коррекции текущих результатов (в соответствии с алгоритмом "скользящей выборки") требующей

25 учета кроме результата анализа текущего импульса так>ке результата анализа самого

"старого" (исключаемого из дальнейшего анализа) импульса. Это осуществляется следующим образом (на примере счетчика 25).

30 Если в последнем разряде (выходном) регистра 16 записана "1", то элементы И 9 и

10 закрыты — соответственно по третьему и второму входам: содержимое счетчика не меняется: не меняется и количество лагиче35 ских "единиц" в регистре 16 — одна "1" выводится, а другая записывается в младший разряд регистра 16. При этом открыт элемента И 10 и импульс с выхода элемента

ИЛИ 14 поступает на вход вычитания счет40 чика 25. Таким образом, содержимое счетчика 25 всегда равно текущему количеству результатов "Больше", 1758867 знаков отклонений длительностей импульсов от допусковой эоны).

Формула изобретения

Времяимпульсный компаратор, содержащий формирователь импульсов, вход которого соединен с входной шиной, а первый и второй выходы — с информационными входами первого и второго блоков синхронизации, первый и второй тактовые входы которых соединены соответственно с первым и вторым выходами генератора тактовых импульсов, первый выход которого соединен с первым входом первого элемента И, второй вход которого соединен с первым входом второго элемента И и прямым выходом первого триггера, S-вход которого соединен с выходом первого блока синхронизации, à R-вход — с выходом элемента

ИЛИ и входом элемента задержки, выход которого соединен с тактовым входом первого регистра сдвига и входом сброса первого счетчика импульсов. выходы которого поразрядно соединены с входами первого коммутатора, выходы которого поразрядно соединены с входами третьего элемента И, прямой выход которого соединен с информационным входом первого регистра сдвига, причем выход второго блока синхронизации соединен с вторым входом второго элемента И, выход которого соединен с первым входом элемента ИЛИ, выход которого соединен с первыми входами четвертого и пятого элементов И, вторые входы которых соединены соответственно с прямым и инверсным выходами третьего элемента И, третьи входы — соответственно с инверсным и прямым выходами первого регистра сдвига, а выходы — соответственно с суммирующим и вычитающим входами второго счетчика импульсов, выполненного реверсивным, причем входы первый групп входов первого и второго цифровых компараторов соединены соответственно с первой и второй установочными шинами, входы вторых групп входов поразрядно объединены, а выходы соединены соответственно с

5 первой и второй выходными шинами, о т л ич а ю шийся тем, что, с целью обеспечения возможности анализа соответствия длительности импульсов в импульсной последовательности заданному интервалу

10 длительностей, в него введены второй коммутатор, второй триггер, второй регистр сдвига, третий счетчик импульсов, выполненный реверсивным, с шестого по восьмой элементы И и сумматор, выходы которого

15 поразрядно соединены с входами второй группы входов первого цифрового компаратора, входы первой группы входов — поразрядно с выходами второго счетчика импульсов. входы второй группы входов по20 разрядно с выходами третьего счетчика импульсов. вычитающий и суммирующий вход которого соединены соответственно с выходами седьмого и восьмого элементов И, первые входы которых соединены с выходом

25 элемента ИЛИ, вторые входы — соответственно с инверсным и прямым выходами второго триггера, а третьи входы — соответственно с прямым и инверсным выходами второго регистра сдвига, тактовый вход ко30 торого соединен с выходом элемента задержки, а информационный вход — с прямым выходом второго триггера, S-вход которого соединен с выходом первого блока синхронизации, а R-вход — с выходом шестого эле35 мента И, входы которого поразрядно соединены с выходами второго коммутатора, входы которого поразрядно соединены с выходами первого счетчика импульсов. счетный вход которого соединен с выходом

40 первого элемента И, причем прямой выход третьего элемента И соединен с вторым входом элемента ИЛИ.

1758867 4 3

2 д

У г

Л

Ю

Н

Й02. 2

Составитель С.Кишенский

Редактор 0,Спесивых Техред М.Моргентал Корректор A.Bîðîâè÷

Заказ 3012 Тираж Подписно

ВНИ одписное

В ИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35. Рауаская наб., 4/5 роизводственно-издательский комбинат "Патент", г. Ужгород, уг.Гагарина 101