Устройство передачи и приема сигналов

Иллюстрации

Показать всеРеферат

СОЮЗ СОГЗЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

Респувдик (5125 I-(04 1 1/08

ГОСУЛАРСТБНП ЫИ,OMMTF T

ПО ИЗОБРЕТЕ11ИЯГ1 И ОТКРЬП ИЯМ

Г1РИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИ

К АВТОРСКОМУ СВИДЕТЕJlbCTIÇY

g Q АРк я)1

2 (21) 4667789/09 (22) 10,02.89 (46) 30.08,92. Б,on. ¹ 32 (71) Институт кибер»етики с вычислительным центром Узбекского нау1»о-производ ственного обьединения "Кибернети";;"

АН УЗССР (72) Э.Б.1Лахмудов, Э.Н.Биктимиров, В.С.Мирахмедов, Д.В.Протопопов, Э.Улжаев и Б.А,Захидов (56) Авторское свидетельство СССР № 944130, кл. I-I 04 L 1/10, 1982, Авторское свидетельство СССР № 1061275, кл. Н 04 (1/10, 1983.

Заявка ФРГ ¹ 3126894, кл, Н 04 1. 25/04, 1983.

Кобленц А.И и др. ПЛнооканальная электросвязь и каналообразующая телеграфная аппаратура. M. Радио и связь, 1989, с. 153, рис.7.22. (54) УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕХАЛА

СИГНАЛОВ

Изобретение относится к электросвязи и может использоваться в системах передачи информации с многократным повторением сообщений для их мажоритарной обработки и коррекции ошибок.

Извес1но устройство для исправления ошибок в кодовой комбинации, содержащее два пороговых блика. два ключа, три сумматора.по модулю два, элемент И, два элемента ИЛИ, блок обнаружения ошибок. накопитель и элемент запрета.

Известно также устройство для исправлсния одиночных и обнаружения многократных ошибок, содержащее входной,, Я ÄÄ 1758887 А1 (57) Изобретение относится к электросвязи и может использоваться в системах передачи информации с многократным повторением сообщений для их мажоритарной обработки и коррекции ошибок. Целью изобретения является повышение помехоустойчивости при воздействии нерегулярных импульсных помех. Устройство передачи и приема сигналов содержит на передающей стороне демультиплексор, блок задержек, мультиплексор передачи, формирователь ьыходного сигнала, формирователь управляюших сигналов и блок синхронизации, а на прием»ой стороне — блок согласования, демультиплексор при--ма, блок задержек, блок дешифрации и блок синхронизации, Исходная цифровая последовательность преобразуетс".. на передающей стороне таким образом, что вместо каждого символа передаются три таких же символа, которые на приемном конце путем мажоритарной обработки восстанавливаются с исправлением возникающих в процессе передачи ошибок.

1 ил. 1 табл. накопитель, шесть ключей, сумматор по модулю два, блок обнаружения ошибок, триггер, динамический триггер. счетчик, дешифратор, элемент ИЛИ и дешифратор базового остатка, в котором исправление и обнаружение ошибок достигается благодаря использованию циклических кодов.

Недостатками известных устройств явл>-. отся сложность аппаратур»ой реализации, большое время обнаружения и исправления ошибок, а также невысокая помехоустсйчивость.

Известно устройство коррекции ошибок в разрядах, содержащее реверсив»ый счет1758887 чик и четыре логических элемента, в котором неискаженное значение (О или 1) каждого передаваемого разряда определяется путем многократного (не менее трех раз) сканирования сигнала.

Недостатком известного устройства является то, что для нормального функционирования оно требует исключительно побитой организации передачи цифровой информации и, кроме того, значительное время коррекции ошиб6к:

Наиболее близким по технической сущности к заявляемому устройству является выбранное в качестве протокола устройство передачи и приема сигналов, содержащее на передающей стороне последовательно соединенные мультиплексор передачи и блок формирования выходного сигнала, а также блок синхронизации и другие блоки, а на приемной стороне — последовательно соединенные блок согласования и демультиплексор приема, а также блок синхрони зации и другие блоки, Недостатком известного устройства является низкая помехоустойчивость при воздействии нерегулярных импульсных помех, приводящая к необратимой потере информации.

Целью изобретения является повышение помехоустойчивости при воздействии нерегулярных импульсных помех.

Указанная цель достигается тем, что в устройство передачи и приема сигналов, содержащее на передающей стороне последовательно соединенные мультиплексор передачи и блок формирования выходного сигнала, а также блок синхронизации, а на приемной стороне — последовательно соединенные блок согласования и демультиплексор приема, а также блок синхронизации, на передающей стороне дополнительно введены формирователь управляющих сигналов и последовательно соединенные демультиплексор и блок задержек, выходы которых соединены с соответствующими входами мультиплексора передачи, причем вход формирователя управляющих сигналов соединен с информационным входом демультиплексора, управляющие входы которого соединены с соответствующими входами блока синхронизации и с соответствующими выходами формирователя управляющих сигналов, при этом управляющие входы мультиплексора передачи соединены с соответствующими выходами блока синхронизации, а на приемной стороне — последовательно соединенные блок задержек и блок дешифрации, при этом входы блока задержек соединены с соответствующими выходами демультип5

55 лексора приема, управляющие входы которого соединены с соответствующими выходами блока синхронизации, вход которого соединен со входом блока согласования.

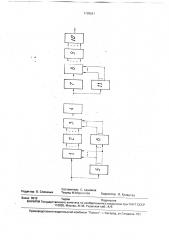

На чертеже представлена структурная электрическая схема устройства передачи и приема сигналов.

Устройство передачи и приема сигналов содержит на передающей стороне последовательно соединенные демультиплексор 1, блок 2 задержек, мультиплексор 3 передачи и блок 4 формирования выходного си нала, причем информационный вход демультиплексора 1 подключен ко входу формирователя 5 управляющих сигналов. соответствующие выходы которого одновременно соединены с управляющими входами демультиплексора 1 и с соответствующими входами блока 6 синхронизации, при этом управляющие входы мультиплексора 3 передачи соединены с соответствующими выходами блока б синхронизации, а на приемной стороне последовательно соединенные блок 7 согласования, демультиплексор 8 приема, блок 9 задержек и блок 10 дешифрации, причем вход блока 7 согласования подключен ко входу блока 11 синхронизации,соответствующие выходы которого соединены с управляющими входами демультиплексора 8 приема.

Устройство передачи и приема сигналов работает следующим образом, Исходная цифровая последовательность, в которой первый бит является синхронизирующим и всегда имеет уровень логической единицы. одновременно поступает на информационный вход демультиплексора I и на вход формирователя 5 управляющих сигналов. Синхроимпульс выделяется формирователем 5 управляющих сигналов и начинает вырабатывать сигналы, поступающие на управляющие входы демультиплексора 1, Под действием этих управляющих сигналов импульсы с информационного входа демультиплексора

1 последовательно коммутируются на его выходы и поступают на соответствующие входы блока 2 задержек. Блок 2 задержек осуществляет задержку каждого бита на время t = n-2 т, где и = 1, 2, 3,... и гдлительность символа {0; 1), с тем, чтобы после прохождения через мультиплексор 3 передачи, на его выходе сформировалась последовательность тех же самых битов, но уже с расстоянием между ними, равным 2 t.

Это поеобразование необходимо для того, чтобы исключить возможность наложения символов друг на друга после того, как все

1758887 они последовательно поступят на вход блока 4 формирования выходного сигнала, который увеличит длительность каждого из них в три раза, т,е. ЩООО; 111}, Сформированная таким образом последователь- 5 ность символов поступает в канал связи.

Управление работой мультиплексора 3 передачи осуществляется благодаря сигналам, поступающим на его управляющие входы с соответствующих выходов блока 6 10 синхронизации, которые, в свою очередь, вырабатываются посредством импульсов, приходящих с соответствующих выходов формирователя 5 управляющих сигналов.

Пройдя через канал связи, преобразо- 15 ванная кодовая последовательность одновременно поступает на входы блока 7 согласования и блока 11 синхронизации.

Блок 7 согласования осуществляет задержку принятой дискретной последовательно- 20 сти на время, необходимое для начала генерации управляющих символов блоком

11 синхронизации после прихода синхроимпульса. Под действием этих сигналов. поступающих на управляющие входы 25 демультиплексора 8 приема, информационные символы с его входа последовательно коммутируются на три выхода. Блок задержек 9 производит задержку каждого бита на различные периоды времени с тем, чтобы 30 все три символа, соответствующие исходному биту, поступили одновременно на входы блока 10 дешифрации. Принцип работы блока 10 дешифрации заключается в том, что на его выходе будет логический ноль только в 35 том случае, если не менее двух битов равны

JIoI è÷åñêoìó нулю, и на его выходе будет логическая единица только в том случае, когда хотя бы два бита равны логической единице, и задается с помощью таблицы. 40

Таким образом, при вышеприведенном алгоритме работы блока 10 дешифрации на его выходе будет сформирован лсходный сигнал.

Устройство передачи и приема сигналов повышает помехоустойчивость передачи дискретной информации благодаря исправлению ошибок, возникающих под дейс1вием нерегулярных импульсных помех в канале связи.

Формула изобретения

Устройство передачи и приема сигналов, содержащее на пеоедающей стороне последовательно соединенные мультиплексор передачи и блок формирования выходного сигнала, а также блок синхронизации, а на приемной стороне — последовательно соединенные блок согласования и демультиплексор приема, а также блок синхронизации, о тл и ч а ю ще е с я тем, что, с целью повышения помехоустойчивости при воздействии нерегулярных импульсных помех, на передающей стороне введены формирователь управляющих сигналов и последовательно соединенные демультиплексор и блок задержек, выходы которых соединены с соответствующими входами мультиплексора передачи, причем вход формировзтеля управляющих сигналов соединен с информационным входом демультиплексора, управляющие входы которого соединены с соответствующими входами блока синхронизации и соответствующими выходами формлрователя управляющих сигналов, при атом управляющие входы мультиплексора передачи соединены с соответствующими выходами блока синхронизации, а на приемной стороне — последовательно соединенные блок задержек и блок дешифрации, при атом входы блока задержек соединены с соответствующими выходами демультиплексора приема, управляющие входы которого соединены с соответствующими выходами блока синхронизации, вход которого соединен с входом блока согласования.

1758887

Составитель С, Аджемов

Редактор О. Спесивых Техред M.Mopãåíòàë Корректор g, Крае ода

Заказ 3013 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101