Усилитель с защитой от перегрузки

Иллюстрации

Показать всеРеферат

СОКТЗ СОИ (СКИХ

Г О!!ИАЛИСТИЧЕСКИХ

РРСПУВЛИК (я)5 Н 02 Н 7/20

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCKOMY СВИДЕТЕЛЬСТВУ (21) 4901066/07 (22) 09.01.91 (46) 07.09.92. Бюл N. 33 (71) Научно-исследовательский институт электротехники (72) Л.Г, Галактионов, А.С. Салов, В.Г. Теодорович и B. К. Портнов (56) Патент ЧССР N. 132479. кл. 21 а 18/01, 1969.

Авторское свидетельство СССР

N". 593281, кл. Н О? Н 7/20, 1978, (54) УСИЛИТЕЛЬ С ЗАЩИТОЙ ОТ ПЕРЕГРУЗКИ (57) Сущность изобретения: устройство содержит транзисторы 1. 2 разного типа проводимости. резисторы 3, 4, 5, пороговые

Изобретение относится к радиотехнике и может быть использовано в выходных усилителях, а также в усилителях мощности для обеспечения работоспособности схемы от воздействия перегрузки, Целью изобретения является повышение надежности путем увеличения быстродействия запирания транзистора выходного каскада при воздействии перегрузки.

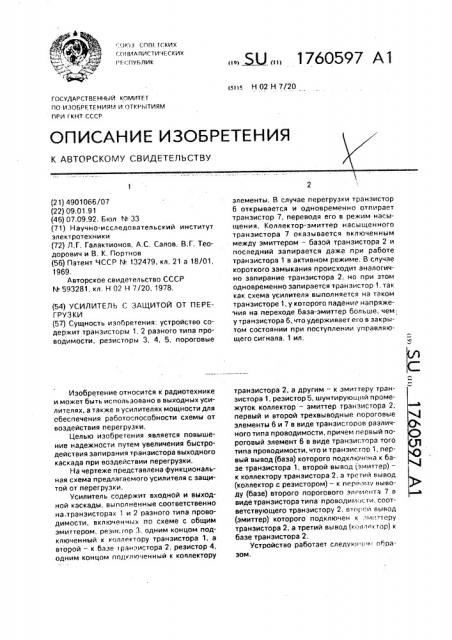

На чертеже представлена функциональная схема предлагаемого усилителя с защитой от перегрузки.

Усилитель содержит входной и выходной каскады. выполненные соответственно на.транэисторах 1 и 2 разного типа проводимости, включенных по схеме с общим эмиттером, резисГор 3. одним концом подключенный к коллектору транзистора 1, а второй — к базе транзистора 2, резистор 4, одним концом подключенный к коллектору.. Ж«1760597 А1 элементы. В случае перегрузки транзистор .6 открывается и одновременно отпирает транзистор 7, переводя его в режим насыщения. Коллектор-эмиттер насыщенного транзистора 7 оказывается включенным между эмиттером — базой транзистора 2 и последний запирается даже при работе транзистора 1 в активном режиме. В случае короткого замыкания происходит аналогично запирание транзистора 2, но при этом одновременно запирается транзистор 1, так как схема усилителя выполняется на таком транзисторе 1, у которого падение напряжения на переходе база-эмиттер больше, чем: у транзистора 6, что удерживает его s закрытом состоянии при поступлении управляющего сигнала. 1 ил. транзистора 2, а другим — к змиттеру транзистора 1, резистор 5, шунтирующий промежуток коллектор — эмиттер транзистора 2, первый и второй трехвыводные пороговые элементы 6 и 7 в виде транзисторов различного типа проводимости, причем первый пороговый элемент 6 в виде транзистора того типа проводимости. что и транзистор 1, первый вывод (база) которого подключена к базе транзистора 1, второй вывод (эмиттер)— к коллектору транзистора 2, а третий вывод (коллектор с резистором) — к первому выводу (базе) второго порогового эпеме ла 7 в виде транзистора типа проводим..кти. соответствующего транзистору 2, вто ой вывод (эмиттер) которого подключен к . мнттеру транзистора 2, а третий вывод (v.. л1актор) к базе транзистора 2.

Устройство работает следук» li . образом.

1760597

При отсутствии управляющего сигнала на входе усилителя транзисторы 1, 2, 6 и 7 закрыты, так как потенциал, образующийся на выходе делителя напряжения на резисторах 4 и 5 является закрывающим для транзистора 6 и соответственно для транзистора

7. При подаче положительногоуправляющего сигнала на вход усилителя транзисторы 1 и 2 открываются и на резисторе 4 появляется импульс напряжения, который является также запрещающим для транзистора 6.

Таким образом, при отсутствии перегрузки или короткого замыкания в нагрузке транзистор 6 и соответственно транзистор

7 все время закрыты и не оказывают влияния на работу усилителя.

В случае перегрузки транзистор 6 открывается и одновременно отпирает транзистор 7, переводя его в режим насыщения, Коллектор-эмиттер насыщенного транзистора 7 оказывается включенным между эмиттером — базой транзистора 2 и последний запирается даже при работе транзисто- ра 1 в активном режиме.

В случае короткого замыкания происходит аналогично запирание транзистора 2, но при этом одновременно запирается транзистор 1, так как схема усилителя выполняется на таком транзисторе 1, у которого падение напряжения на переходе база— эмиттер больше чем у транзистора 6, что удерживает его в закрытом состоянии при поступлении управляющего сигнала.Формула изобретения

Усилитель с защитой от перегрузки, содержащий входной и выходной каскады. выполненные на двух транзисторах разного

5 типа проводимости, включенных по схеме с общим змиттером, причем между силовыми выводами транзистора выходного каскада включен первый резистор, между коллектором транзистора выходного каскада и эмит10 тером транзистора входного каскада включен второй резистор, а между коллектором транзистора входного каскада и базой транзистора выходного каскада включен третий резистор, первый порого15 вый элемент, сигнальный вход которого подключен к коллекторутранзистора выходного каскада, а опорный — к базе транзистора входного каскада, отличающийся тем, что, с целью повышения надежности

20 путем увеличения быстродействия запирания транзистора выходного каскада при воздействии перегрузки, в него введен второй пороговый элемент, причем выход первого порогового элемента подключен к

25 сигнальному входу второго порогового элемента, опорный вход и выход которого соответственно соединены с эмиттером и базой транзистора выходного каскада, при этом падение напряжения между сигнальным и

30 опорным входами первого порогового элемента меньше, чем падение напряжения на переходе база — эмиттер транзистора входного каскада.