Устройство для измерения частоты гармонического сигнала

Иллюстрации

Показать всеРеферат

Изобретение может быть использовано для измерения частоты гармонического сигнала за время, меньшее периода измеряемого сигнала Целью изобретения является повышение точности измерения частоты гармонического сигнала Устройство содержит аналого-цифровой преобразователь 1. первый - третий регистры 2, 3, 4, сумматор 5, блок 7 определения модуля числа, блок 8 сравнения, первый блок 9 запрета, первый блок 11 деления, функциональный блок 13, генератор 15 импульсов, первый и второй блоки 16, 17 задержки, введение блока 6 умножителя на два. второго блока 10 запрета и блока 14 памяти позволяет повысить точность измерения. 1 ил,

СОЮЗ СОВЕТСКИХ

СОЦИДЛИСТИЧ Е СКИХ

РЕСПУБЛИК (si)s G 01 R 23/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

В (21) 4610397/21 (22) 25.11.88 (46) 15,09.92. Бюл. ¹ 34 (72) С.В.Васильев, С.А,Доронин, Н.Н.Дубовик и Л.П.Котенко (56) Авторское свидетельство СССР № 1118569, кл, G 01 R 23/00, 1985.

Авторское свидетельство СССР № 1691765, кл. G 01 R.23/00, 1988. (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЧАСТОТЫ ГАРМОНИЧЕСКОГО СИГНАЛА (57) Изобретение может быть использовано для измерения частоты гармонического сигИзобретение относится к измерительной технике и предназначено для измерения частоты гармонического сигнала за время меньшее периода измеряемого сигнала.

Целью, изобретения является повышение точности измерения частоты гармонического сигнала.

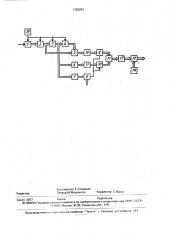

На чертеже представлена функциональная схема устройства для измерения частоты гармонического сигнала.

Устройство содержит аналого-цифровой преобразователь 1 (АЦП), первый — третий регистры 2, 3, 4 сдвига, сумматор 5, умножитель 6 на два, блок 7 определения модуля числа, блок 8 сравнения. первый и второй блоки 9, 10 запрета, пераый и второй блоки 11, 12 деления, функциональный блок

13, блок 14 памяти, генератор 15 импульсов, первый и второй блоки 16, 17 задержки.

Выход АЦП 1 соединен со входом первого регистра 2 сдвига, выход которого соединен со входом второго регистра 3 сдвига, Ä.,5U,, 1762254 А1 нала за время, меньшее периода измеряемого сигнала, Целью изобретения является повышение точности измерения частоты гармонического сигнала. Устройство содержит аналого-цифровой преобразователь 1, первый — третий регистры 2, 3, 4, сумматор

5, блок 7 определения модуля числа, блок 8 сравнения, первый блок 9 запрета, первый блок 11 деления, функциональный блок 13, генератор 15 импульсов, первый и второй блоки 16, 17 задержки, введение блока 6 умножителя на два. второго блока 10 запрета и блока 14 памяти позволяет повысить точность измерения. 1 ил, выход которого соединен с первым входом сумматора 5, второй вход которого соединен с выходом первого регистра 2 сдвига, а выход соединен через последовательно соединенные первый блок 16 задержки и блок

9 запрета с первым входом первого блока 11 деления, второй вход которого соединен с выходом второго регистра 3 сдвига через последовательно соединенные умножитель

6 на два. второй блок 17 задержки и блок 10 запрета, при этом выход второго регистра 3 сдвига соединен со входом блока 7 определения модуля числа, выход которого соединен со входом блока 8 сравнения, выход которого соединен с управляющими входами блоков 9, 10 запрета, а выход блока 11 деления соединен с входом функционального блока 13, выход которого соединен спервым входом второго блока 12 деления, второй вход которого соединен с выходом блока 14 памяти, причем выход генератора импульсов соединен с управляющим входом АЦП 1 и дополнительнь ми входами регистров 2, 3. 4 сдвига.

1762254

Устройство работает следующим образом. Контролируемое напряжение U поступает на аналоговый вход АЦП 1, который производит с периодом То преобразование мгновенных значений контролируемого напряжения в цифровой код. Этот код поступает и последовательно заполняет регистры 2, 3, 4 сдвига. Таким образом, в установившемся ре>киме в регистре 4 сдвига находится код U1, в регистре 3 сдвига— код Uz и в регистре 2 сдвига — код 03, где U1, Uz, V3 — мгновенные значения контролируемого напряжения в моменты времени t1, tz, тз соответственно. Содер>кимое первого регистра 2 сдвига U3 и третьего регистра 4 сдвига V1 суммируется в сумматоре 5 и результат через первый блок 16 задержки и блок 9 запрета поступает на первый вход первого блока 11 деления. Содержимое второго регистра 3 сдвига Uz после умножения на два в умножителе б поступает через второй блок 17 задер>кки и блок 10 запрета на второй вход первого блока 11 деления. Одновременно с этим сигнал Vz поступает в блок 7 определения модуля числа и после него в блок 8 сравнения,гдеIUzlсравнивается с.порогом (например, h = 0,1 ) Uzl, Uz— нормированное значение сигнала}.

Если lVz < h. то блок 8 сравнения выдает низкий потенциал и закрывает блоки 9, 10 запрета. В этом случае на выходах блоков

9. 10 запрета сохраняются коды предыдущих выборок, а на выходе устройства — код предыдущего результата. При:Uz(h блоки 9, 10 запрета пропускают коды U1+ 03 и

2Uz на входы блока 11 деления. Результат деления поступает в функциональный блок

13. где производится вычисление функции

U1+ U3 агссоэ — — — . Второй блок 12 деления

202 осуществляет операцию деления сигнала, поступившего с выхода функционального блока 13 на значение сигнала 2л То, записанного в блок 14 памяти. На выходе второго блока 1? деления получается значение

1 Ц1+ 03 частоты, равное f = ---.-arccos

2л1 3 202

Таким образом. эа счет введения дополнительной цепи, включенной параллельно цепи прохо>кдения си нала Uz и содер>ка10

?О

50 щей блок определения модуля числа, блок сравнения и два блока запрета. достигается возмо>кность принудительного прерывания поступления сигналов, приводящих к большим погрешностям измерения, на входы блока деления, что в конечном итоге приводит к повышению точности измерения частоты гармонического сигнала, Формула изобретения

Устройство для измерения частоты гармонического сигнала, содержащее аналогоцифровой преобразователь, выход которого через последовательно соединенные первый, второй и третий регистры соединен с первым входом сумматора, второй вход которого соединен с выходом первого регистра, а также блок определения модуля числа, первый и второй блоки задержки, блок сравнения, выход которого соединен с управляющим входом первого блока запрета, первый блок деления, функциональный блок, пр1 чем выход генератора импульсов соединен с дополнительным входом первого регистра и управляющим входом аналого-цифрового преобразователя, информационный вход которого является входом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения точности измерений, в него введены умножитель на два, второй блок запрета, второй блок деления и блок памяти. выход которого соединен с вторым входом второго блока деления, первый вход которого через функциональный преобразователь соединен с выходом первого блока деления, выход генератора импульсов соединен с дополнительными входами втооого и третьего регистров, выход второго регистра соединен с входами умножителя на два и блока определения модуля числа, выход которого через блок сравнения соединен с управляющим входом вто рого блока запрета, выход блока умножения на два через последовательно соединенные второй блок задержки и второй блок запрета соединен с вторым входом первого блока деления, первый вход которого через последовательно соединенные первый блок запрета и первый блок задержки соединен с выходом сумматора.

1762254

Составитель Е.Соловьев

Техред М.Моргентал Корректор С.Юско

Редактор

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101

Заказ 3257 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035. Москва, Ж-35, Раушская наб., 4/5