Измеритель постоянной времени апериодического звена первого порядка

Иллюстрации

Показать всеРеферат

Применение устройство относится к измерительной технике и автоматике и предназначено для использования в составе информационно-измерительных систем и автоматизированных систем управления технологическими процессами Сущность изобретения устройство содержит входную клемму (1) клемму запуска (2), блок управления (3) два аналоговых запоминающих блока (4 5), два интегратора (6,7), четыре масштабных блока (8-11) два блока вычитания (12 13) блок деления (14) индикатор (15) с соответствующими связями 2 ип

СОК З СОИ 1СхИХ

СО,!;1A! 114C П- Г: СКИХ

I Р С(1УГ ЛИ К

<.=1;.= С 01 R 29/02

ГОСУДАРСТР HHbii KE!iAl41ET

ПО ИЗОБРЕТЕНИЯЬЛ И 01КРЬ1Т ИЯМ

ЛРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕЛ:-НИЯ.

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1ф ) ° ) 1 ,() l

Л

О()=А е (21) 4789783/21

22 05.02.90

46 15.09.92. Бюл. M 34

71 Тернопольский филиал Львовского политехнического института им. Ленинского комсоt4ола (72) А.Н. Лупенко (56) Анкудинов А.И., Кравец В.И., Сем;енко

M.ß. Измерение коэффициента затухания экспоненциальных видеоимпульсов по реакции резисторно-емкостного четырехполгосника. "Измерительная техника". К. 7, 1986, с.40- 42.

Авторское свидетельство СССР

N. 1691782, кл. G 01 R 29/02. 1990. (54) И 3 M Е Р И T Е Л Ь П О (Т О Я Н Н О Й В Р Е M Е—

НИ АПЕРИОДИЧЕСКСГО ЗВЕНА ПЕРВОГО ПОРЯДКА

Изобретение относится к области измерительной техники и автоматики и предназначено для ис ".ользования в составе информационно-измерительных систем и автоматизированных систем управления технологическими процессами.

Известно устройство для измерения коэффициента затухания переходных процессов (величины, обратной постоянной времени), содержащее входную клемму, резистивно-емкостный четырехполюсник и индикатор (1}.

При этом в качестве измерителя временных интервалов ис .ользуется осциллограф, который не обеспе пвает высокой точности, быстродействия и PBToMBTèçàöè14 измерений.

Наиболее близким к заявляемому техническому решению являегся измеритель постоянной времени апериодического звена первого порядка (2), содержащее входную клемму, клемму запуска, аналоговый запоминающий блок, блок вычитания, блок

„., SU „„1762273 А1 (57) Применение: устройство относится к измерительной технике и автоматике и предназначено для использования в составе информационно-измерительных систем и автоматизированных систем управления технологическими процессами. Сущность изобретения: устройство содержит входную клемму (1), клемму запуска (2), блок управления (3), два аналоговых запоминающих блока (4,5), два интегратора (6,7), четыре масштабных блока (8-11), два блока вычитания (12,13), блок деления (14), индикатор (15) с соответствующими связями. 2 ил. деления, индикатор, интегратор 11 блок управления.

Недостатком известного устройства является ограниченная область прг1менения, т,к, оно служит для исследования только экспоненциально спадающих сигналов вида

Целью изобретения является расширение области применения за счет исследования как экспоненциально спадающих, так и экспоненциально возраста ощих сигнал о в.

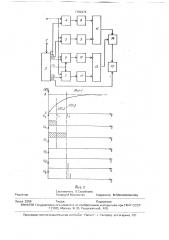

На фиг.1 представлена блок-схема 3мерителя постоянной времени апериоди:, ского звена первого порядка (в дальнейшем — измеритель); на фиг.2 приведены диаграммы, поясня1ащие принциll работы измерителя.

Измеритель содержит входную клемму

1, клемму 2 запуска, блок 3 управления, два

1762273 аналоговых запоминающих блока 4 и 5, двэ интегратора 6 и 7, четыре масштабь ых блока 8,9,10.11, два блока 12 и i3 вычитания, блок 14 деления. индикатор 15.

Входная клемма 1 соединена с сигнэль- 5 ными входами аналоговых запоминающих блоков 4 и 5 и интеграторов 6 и 7. Выходы аналоговых запоминающих блоков 4 и 5 через масштабные блоки 8 и 9 соответственно подключены к первому и второму входам 10 блока 12 вычитания, э выходы интеграторов

6 и 7 через масштабные блоки 10 и 11 соответственно подключень к первому и второму входам блока 13 вычитания. Выходы блоков 12 и 13 вычитания соединены соот- 15 ветственно с первым и вторым входами блока 14 деления, выход которого связан с сигнальным входом индикатора 15. Клемма 2 запуска подключена к входу блока 3 управления, первый, второй, третий. чет- 20 вертый и пятый выходы которого подключены к управляющим входам соответственно аналоговых запоминающих блоков 4 и 5, интеграторов 6 и 7 и индикатора !5, а шестой выход блока 3 25 управления связан с входами сброса интеграторов 6 и 7.

Принцип работы измерителя основан на проведении вычислительных операций с выходным сигналом апериодического звена 30 при подаче на его вход скачкообразного воздействия в виде единичной ступенчатой функции. В этом случае переходный процесс апериодического звена первого порядка описывается выражением: 35 1 ,/ 0(1)бХ+Т U(t2) (4) А—

U(t) =- А(1 - е ). где U(t) — зависимость напряжения (выходного сигнала) на выходе апериодического 40 звена первого порядка при подаче на его вход воздействия в виде единичной ступенчатой функции;

А = U() — установившееся (асимптотическое) значение выходного сигнала апериодического звена; t — время; г — постоянная 4 времени апериодического звена первого порядка.

Интеграл от выражения (1) на интервале времени от нуля до t равен:

f U(t)dt. о

В момент времени tt блок 3 управления формирует импульс Ui, который поступает на аналоговый запоминающий блок 4, который фиксирует значение напряжения

55 (1).

Интегратор 7 интегрирует входной сигнал в течение времени 0-tz так что в момент tz íà его выходе формируется величина (2) =А 1 — rU(t) 1 t

) U (t ) dt = Г A (1 — е ) dt =

4 /(, =А t — А т+А т е

Значения интеграла (2) для моментов времени t:= t t и t2 =- ty сос гэвя г систему уравнений:

f U(t)dt =А tq — r U(tq) о

3 0(t)dt =A tg — т U(tz). (3) о

Из первого уравнения системы (3) следует

После подстановки (4) во второе уравнение (3) в результате преобразований определяется искомая постоянная времени:

t2 т1. т1 f U(t ) dt — tz g U (t ) dt о о !

2 LI (t f1 — riiU 7!2 ) Выражение (5) лежит в основе работы предлагаемого измерителя, Измеритель работает следующим образом.

В момент включения измерителя блок 3 управления формирует импульс Ut (см. фиг,2) сброса, который устанавливает интеграторы 6 и 7 в нулевое состояние.

Входное напряжение U(t) (см. фиг.2}, которое представляет собой выходной сигнал апериодического звена первого порядка при подаче на его вход скачкообразного воздействия в виде единичной ступенчатой функции, через входную клемму 1 поступает на входы аналоговых запоминающих блоков

4 и 5 и интеграторов 6 и 7.

В момент времени t = 0 блок 3 управления "включает" интеграторы 6 и 7, подавая на них управляющие напряжения Оз и U4, соответственно (фиг,2). Интегратор 6 интегрирует входной сигнал в течение времени

0 — t> и запоминает значение интеграла

1762273 l2

f U(t)dt о

В момент времени tz блок 3 управления выдает управляющий импульс Uz (фиг.2), который поступает на аналоговый запоминающий блок 5, который фиксирует значение напряжения U(tz).

Выходные напряжения аналоговых запоминающих блоков 4 и 5 и интеграторов

6 и 7 поступают на входы масштабных блоков 8,9,10,11 соответственно. Коэффициенты передачи масштабных блоков

8,9,10, 11 соответственно пропорциональны интервалам времени KB= tz, K9=- tl, K10= т2, K11=- t1.

Величины т1 и т2 зависят от диапазона измерения постоянной времени. В интеграторах 6 и 7 они соответственно определяют верхний предел интегрирования.

С выходов масштабных блоков 8 и 9 сигналы поступают соответственно на прямой и вычитающий входы блока 12 вычитания, на выходе которого формируется значение знаменателя выражения (5), а с выходов масштабных блоков 10 и 11 соответственно на вычитающий и прямой входы блока 13 вычитания, на выходе которого формируется значение числителя выражения (5). Далее выходные си1нзлы блоков 12 и 13 вычитания поступают соответственно на входы "знаменатель" и "числитель" блока

14 деления, на выходе которого образуется сигнал, равный искомому значению постоянной времени.

В момент времени т блок 3 управления выдает импульс Ug (фиг,2) на индикатор 15, под влиянием которого индикатор 15 запоминает и отображает значение величины постоянной времени, поступающее на него с выхода блока 14 деления.

После этого в момент времени 16 блок 3 управления формирует импульс Uc сброса, который, поступая на входы сброса интеграторов 6 и 7, устанавливае их в исходное состояние. Цикл измерения завершился.

Длительность импульсов U; и 02, управляющих процессом фиксирования в аналоговых запоминающих блоках 4 и 5 должна быть значительно меньше интервалов tl и t2, чтобы эа время их действия входное напряжение U(t) практически оставалось неизменным, а, с другой стороны, они должны обеспечить запоминание значений U(tl) и

55 ц(тз) с достаточной точностью, также должно бь ть выдержано соотношение между моментами времени t2 t,.

Блок 3 управления представляет собой набор последовательно включенных формирователей импульсов и ждущих мультивибраторов.

Формула изобретения

Измеритель постоянной времени апериодическога звена первого порядка, содержащий блок управления, первый аналоговый запоминающий блок. первый интегратор, первый блок вычитания, блок деления, индикатор, входную клемл1у и клемму запуска, причем входная клемма подключена к сигнальным входам первого аналогового запоминзющего блока и первого интегратора, управляющие входы которых соединены соответственно с первым и третьим выходами блока управления. пятый выход которого соединен с управляю1цим входом индикатора, сигнальный вход которого соединен с выходом блоха деления, первый вход которого соединен с выходол1 первого блока вычитания, к входу блока управления подключена клемма запуска, о тл и ч а ю шийся тем, что. с целью расширения области применения за счет исследования как экспоненциально спадающих, так и экспоненцизльно возрастающих сигналов, внего введены второй ан,алоговый запоминающий блок, второй интегратор, четыре масштабных блока и второй блок вычитания, причем шестой выход блока управления подключен к входам сброса первого и второго интеграторов, выходы которых соответственно через третий и четвертый масштабные блоки подключены к первому и второму входам второго блока вычитания, выход которого соединен с вторым входом блока деления, входная клемма подключена к сигнальным входам второго интегратора и второго аналогового запоминающего блока, выходы первого и второго аналоговых запоминающих блоков соответственно через первый и второй масштабные блоки соединены с первым и вторым входами первого блока вычитания, управляющие входы в1 рого аналогового запоминающего блока и второго интегратора соединены соответственно с вторым и четвертым выходами блока управления.

1762273

Корректор M.Màêñèìèmèíåö

Редактор

Заказ 3258 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб.. 4/5

Производственно-издательский комбинат "Патент". г. Ужгород, ул.Гагарина, 101

U;. Рог. 2

Составитель Л.Стройкова

Техред М,Моргентал