Параллельный аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к аналого-цифровым устройствам. Цель изобретения - повышение точности и упрощение устройства. Аналого-цифровой преобразователь состоит из двух групп компараторов 1, 2, .. , 7, /4 первого дополнительного компаратора 8. резистивного делителя 9. кодирующего логического устройства 10. линейных дифференциальных усилитепей 11. 12, второго дополнительного компаратора 13, шин 14 15 опорных напряжений делитепя 9 напряжения шины 16 управления, дополнительных шин 17, 18 опорных напряжений, шины 19 общего входного сигнала и выходной шины 20. Первый вход компаратора 13 подключен к прямому выходу усилителя 11. а второй вход - к инверсному выходу усилителя 12. Входы кодирующего логического устройства 10 подключены к выходам компараторов 1 з.п. ф-лы 3 ил 20 о ю Jb о ю N3

СОЮЗ СОНЕTCKVIX

ССЧ ИДЛИС t ИЧГСКИХ

РЕСПУБЛИК

<с4)5 Н 03 M 1/36

ГOCY/tAPCTBEt tttblA КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ г КНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) 1481883 (21) 4641423/24 (22) 24.01.89 (46) 15.09,92. Бюл. M 34 (72) B.Н.Паулаускас и B.Â.Паулаускас (56) Авторское свидетельство СССР

hk 1481883, кл, Н 03 M 1/36, 1987, (54) ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ (57) Иэобретение относится к аналого-цифровым устройствам, Цель изобретения — повышение точности и упрощение устройства.

Аналого-цифровой преобразователь состоит иэ двух групп компараторов 1, 2...., 7, „., SU ÄÄ 1762409 А2 первого дополнительного компаратора 8. реэистивного делителя 9, кодирующего логического устройства 10, линейных дифференциальных усилителей 11, 12, второго дополнительного компаратора 13, шин 14.

15 опорных напряжений делителя 9 напряжения шины 16 управления, дополнительных шин 17, 18 опорных напряжений, шины

19 общего входного сигнала и выходной шины 20. Первый вход компаратора 13 подключен к прямому выходу усилителя 11, а второй вход — к инверсному выходу усилителя 12.

Входы кодирующего логического устройства 10 подключены к выходам компараторов.

1 э.п. ф-лы. 3 ил, 17624С9

Изобретение относится I< аналого-цифровым устройствам и может бы ь использовано в системах обработки и передачи информации и является усовершенствованием устройства, описанного в авт, св. N

1481883.

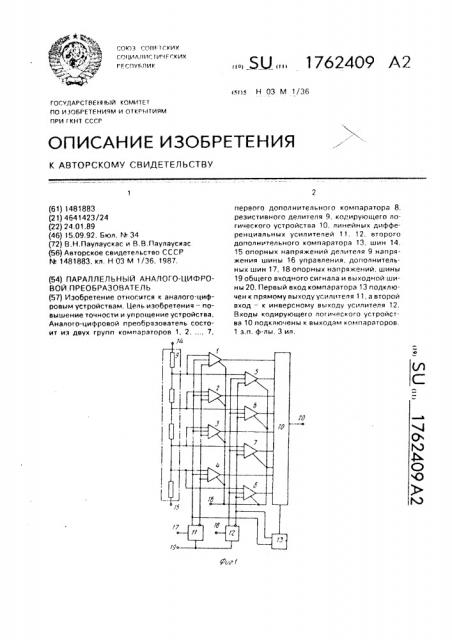

Целью изобретения пвляется повышение точности и упрощение устройства, На фиг, 1 приведена блок-схема параллельного аналого-цифрового преобразователя (АЦП); на фиг, 2 — диаграммы входных и опорных напряжений, где по оси абсцесс отложено входное напряжение, разбитое на четыре рабочих интервала, а по оси ординат — опорные напряжения. Прямые наклонные линии представляют прямые (Un>) и противофазные (Unyj напряжения, явля ощиеся интервальными функциями входного аналогового напряжения, Уровни опорных напряжений обозначены горизонтальными линиями, опорные напряжения компараторов 1...4 обозначены Upni...Upn4 соответственно, а шины опорных напряжений -UilEr-1 и Вверг. На фиг, 3 приведена блок-схема компаратора напряжения на три входа.

Аналого-цифровой преобразователь (фиг. 1) состоит из двух групп компараторов

1 — 7, первого дополнительного компаратора

8. реэистивного делителя 9, кодирующего логического устройс ва 10, линейных дифференциальных усилителей 1 i, 12, второго дополнительного компаратора 13, шин 14, 15 опорных напряжений дели1еля 9 напряжения, шины 16 управления, доголнительных шин 17, 18ог ор-1ых напряжений 0яггз, Ояегл, шины 19 общего входного сигнала и выходной шины 2С.

Схема кам вратop приведенная на фиг. 3, включает Входную электрическую цепь, состоящую из транзисторов 21, 22, 23, построенную на базе Дифференциальной пары транэи<ггоров 22. 23, ключ 24 тока, источник 25 тока, шину 26 пи ания, входы

27, 28, 29, вход стробирования 3О, выход 31, транзисторы 32 l4 33, резисторы 34 и 35.

Устройство работае следующим образом.

Входной диапазон аналогового сигнала разбит на четыре рабочих интерва lOB (Uol, 0о2), (Uo2 Uo3), (Ооз, Uo4), (- ол, Uo5) (фИГ. 2), Каждый рабочий ин, арвал входи.-.. ГО сигнала относится к одной . руопе входов:, 0 lnBpBторов, К первому интервалу 01HÎcятся те входы компараторов, которые подключены к противофаэному Выходу дифференциаг ьного усилителя 11, а к прямому выходу егo подключень1 те ко lnBpBTOpbl, которые относятся K треть= му интервал / ВходноГО сиГнала. Разница входных напряжений между сигнальными входами Одно о компаратора этой группы на первом или на третьем интервале не менее напряжения. равного напряжению второго интервала. Аналогично, разница входных напряжений между сигнальными входами второй группы компараторов не менее напряжения, равного напряжению третьего интервала. Ширина интервала выбирается такой величины, чтобы на рабочих интервалах компаратора его один сигнал вход был всегда закрыт.

Если прямой или противофазный сигнал на входах компаратора превышает опорное напряжение подключенного к опорному входу компаратора, то на выходе компаратора напряжение соответствует логической единице. При величине входного сигнала, определяемого первым или вторым интервалами, выходной унигарный код на

Выходе компаратора представляет в обратном кОДВ. Если ВХОДной сиГнал нахОДится В диапазоне, определяемом третьим или четвертым ",нтервалами, то выходной код на

ВЫХОДЕ КЗМПаРатОРОВ ПРЕДСтаВЛЯЕтСЯ ПРЯмым кодам. Для опознавания прямого или обратного кода применен компаратор 13

Шины U»p, .12пр, 01пф, 02пф представ ляют выходы линейных дифференциальных усилителей 11, 12. Узлы пересечения прямых линий опорных напряжений (Uoni, Uon2, 0опз, Upn4) i4 наклонных линии BHBлОГОВых напряжений (Ulnp, U2np, 0»ф, U2ng) указы:аBlю0т T нHа B э3нHаBчuеeнHиHя n нHаBпnрpяnж еBнHlи4lй 4 ((в B lкlо0о0рpд lи4нHаBтTной плоскости), при которых срабатывают компараторы. Проекции этих узлов на оси абсцисс предс авляют noроговые уровни квантования. Например, разница напряжений пороговых уровnåé. представляемых проекцИямИ УЗЛОВ (Uon4 1пф) и l,Uonl, U2nd>j

HB оси абсцисс является шагом YBBHT0âBHèÿ между четвертым l1 пятым компара Горами, т.е. между последним компаратором первой

Группы и первым компаратором второй

Группы и представляет пятый по порядку шаг квантования. Разница напряжений на входной оси (оси абсцисс) аналогового напРЯжениЯ межДУ пРоекЦиЯми Узлов (Upn4

1Лпф) И {Uon4, Uinp) ЯВЛЯЕТСЯ ДЕВЯТЫМ ШаГОМ квантования, Каждый компаратор может срабBтыBВTь TОлько От пряMОГО Unр иflи ОT противофазного Опф аналогового напряже-:ия. Например, компараторы первой груп:;ы будут работать только в интервалах входных напряжений (Uo2 Uol) l4 (Оо4 Uo3).

В интервале (Upz-Uoi) напряжений компараторы будут работать от противофазного

НаПРЯжЕНИЯ 01пф, а В ИнтЕРВВЛЕ (Uo4 — Uo3)—

0Т ПРЯМОГО НаПРЯжЕНИЯ 01пр, Пример, Пусть Вхсдной сигнал будет

Ux> (фиг. 2), тогда выходы компараторов будут Q, =-- С, 02 - О, 03 =- i, 04 = 1, Gs -- 1, Ов =

1762409

"1,От=1, Ов=1, О<э=:, де Qi — код выход;".

I-ro компаратора. Выходы Q!, Qg, Оз. Ол относятся к первой группе компаратаров, а выходы Ов, QI;, От, Ов — ко второй группе компараторов, включая первый дополнительный компаратор, Этот код является инверсным и представляется как Ов. Qr, Ов, Ов, Q4, Оз, Ор, О< = 11111100 (младшие разряды с правой стороны), Прямой унитарный кад будет 00000011. Кроме того, признак (О<з) представляет дополнительную «нформацию о том, что выходной код является кодом старших или младших разрядов. При О<э =

-лог. "1" старшие разряды (8 разрядов) необходимо представить лог, "0 в прямом коде. Если 01З = лог. "0", то младшие разрялы (8 разрядов) унитарного кода неабход«ма в прямом выходном коде представ«ть в виде лог, "1".

Пусть на входе преобразователя будет

0х2, тогда Q < =- 1, Qy = 1. Оз =- 1, 01 =- 1, Ов ==О, Ов = О, Ов = 1, О<э-- 1, = О. тогда выходной код старших разрядов будет

ОвОвОтОв01020зО < == 0011111, Ка; видна, при формировании када сгаргвих разрядов разряды кода в каждой группе армиру<отся в обратном порядке. В остальном этот преобразователь работает как типовой АЦП параллель«ага действ« .

Погрешность матрицы делителя напряжен« зав«сит от количес ва рез» старав в цепс:ке. Чем больше резистopo! -,ем бал:-.ше погрешность, а чем больше погрешность, тем хуже дифференциальная и интегральная нелинейность. Б предлагаемом устройстве кол«чество реэ«старое в 4 раза меньше числа шагов квантования, поэтому уменьшается брак па интегральной и дифференциальной нелинейности, Кроме того, эа счет уменьшения коли <ества резисторов и ксмлпараторав в два раза, т.к, количество резисторов матрицы делителя напряжения в четыре раза, а количество компараторов в два раза меньше числа шага квантования уменьшается площадь кристалла для монолитного АЦП или уменьшается обьем и вес АЦП для дискретного исполнения.

©ормула изобретения

1. Параллельный аналога-цифровой преобразователь по авт. св, М 1481883, о тл и ч а ю шийся тем, что, с целью повышения точности и упрощения устройства, в него введены два дополнительных компаратара, первый и второй линейные дифференциальные усилители, прямой вы5

25 .3 0

40 ход первого «3 которых являегся ш«най прямого с«гнала, а:<няерснь<й выход второго линейно. о дифференциального усилителя является шиной противофазного входного сигнала, первые входы первого и второго дифференциальных усилителей обьединены и являются шиной обще;о входного c«гнала, вторые входы - соответственно первой и второй дополнительными шинами опорных напряжений, при этом третьи âõîды компараторов первой группы обьедине rtI.-! !1 подклю <ены к «нверсно<лу выходу первого линейного дифференциального усилителя, первый вход первого дополнительного кампаратора сбьединен с вторым входом одного иэ компараторов первой группы, второй вход — с вторым входом од. Ого из компаратарав второй группы, третий вход абьединен с третьими входами ко паратаров в арой руппы «подключен к прямому вь;ходу второго линейного диффе ренц«альнofа усил«теля, а вход стробирован«я является управляющей шиной, прямой выход первого и инверсный выход второго ли.<ейных дифференциальных усилителей подключены соответственно к перва му: в га рак<у входам второго ..: ПСЛ:: т.".i OÃO Ка -;ПаРатГ Оа ВЫХОД КОТОООГО «вь! ход пер воi и дапал и «тРЛ ьнсгс кампаратора соединены соответственно с первым и вторым дополнительными входами кадирующего логического устройства.

2. Преобразователь по и. 1, о т л и ч а юшийся тем, чта он содержит первый дополнительный кампаратор и каждый кок<паратор первой и второй групп выполнен на пяти транзисторах, двух резисторах, первые выводы которых обьединены и подключены к шине питания, переключателе тока и источнике ТОка, выход КоТоро!о подключен к входу переключателя тока. управляющий вход которого являе1ся входам стробирования компаратора, прямой выход подключен к эмиттерам первого, второго «третьего транзисторов, базы которых являются соответственна третьим, вторым «первым входами компаратара. а коллекторы первого и второго транзисторов обьед«нены и подключены к базе четвертого и кал«ектару пятого Tpà<.3«ñòoðoÿ «ятаро лу выводу первого резистора который I:Rë pòñë выхадом компаратара, второй вывод второго резистора соединен с базой пятого тРаНЗИСтОРа, КОЛЛРКтаРаМИ ЧЕ<ВЕРтаГО И третьего транз«старая, базы последних обьединень . и саед Ilp!

1762409

&02

+05

Составитель В.Солодова

Техред M.Mîðãåíòàë

Корректор А.Долинич

Редактор Н,Каменская

Производственно-издательский комбинат "Патен ", г. Ужгород, ул Гагарина. 1О!

Заказ 3265 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5