Преобразователь кодов

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике, информационно-измерительной и вычислительной технике и может быть использовано при преобразовании кода с основанием 2 в двоичный код, а также при вычислении ряда элементарных функций. Цель изобретения - повышение достоверности преобразования кодов. В преобразователь кодов, содержащий регистр 1, умножитель 2, вход двоичной константы преобразователя 3, первый управляющий вход преобразователя 4, коммутатор 5, второй управляющий вход преобразователя б, накапливающий сумматор 7, вход преобразователя 8. выход преобразователя 9, дополнительно введены первая 10 и вторая 11 группы элементов И, блок контроля кода 12 с выходом 13. Кроме того, блок контроля кода содержит п элементов равнозначности 14 и д-входовый элемент И 15 с выходом 16. 1 з.п. ф-лы, 2 ил., 1 табл.

СОК)3 СОВЕТСКИХ

COIIÈÀJIlCTVIVFCÊÈÕ

РЕСПУБЛИК (st)s Н 03 M 7/12

ГОСТ/1ДРСТВЕН1 АЛЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ I КНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ - — 4 ()с

Ю

Ф

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4765085/24 (22) 04.12.89 (46) 15.09.92, Бюл. N 34 (71) Винницкий политехнический институт (72) Н.А.Квитка, В.П.Кожемяко, А.И. Короновский и В.С. Стратиенко (56) Авторское свидетельство СССР

М 1283979, кл. Н 03 M 7/12, 1985.

Авторское свидетельство СССР

М 1462487, кл, Н 03 M 7/02, 1986, (54) ПРЕОБРАЗОВАТЕЛ Ь КОДОВ (57) Изобретение относится к автоматике, информационно-измерительной и вычислительной технике и может быть использовано при преобразовании кода с основанием 2 в двоичный код, а также при вычислении ряда. SU 1762410 А1 элементарных функций. Цель изобретения— повышение достоверности преобразования кодов. В преобразователь кодов, содержащий регистр 1, умножитель 2, вход двоичной константы преобразователя 3, первый управляющий вход преобразователя 4, коммутатор 5, второй управляющий вход преобразователя 6, накапливающий сумматор 7, вход преобразователя 8, выход преобразователя 9, дополнительно введены первая 10 и вторая 11 группы элементов И, блок контроля кода 12 с выходом 13, Кроме того, блок контроля кода содержит п элементов равнозначности 14 и g-входовый элемент И 15 с выходом 16. 1 з.п. ф-лы, 2 ил„

1 табл.

1762410

Изобретение относится к автоматике, информационно-измерительной и вычислительной техник для преобразования кода с основанием у 2 в двоичный код, а также может быть использовано при вычислении 5 ряда элементарных фучкций.

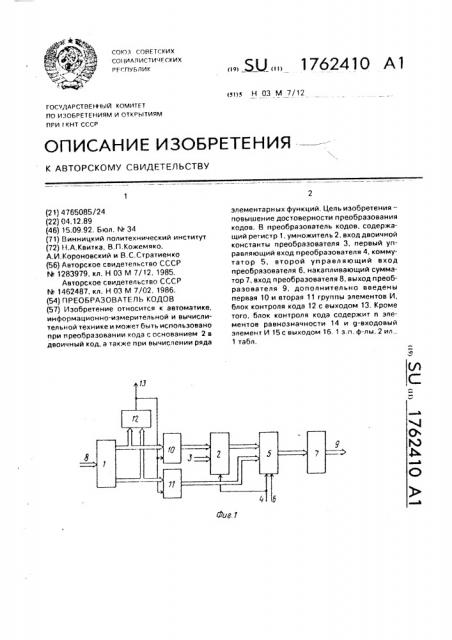

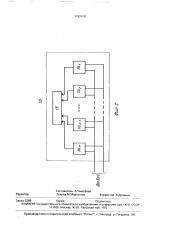

Цель изобретения — повышение достоверности преобразования кодов, На фиг, 1 и 2 приведены структурная схема предлагаемого преобразователя и 10 блока контроля.

Преобразователь содержит регистр 1, умножитель 2, вход 3 двоичной константы, первый управляющий вход 4, коммутатор 5, второй управляющий вход 6, накапливаю- 15 щий сумматор 7, выход 8 преобразователя, первую группу элементов И 9, вторую группу элементов И 10, блок контроля 11, выход блока контроля 1?, выходной элемент И 13, п элементов "равнозначность" 141-14<. 20

Работа преобразователя основана на следующем алгоритме.

Входной 2"-разрядный код N с основанием 2 изображается в виде а2(2 + а1(2 ) + ад{ 2 ) + а, (1 2 )

+а(2) +„,+а (<2)" (1)

Веса разрядов кода с основанием У 2 составляют последовательность степеней ос- 30 нования .,1б i 2,15,8 2,Б,4 "2 4,2 <2.2,1

V2 1 /2 1

2 2 4 4 "

Из выражения (2) следует, что четные степени являются весами аэзрядов двоичного кода, а нечетные - весами двоичного кода, умноженными на 2 . С учетом этого входной код N, предстэвляюший выражени(1). 4

n — 1

1 — 1

N= 2,>, ai2 2 +

I = — и+1 л — 2

+ 2 } 2 (),)

1 =- — и где аь э е (0,1) и являются цифрами двоична-кодированной системы счисления с основанием У2, а, I, ) дл 2п-разрядных 50 чисел принимают значение

I(- (-и+1, ..., -3, -1,1,3,4, ..., n-1):

Jg (n —...„-4,-2,0,?,4, .„, п-2), Первый член формулы (3) составляет сумму нечетных разрядов кода й, э второй член — 55 сумму четных разрядов этого же кода.

Выражение (3) содержит две двоичные части, позволяет изображать 2п-аазрядные двоичные коды. и таким образом, является

Предложенное кодирование позволяет довольно просто и оперативно осуществить контроль кода с основанием 2, подлежащего преобразованию в двоичный код и тем самым повысить достоверность такого преобразования, Признаком искажения комбинации яв. яется нечетность единиц в паре разрядов комбинации, Пример преобразования кода с основа/ нием у 2 в двоичный код для числа 10+ 10

У 2 =- 11001100. (У 2 ) = 11000.0001(2) приведен в таблице 1. код с основанием 1 2 исходного числа 11001100

Четные разряды кода исходного числа 1010

Нечетные разряды кода исходного числа

Двоичныйэквивэлент числа у 2 1.01101

Произведение нечетных разрядов кода исхаднога числа на двоичный эквивалент числа < 2 1110.0001

Сумма четных разрядов кода исходного числа и произведения 1 1000.0001

Необходимо отметить, чта в таблице четные и нечетные разряды кода исходного числа представлены в соответствии с выражением (4) в "сжатом" виде.

Преобразователь кодов с основанием

У 2 в двоичный код работает следующим образом.

Vîä с основанием 2 исходного числа (11001100) записывается в регистр 1. Поскольку к выходам нечетных и четных разрядов регистра 1 подсоединены соответственно первые и вторые входы элементов "Равнозначность" 151-15п, входящих в состав блока 10 контроля кода (см. фиг. 2) и осуществляющих контроль четности кода пары разрядов, то при наличии в регистре 1 искаженной кодовой комбина1010 исходным в разработке преобразователя када с основанием у 2 в двоичный код,если в выражении (3) в качестве разрешенных кодовых комбинаций в двоична-кодированной системе счисления с основанием 2 для кодирования чисел использовать лишь те, которые содержат одинаковые двоичные части, та любая кодовая комбинация в коде с основанием У 2 будет содержать четное количество единиц, располаженны парами, а выражение (3) примет вид

n/2 — 1

М =-(2+1) g a;2 2 (4) ! = — n/2

1762410 ции (11 10 11 01) на выходе и-вхадавого элемента И 14, а значит и на вторых входах первой и второй группы элементов И 11 и

12, появится нулевой потенциал, запрещающий дальнейшее преобразование информации, преобразование заканчивается, В том случае, когда в регистре 1 присутствует искаженная кодовая информация (11 00 11

00), то на выходе элемента И 14 возникает единичный потенциал, разрешающий поступление информации на умножитель 2 и коммутатор 3. С приходом по первому входу управления 8 управляющего сигнала происходит запись четных разрядов исходного кода (1010) из регистра через вторую группу элементов И 12 и коммутатор 3 в накапливающий сумматор 4 и одновременно с этим запись нечетных разрядов исходного када (1010) из регистра 1 через первую группу элементов И 11 в регистр мнажимаго умножителя 2 и приближенного двоичного эквивалента числа 2 (1,01101) в регистр множителя, умножителя 2. В результате умножения на выходе умножителя появляется двоичный код (1110.0001), который с приходом управляющего сигнала на вход 9 через коммутатор 3 поступает на вход накапливающего сумматора 4, где происходит его сложение с кодом четных разрядов исходнога числа (1010). После выполнения операции сложения на выходе 9 преобразователя кодов появляется двоичный кад (11000.0001), который представляет собой результат преобразования кода (11001100) с основанием 2 исходного числа в двоичный кад. Следует отметить, что разрядная сетка накапливающего сумматора 4 содержит 2п- 1 разрядов, из которых (и -1) разрядов используется для хранения целой части, а и разрядов дробной части двоичного кода.

Формула изобретения

1, Преобразователь кодов с основанием

Г

2 s двоичный код, содержащий регистр, входы котора Га я ВJ1 я ьа T ся и >1фа (>Mà öèîíí ûf1è входами преобразователя, умнажитель. входы множителя которого саед IHpíû с входам двоичной константы преобразователя, 5 управляю.ций вход умножителя соединен с первым управляющим входам преобразователя, а выход соединен с первой группой лнформацианных входов коммутатора, первый и второй управляющие входы которого

10 являются соответственно первым и вторым управляющими входами преобразователя, выход коммутатора соединен с входом накапливающего сумматора, выход которого является выходом преобразователя, о т л и15 ч - ю шийся тем, что, с целью повышения достоверности преобразования, в него введены первая и вторая группы элементов И и блох контроля на четность кода пары разрядов комбинации, первая группа входов ка20 тарого и первые входы элементов И первой группы соединены с выходами группы нечетных разрядов регистра, выходы группы четных разрядаз которого соединены с первыми входами элементов И второй группы и

25 второй группой входов блока контроля кода на четнасть када пары разрядов комбинации, выход которого является контрольным выходам преобразователя и соединен с вторь ми входами элементов И первой и второй

30 групп, выходы которых соединены с входами множимого умножителя и второй группой информационных входов коммутатора соответственно.

2. Преобразователь по и. 1, о т л и ч а ю35 шийся тем, что блок контроля на четность кода пары разрядов комбинации кода содержит и элементов РАВНОЗНА 1НОСТЬ и

0-входовый элемент И, выход KQT(рого является контрольным выходом блока, а входы

40 и-вхадового элемента И соединены с выходами соответствующих элементов РАВНО3 НА4 НОСТЬ, первые и вторые входы которых соединены с первым l1 вторым входами блока соответственна.

1762410

Составитель А,Тимофеев

Техред M.Mîðãåíòàë Корректор А.Долинич

Редактор

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101

Заказ 3265 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб.. 4/5