Сумматор по модулю три

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в устройствах, функционирующих в системе остаточных классов. Цель изобретения - увеличение быстродействия. Сумматор содержит два элемента И, два элемента сложения по модулю два, три элемента ИЛИ-НЕ. Сумматор по модулю три представляет собой комбинационную схему и обеспечивает сложение исходных двухразрядных операндов по модулю три. 1 ил., 1 табл.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (39) (ФЦ (ss)s G 06 F 7/49

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4877295/24 (22) 24.10.90 (46) 23.09.92. Бюл. N. 35 (72) И,Е.Анкудинов, А.M,Çûêîâ, С.А.Удинцев и Н.Н.Шипилов (56) Авторское свидетельство СССР

N 1564613, кл. G 06 F 7/49, 1988, Авторское свидетельство СССР

М 1654812, кл. G 06 F7/49,,1989.

Изобретение относится к вычислительной технике и может быть использовано в устройствах, функционирующих в системе остаточных классов.

Известен сумматор по модулю три, содержащий четыре элемента И, два элемента сложения по модулю два и три элемента

ИЛИ.

Недостаток известного устройства— большие аппаратурные затраты и низкое быстродействие, обусловленное значительной логической глубиной схемы.

Наиболее близким к изобретению по технической сущности является сумматор по модулю три, содержащий два элемента сложения по модулю два и два элемента И, причем входы первых элементов И и сложения по модулю два соединены с входами младших разрядов операндов сумматора, входы вторых элементов И и сложения по модулю два соединены с входами старших разрядов операндов сумматора.

Данное устройство является комбинационной схемой, обеспечивающей сложе(54) СУММАТОР ПО МОДУЛЮ ТРИ (57) Изобретение относится к вычислительной технике и может быть использовано в устройствах, функционирующих в системе остаточных классов, Цель изобретения— увеличение быстродействия. Сумматор содержит два элемента И, два элемента сложения по модулю два, три элемента

ИЛИ-НЕ. Сумматор по модулю три представляет собой комбинационную схему и обеспечивает сложение исходных двухразрядных операндов по модулю три. 1 ил., 1 табл. ние исходных двхуразрядных операндов по модулю три.

Недостатком этого сумматора является

его низкое быстродействие, обусловленное большой логической глубиной схемы, Цель изобретения -увеличение быстродействия сумматора по модулю три, Поставленная цель достигается тей, что 4 в сумматор по модулю три, содержащий два Ch элемента сложения по модулю два и два элемента И, причем входы первых элемен- С) тов И и сложения по модулю два соединены (Л с входами младших разрядов операндов сумматора, входы вторых элементов И и сложения по модулю два соединены с входами старших разрядов операндов сумматора, введены три элемента ИЛИ вЂ” НЕ, входы первого из которых соединены с входами старших и младших разрядов операндов сумматора, а выход — с первыыми входами второго и третьего элементов ИЛИ вЂ” НЕ, вторые входы которых соединены с выходами соответственно первого и второго элементов

И, третьи входы — с выходами соответствен3

1764050 но второго и первого элементов сложения по модулю два, а выходы — c выходами соответственно младшего и старшего разрядов результата сумматора.

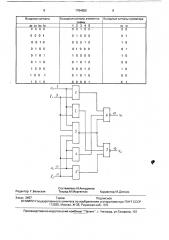

Использование указанных элементов с соответствующими связями обуславливает уменьшение глубины схемы, приводящее к повйшению быстродействия сумматора по модулю три, На чертеже представлена схема сумматора по модулю три.

Сумматор содержит элемент И 1, элемент 2 сложения по модулю два, элемент

ИЛИ вЂ” НЕ 3, элемент 4 сложения по модулю два, элемент И 5, элементы ИЛИ вЂ” НЕ 6, 7, входы разрядов операндов 8 — 11, выходы разрядов результата 12, 13.

Входы элемента И 1 и элемента 2 сложения по модулю два соединены с входами младших разрядов операндов сумматора, входы элемента 4 сложения по модулю два и элемента

И 5 соединены с входами старших разрядов операндов сумматора. Входы элемента

ИЛИ вЂ” НЕ 3 соединены с входами старших и младших разрядов операндов сумматора, а его выход — с первыми входами элементов

ИЛИ вЂ” НЕ 6, 7. Вторые входы элементов

ИЛИ вЂ” HE 6, 7 соединены с выходами соответственно элементов И 1, 5. Третьи входы элементов ИЛИ вЂ” НЕ 6, 7 соединены с выходами соответственно элементов 4, 2 сложения по модулю два 4, Выходы элементов

ИЛИ вЂ” НЕ 6, 7 соединены с выходами соответственно младшего и старшего разрядов результата сумматора.

Сумматор работает следующим образом.

Суммируемые операнды А и В задаются двухразрядными кодами А = а а, В = blab>, где а> и b> — младшие разряды операндов; а и Ь вЂ” старшие разряды операндов.

В соответствии с выбранным модулем Р

= 3 каждый операнд может принимать значения "0"{00), "1 "(01), "2 "(10). Функционирование сумматора по модулю три иллюстрируется таблицей, в которой приведены выходные сигналы всех элементов схемы для всех возможных значений входных сигна5 лов.

В качестве базового объекта выбран прототип изобретения.

Преимуществом изобретения перед прототипом является более высокое быст10 родействие. Указанное преимущество заключается в следующем. Логическая глубина схемы прототипа составляет три вентиля Оо=З, а логическая глубина схемы предлагаемого устройства — G =2, Следова15 тельно, выигрыш в быстродействии составляет

Go «3

G> 2

= — =1,5

Таким образом, предлагаемый сумма20 тор по модулю три обладает в 1,5 раза более высоким быстродействием, чем прототип.

Формула изобретения

Сумматор по модулю три, содержащий два элемента сложения по модулю два и два

25 элемента И, причем входы первых элементов И и сложения по модулю два соединены с входами младших разрядов операндов сумматора, входы вторых элементов И и сложения по модулю два соединены с вхо30 дами старших разрядов операндов сумматора, отл и ч а ю шийся тем, что, с целью увеличения быстродействия, он содержит три элемента ИЛИ-НЕ, входы первого из которых соединены с входами старших и

35 младших разрядов операндов сумматора, а выход — с первыми входами второго и третьего элементов ИЛИ вЂ” HE, вторые входы которых соединены с выходами соответственно первого и второго элементов И, третьи вхо40 ды — с выходами соответственно второго и первого элементов сложения по модулю два, а выходы — с выходами соответственно младшего и старшего разрядов результата сумматора, 45

1764050

Составитель И.Анкудинов

Техред М,Моргентал Корректор М.Демчик

Редактор Г.Бельская

П роизводственно-издательский комбинат "Патент", г. Ужгород, ул, Гагарина, 101

Заказ 3457 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5