Устройство для обработки векторов

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 G 06 F 15/347

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР у

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Д

О (Я

СО (21) 4872539/24 (22) 19,07.90 (46) 23.09,92. Бюл. N 35 (71) Московский институт радиотехники, электроники и автоматики (72) Н.Н.Евтихиев, E.Â.Åìåëèí, Д.Э.Краснов, И.В,Ланин, Е,Г.Литвинов и В.Л.Таубкин (56) Авторское свидетельство СССР

¹ 1256041, кл, G 06 F 15/20, 1985.

Европейский патент N. 0049039, кл, G 06 F 15/347, опублик. 1984. (54) УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ВЕКТОРОВ (57) Изобретение относится к вычислительной технике и может быть использовано в качестве специализированного вычислителя в системах обработки данных, Цель изо„„Я2„, 1764058 А1 бретения — повышение быстродействия при выполнении над векторами операций типа и п (т(аь b) а Ьь а также расширение

i=О I=0 функциональных возможностей за счет вып числения функции g„f(ai bi), Устройство coi=0 держит два входных регистра 1, 2, четыре буферных регистра 6, 7, 10, 11, три мультиплексора 4, 5, 12, арифметико-логический блок 3, умножитель 9, сумматор единиц 8, сумматор 13, регистр результата 14, регистр сдвига 15 и регистр выбора функции 16.

Достижение цели обеспечивается за счет новой структуры устройства, позволяющей организовать конвейерную обработку элементов векторов, 1 ил.

1764058

Изобретение относится к вычислительной технике и может быть использовано в качестве специализирован ного вычислителя в системах обработки данных.

Известно устройство, содержащее матрицу ячеек, каждая из которых имеет элементы И, ИЛИ, НЕ, триггеры, и предназначенное для выполнения операцИи сжатия векторов. Недостатком известного устройства являются узкие функциональные возможности, которые не позволяют выполи 2 и нять. операции (f (аь Ь )), а > bi u

i =0 i =0 п

g f (аь b;), где а и bi — соответствующие

i =0 элементы первого и второго векторов, имеющие размерность N; f (аь bi) — произвольная простейшая функция двух аргументов;

Zi — функция бинарной корреляции двух ве кторов.

Наиболее близким к изобретению является устройство для обработки разряженных векторов, содержащее девять буферных регистров, арифметико-логический узел, узел логики управления, сдвиговый регистр и счетчик. Недостатком указанного устройства является его малое быстродействие.

Цель изобретения — повышение быстродействия при выполнении над векторами

tl

2 операций типа,, (f(ai bi)), а . Ь, а

i =0 i 0 также расширение функциональных возможностей за счет вычисления функции и ,>,,f (ai, bi), i =0

Поставленная цель достигается тем, что в устройство для обработки векторов, содержащее первый. и второй входные регистры, регистр выбора функции, арифметико-логический блок, четыре буферных регистра, регистр результата и регистр сдвига, первый и второй выходы которого соединены соответственно с управляющими входами первого, второго, третьего и четвертого буферных регистров, причем входы первого и второго операндов устройства соединены соответственно с информационными входами первого и второго входных регистров, выходы которых соединены соответственно с входами первого и второго операндов арифметико-логического узла, вход кода операции устройства соединен с входом регистра выбора функции, выход регистра результата соединен с выходом результата устройства, первый вход синхронизации которого соединен с входом синх5

55 ронизации первого входного регистра, вход запуска регистра сдвига и вход синхронизации второго входного регистра соединены с вторым входом синхронизации устройства, управляющий вход регистра результата соединен с третьим входом регистра сдвига, введены три мультиплексора, сумматор единиц, умножитель и сумматор, причем информационный вход регистра результата соединен с выходом сумматора, входы младших разрядов первого слагаемого которого соединены с выходом первого мультиплексора, первый и второй информационный входы которого соединены соответственно с выходом значащих разрядов третьего и выходом четвертого буферных регистров, информационный вход третьего буферного регистра соединен с выходом умножителя, первый и второй информационные входы которого соединены соответственно с выходами первого и второго буферных регистров, информационные входы которых соединены соответственно с выходами второго и третьего мультиплексоров, первые информационные входы которых соединены соответственно с восходами первого и второго входных регистров, первый выход регистра выбора функции соединен с входом задания режима работы арифметикологического узла, выход которого соединен с вторыми информационными входами второго и третьего мультиплексоров и входом сумматора единиц, выход которого соединен с информационным входом четвертого буферного регистра, управляющие входы второго и третьего мультиплексоров соединены с вторым выходом регистра выбора функции, третий выход коl торого соединен с управляющим входом первого мультиплексора, выход регистра результата соединен с входом второго слагаемого сумматора, входы старших разрядов первого слагаемого которого соединены с выходом знакового разряда третьего буферного регистра.

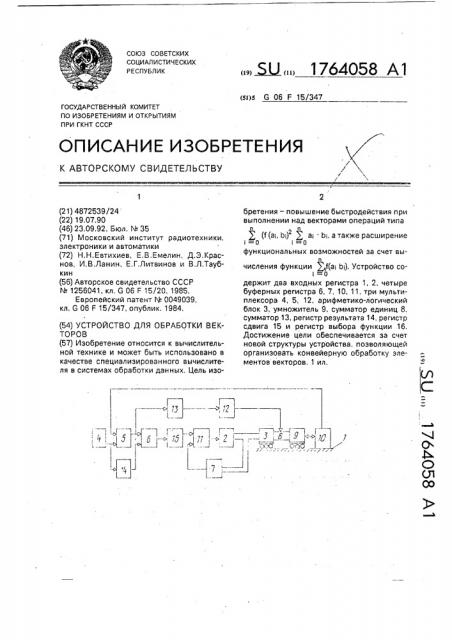

Функциональная схема устройства представлена на чертеже.

Устройство содержит первый 1 и второй

2 входные регистры, арифметика-логический блок 3, мультиплексоры 4 и 5, буферные регистры 6 и 7, сумматор единиц 8, умножитель 9, буферные регистры 10 и 11, мультиплексор 12, сумматор 13, pei истр результата 14, сдвиговый регистр 15, регистр выбора функции 16, информационные входы 17 и 18, вход задания функции 19, выход

20, входы 21 и 22 синхронизации устройства, 1764058

Устройство работает следующим образом. Перед началом работы происходит обнуление регистров 1, 2, 6, 7, 10, 11, 14, 16 и установка в исходное состояние регистра 15 (цепи сброса и начальной установки на чертеже не показаны). Затем по входу 19 в регистр 16 заносится управляющее слово, по которому осуществляется установка реализуемой узлом 3 элементарной функции и коммутация мультиплексоров 4, 5 и 12 (цепи синхронизации на чертеже не показаны).

Далее устройство осуществляет собственно обработку следующим образом.

Векторы А и В подаются на вход устройства поэлементно, но асинхронно. Элемент вектора А через вход 17 подается на регистр

1 и сопровождается импульсом строба с входа 21 для записи в регистр, Соответствующий элемент вектора В через вход 18 подается на регистр 2 и сопровождается стробом с входа 22 для записи в регистр.

Строб записи с входа 22 также подается на вход сдвигового регистра 15, который выполняет функцию временной задержки строба. Сдвинутые по времени относительно строба с входа 22 импульсы с регистра 15 подаются на входы буферных регистров 6, 7, 10, 11 и регистр результата 14, Коммутацией мультиплексоров 4, 5; 12 устанавливаются три режима работы устройства, В первом режиме после записи соответствующих элементов векторов А и B в регистры 1 и 2 выполняется функция в блоке 3 и результат операции, пройдя через мультиплексоры 4 и 5, фиксируется в регистрах 6 и

7 стробом с регистра 15. Содержимое регистров 6 и 7 перемножается на умножителе 9 и записывается в буферный регистр 11 стробом со сдвигового регистра 15. Содержимое регистра 11 через мультиплексор 12 поступает в сумматор 13г и результат выполненной операции записывается в регистр результата 14. Тем самым реализуется первая указанная функция устройства, Во втором режиме после записи в регистры 1 и 2 соответствующих элементов векторов А и В информация через мультиплексоры 4 и 5 перезаписывается в регистры 6 и 7, Далее порядок вычислений тот же. что и в первом случае, Так реализуется вторая функция устройства. В третьем режиме после записи соответствующих элементов векторов А и В в регистры 1 и 2 выполняется предписанная функция в блоке 3 и результат операции подается на вход сумматора единиц 8, информация с выхода которого фиксируется в буферном регистре 10 стробом с регистра

15. Выход регистра 10 через мультиплексор

12 подается на вход сумматора 13 и фиксируется в регистре 14 стробом с регистра 15. единен с третьим выходом регистра сдвига, 50 о т л и ч а ю щ е е с я тем, что, с целью по5

В этом режиме реализуется третья функция работы устройства.

Векторы А и В подаются на вход устройства последовательно, а на выходе регистра

14 формируется результат выбранной функции обработки векторов.

Изобретение позволяет повысить быстродействие устройства при выполнении

П

2 операций типа (f (a;, Ь!)) . д а; b

i=0 i =0 которое достигается преимущественно за счет применения конвейерной обработки элементов векторов и расширить функциональные возможности устройства за счет реализации фуикции,г га;, 0), где а; и bi;—

i=0 соответствующие элементы первого и второго векторов, имеющие разрядность М;

t(a, Ь ) — произвольная простейшая функция двух аргументов; Х1 — функция бинарной корреляции двух векторов.

Формула изобретения

Устройство для обработки векторов, содержащее первый и второй входные регистры, регистр выбора функции, арифметико-логический блок, четыре буферных регистра, регистр результата и регистр сдвига, первый и второй выходы которого соединены соответственно с управляющими входами первого, второго, третьего и четвертого буферных регистров, причем входы первого и второго операндов устройства соединены соответственно с информационными входами первого и второго входных регистров, выходы которых соединены соответственно с входами первого и второго операндов арифметико-логического узла, вход кода операции устройства соединен с входом регистра выбора функции, выход регистра результата соединен с выходом результата устройства, первый вход синхронизации которого соединен с входом синхронизации первого входного регистра. вход запуска регистра сдвига и вход синхронизации второго входного регистра соединены с вторым входом синхронизации устройства, управляющий вход регистра результата совышения быстродействия при выполнении

fl над векторами операций типа, (" (а;. Ь )), i =-0

ll а .Ь, а также расширения функциональi =0 ных возможностей за счет вычисления фунП кций „ >.,f(ai, bi) (где ai и Ь| — соответствующие

i =0

1764058

Составитель Е.Емелин

Техред М.Моргентал Корректор Т.Палий

Редактор Г,Бельская

Заказ 3458 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СCCP

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101 элементы первого и второго векторов, имеющие разрядность М; f(a, Ь ) — произвольная простейшая функция двух аргументов; Х вЂ” функция бинарной корреляции двух векторов, в него введены три мультиплексора, сумматор единиц, умножитель и сумматор, причем информационный вход регистра результата соединен с выходом сумматора, входы младших разрядов первого слагаемого которого соединены с выходом первого мультиплексора, первый и второй информационные входы которого соединены соответственно с выходом значащих разрядов третьего и выходом четвертого буферных регистров, информационный вход третьего буферного регистра соединен с выходом умножителя, первый и второй информационные входы которого соответственно соединены с выходами первого и второго буферных регистров. информационные входы которых соответственно соединены с выходами второго и третьего мультиплексоров, первые информационные входы которых соответственно соединены с выходами первого и второго входных регистров, первый выход регистра выбора функции со5 единен с входом задания режима работы арифметико-логического узла, выход которого соединен с вторыми информационными входами второго и третьего мультиплексоров и входом сумматора еди10 ниц, выход которого соединен с информационным входом четвертого буферного регистра, управляющие входы второго и третьего мультиплексоров соединены с вторым выходом регистра выбора функции, 15 третий выход которого соединен с управляющим входом первого мультиплексора, выход регистра результата соединен с входом второго слагаемого сумматора, входы старших разрядов первого слагаемого которого

20 соединены с выходом знакового разряда третьего буферного регистра.