Накапливающий сумматор

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛ И СТИЧ Е СКИХ

РЕСПУБЛИК (я)5 G 06 F 7/50

? Ъ?-(м » л ?«май »»

ЕТЕНИЯ л.:, ? 1

ГОСУДАРСТВЕНЙЫЙ КОМИТЕТ

-. -.: ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ,, ПРИ I KHT» CCCP * :- -:ОПИСАНИЁ ИЗОБР ьяъ@ф ф ффФф -ф Ф»жАЬ -Ф»мвьйф, . .. -,К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зяма@::" 43Кймй:@? = :". :::. (21) 487«2299/24, -(22) 13.08.90 ., ":(46) 30.09,92. Бюл, ¹ 36 ;., - :-(72) О,И»Федченко (56) Авторское свидетельство СССР

„ :.- -№ 1166099, кл. G 06 F 7/50, 1984.

,". Гамкрелидзе С.А., Завьялов А.B., Маль., цев П»П. и Соколов В.Г. Цифровая обработка ,, ., ийформа»ц»ии»н а ос н ове быстродействующих

: "-",БИС,- M.: Энергоатомиздат, 1988, с,38, : рйс,7. .;::::.:..-":(54) НАКАПЛИВАЮЩИЙ СУММАТОР

-- -::, (57) Изобретение относится к вычислитель : ной техйике и может быть использова lo в

-ъ мфф фф@ф@ ф " " ф т " (pppf

«Яфф.;,""?ь?"..».", " P

4 фф"йф фн ф —,. -а ?. - - ;ФЪ МЫФм МЙ3фМф „; фй +:":-; 4 @Ях ОР .. -% 4 4"Ф фФЖ . фф я 44 ? ф@=,PÔ-;?а.;й, 4 ». « i ++« (? ф *,ффффф-,-:фе", -ЯФ4Ф к . „".". -, р ф . - @ - ;:"? ::у %ф) ЙФ

1

1.

„„. Ж„„1765824 А1 качестве функ«ци«ональй«ого узы стр»ойс?тв обработки информации в реальном масштабе времени, Цель изобретения — повышение скорости обработки входных данных. Накапливающий сумматор содер>(IAT конвейерный сумматор 1, дополнительный регистр

2, L регистров 3 суммы и коммутатор 4, соединенные между собой функционально, Накапливающий сумматор разделяет процесс вычисления общей суммы на L процессов вычисления частных сумм с последующим их подсуммированием, что позволяет повысить скорость обработки входных данных.

4 ил, -"- :.",.« :"- ". ., т .Ф -. " „- -. .= ;;.Фф ф ЯФфв ЛВффФммФъ" 4» -? м ? ? -ЙФ *«»» .а ел» :М м чае»э»4»»»?»Ж ""4 . » -. *«4?4

1765824

Изобретение относится к вычислительной технике и может быть использовано в качестве функционального узла устройств обработки информации в реальном масштабе времени.

Известен параллельный накапливающий сумматор, содержащий в каждом разряде триггер, прямой вход которого соединен с выходом данного разряда сумматора, в каждый разряд которого, с целью увеличения его быстродействия, введен элемент НЕРАВНОЗНАЧНОСТЬ, причем счетный вход триггера 1-го разряда сумматора (1 = 1-п, и-разрядность сумматора) соединен с выходом элемента

НЕРАВНОЗНАЧНОСТЬ того же разряда сумматора, прямой выход триггера 1-го разряда сумматора с первым входом элемента Н Е PAB Н ОЗ НАЧ НОСТЬ !+1-го разряда сумматора, первый вход элемента

НЕРАВНОЗНАЧНОСТЬ младшего разряда сумматора соединен с шиной нулевого потенциала сумматора, второй вход элемента

НЕРАВНОЗНАЧНОСТЬ младшего разряда сумматора соединен с входом данного раз ряда сумматора, входы установки в "0" триггеров всех разрядов соединены с шиной сброса.

Недостатком аналога является низкая скорость обработки входных данных.

Наиболее близким по технической сущности к предлагаемому является накапливающий сумматор, являющийся составной частью умножителя-накопителя 1518ВЖ1 и содержащий сумматор, первый вход которого связан с выходом регистра данных, выход — с входом регистра суммы, а второй вход — с выходом регистра суммы, Недостатком прототипа является низкая скорость обработки входных данных.

Целью изобретения является повышение скорости обработки входных данных.

Поставленная цель достигается тем, что в предложенное устройство, содержащее сумматор, выход которого соединен с информационным входом первого регистра суммы, дополнительно введены L-1 регистров суммы, где L-число повышения скорости обработки входных данных, дополнительный регистр и коммутатор, причем сумматор выполнен конвейерным, первый вход коммутатора является информационным входом накапливающего сумматора, вход переключения режима которого соединен с управляющим входом коммутатора, группа адресных входов которого является управляющим входом накапливающего сумматора, первый выход коммутатора соединен с информационным входом дополнительного регистра, выход которого соединен с пер5

55 вым входом конвейерного сумм ора второй вход которого соединен с вторым выходом коммутатора, являющимся и выходом накапливающего сумматора, выход конвейерного сумматора соединен с информационными входами регистров суммы с второго по L-й, выходы которых соединены соответственно с вторым входом коммутатора.

Отличительными признаками предлагаемого устройства являются наличие не одного, а Lрегистров суммы,,где L — число повышения скорости обработки входных данных, дополнительного регистра и коммутатора, причем сумматор выполнен конвейерным, первый вход коммутатора является информационным входом накапливающего сумматора, вход переключения режима которого соединен с управляющим входом коммутатора, группа адресных входов которого является управляющим входом накапливающего сумматора, первый выход коммутатора соединен с информационным входом дойолнительного регистра, выход которого соединен с первым входом конвейерного сумматора, второй вход которого соединен со вторым выходом коммутатора, являющимся и выходом накапливающего сумматора, выход конвейерного сумматора соединен с информационными входами регистров суммы со второго по L-ый, выходы которых соединены соответственно со вторым входом коммутатора.

Такая структура позволяет разделить процесс вычисления общей суммы на несколько процессов вычисления частных сумм с последующим их суммированием.

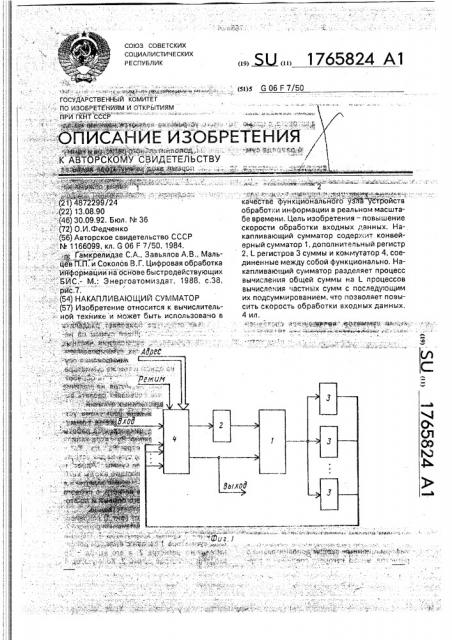

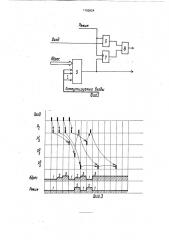

При этом все процессы суммирования осуществляются на одном и том же сумматоре, Зто позволяет повысить скорость обработки входных данных, несмотря на наличие обратной связи, что позволяет сделать вывод о наличии существенных отличий, На фиг,1 изображена блок-схема устройства; на фиг.2 — блок-схема коммутатора; на фиг,3,4 — циклограмма работы устройства и обозначено: Р— вход записи дополнительного регистра; Рз, Рз, Рз

1 2 3 входы записи регистров суммы для устройства с тремя регистрами суммы; "Адрес" и

"Режим" — соответствующие входы коммутатора; 7<, r>, тк, т " — время задержки в сумматоре, на запись в регистр, с первого входа коммутатора на его первый и со второго — на его второй соответственно.

Устройство содержит (фиг,1) конвейерный сумматор 1, дополнительный регистр 2, регистры 3 суммы, коммутатор 4, Первый вход сумматора 1 связан с выходом дополнительного регистра 2, а его выход — со входами регистров суммы 3. Коммутатор 4

5 - " 1765824 6 (фиг,2) содержит, например, мультиплексор сле начала суммированйя последнего вход 5, две схемы И 6 и 7, схему ИЛИ 8, Число ногосигналассодержимымсвоегорегистра коммутируемых входов мультиплексора 5 суммы 3 на вход переключения режима устравно числу ИЛИ 8, Число коммутируемых ройства подается логический "0", при этом входов"мультиплексора 5 равно числу реги- 5 коммутатор 4 связывает свой второй вход со " стров суйс 3. Каждый из э. их входов свя- своим первым "выходом(режим 2), На управ 3fH с вь|ходом-своего-регистра суммы 3. ляющийвходустройстваподаетсяадресодВыход мультиплексора 5 является вторым ного из регистров суммы 3, хранящий уже в iKopdA Коймутатора 4 и связан со вторым сформированную частную сумму. Содержи ... ;,.;. :;-. ." входоМ буйЖГтЪ га 1 и вторым входом вто- 10 мое этого регистра суммы 3 переписывается рои схемы И 7, Первйй вход второй схемы в дополнительный регистр 2. Коммутатор 4

И 7 является ийверсным, связан с первым переводится в режйм 1. На управляющий входом пефвой схемы И 6 и образует вместе вход устройства подается адрес другого pe- вхо И"уйфМйейИя коммутатора 4, Второй 15 мированную частную сумму, Сумматор 1 вил "йервой схемы И 6 является входом начинает суммирование этих двух частных

).: - ус1ройства. Выходы схем И 6 и 7 связаны со сумм, Аналогичным образом осуществляетвходами Схемы ИЛИ 8, выход которой явля- ся суммирование всех других частных сумм " ." ется Нбрвйм "вь(ходом коммутатора 4 и свя- попарно. Результат суммирования каждой зан с" входом-дополййтельйого регистра 2. 20 пары частных сумм записывается в один из

Выходом устройства является второй выход регистров суммь) 3 из этой пары. Полученные к8к и йгора ." " " — реэультаьГсуййМир ЖтЮ й1йло7йчФЖ об -".;Устройство работает следующим обра- разом до тех пор, пока не будет получена зом" (фиг.3,4), Все регистры обнулены, На общая сумма, то есть йока не будут просум вход г)ереключеййя режима устройства по- 25 мированы все частные суммы. Для получедается логическая "1", при этом коммутатор ния доступа к общей сумме на управляющий

4 связывает"свой первый вход со своим пер- вход устоойстЫ подается адрес того per cV ..,.-.. " вй)Ж вйходом," а""йторой вход — с вторым ра Суммы 3, в котором она хранится. выхбДбм (режим 1). На уг равляющий вход Ф о р м у л а и э о б р е т е н и я

)" устройства подается адрес первого регист- 30 Накапливающий сумматор, содержара суммы 3,,";ри этом сигнал с выхода пер- щий сумматор, выход которого соединен с

sorî регйстра "суммы 3 проходит через информационным входом первого регистра мультиплексор 5 на второй вход сумматора суммы, о т л и ч а ю щ и й"с я тем", чтб; с цеййю

1. Очередной входной сигнал через схемы И повышения скорости обработки входных

6 и ИЛИ 8 запйсывается в дополнительный 35 данных, в него введены ) - 1:регистров сумрегистр 2, С выхода которого он проходит на мы, где L — число повышения скорости обрапервый вход Сумматора 1, Сумматор 1 начи- ботки входных данных, дополнительный нает суммирова1 ь зходйые"сигналы, Перед регистр и коммутатор, причем сумматор вызаписью в дойолйительйый регистр 2 следу- полйен койвейерным, первый-вход коммутаf" "" = "-- -- --- -- -,-:---"- --- - "- " - -- — -- - -.- --: - 353;Юйй ЦЕВ гйстра бфЖы 3. Сумматор 1 суммирует этот чения режима которого соединен с управлягистра суммы 3, Аналогичным образом ком- адресных входов которого является управ-! --- :.-:-. муФатор 4 связывает по очереди выходы 45 ляющим входом накапливающего сумматорегйс1ров суммы 3 с вторым входом сумма- ра, первый выход коммутатора соедийен с тора 1. После перебора всех регистров суммы информационным входом дополнительного

3 этот процесс повторяется, начиная с пер- регистра, выход которого сбединен с первого"регистра суммы 3. При этом через вре- вым входом конвейерного сумматора, втомя задефжки в"сумматоре 1 после начала 50 рой вход которого соединен с вторым ла и сйгнЗлаМ"вь)хбда одйбгб йХфФВГСтров ДЖ йййгййвйЯЯЩй б" с МРГа йфа, "вьМд суммы 3 результат записывается в тот же конвейерного сумматора соедийен с инфор самый"регистр" суммы 3, Таким образом в мационными входами регистров суммы с регистрами""б ф4мы 3 формируются частные 55 второго по L-й, выходы которых соединены суммы, Этот процесс продолжается до тех соответственно с вторым входом коммута= пор, пбка доступа)от входные сигналы, По- тора, 1765824

Вход

РЗ

Андрес

4 с

Составитель О, Федченко

Редактор Т. Орловская Техред М,Моргентал Корректор Е. Папп

Заказ 3385 " Тираж " " Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР ... 113035, Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", г. Ужгород, yri,Ãàãàðèíà, 101

i l „"