Устройство для контроля микропроцессора

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„. Ж„„1765828 А1, йю КАФФ..Фж Эг ъ ; 1 =рФФ»- ФД4ф4;. .»»:;-;:. »» Фе.а Г:„;:.:-,:з . -. -.

ГОСУДАРСТВЕЙНЫИ КОМИТЕТ

ПО РЗО«БРЕТЕНИЯВГИ О»ТКРЯТЖМ у»4»»; „ ц р»».» у,.»:«,««».;-.--» -, -". ° н

АПИСА»НИЕ ИЗОУБР .!фя -„-ф ффиф «фффффяяг». » ="»«ф я,» р,—:- «»»»-дфоп:»,, ° .

К ALT OPCKI5MY CBN@TEllbLTffY (21) 4905766/24 (22) 18,12.90 (46) 30.09.92; Бюл. ¹ 36 (72) М,П.Ткачев и В,Ю,Пикин (56) Авторское свидетельство СССР

N 1287161, кл, G 06 F 11/00, 1987.

@ А*вторск«ое свидетел ь"с тво CC СР "

N 1213480, кл. С 06 F 11/00, 1986. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МИКРОПРОЦЕССОРА (57) Изобретение относится к цифровой вычИбл»Й г" ельной технике и может быть исполь.-»»»«та си»:.»»алт»»г« .,:- а»«». »--»;:»--»»-,.O», =-*,»»»» и «»»» . »-.«,",- Изобр»етение отйосится к цифровой выч исл йтел ь»й«о и т ех«йй к е й"может быть испол ьб О ™ О .» уды »»- . »»«„»«»..» .« »«; ».„"«д» -,,: у,-«»;„». Щ«»«» р» „ "».-, з вано -при""" -"" п»ост»роейи»и мйкропроце"с со»рййх"систем"«и мй»кроЭВМ с кон тр оле м. "

"+ Denüþ изобретения является снижение апйар»атурных заТрат. " " . ":* Сущность изобретения состоит в снижений айпаратурйых»»»за грат за" сче Гисйол» ь» зо-" ва«йия" йнформации о "необходимости фо»«рми«р»овайия в каждом машинном цикле ми кро йрвц« ессо» раси г«йал о в си йхфо нФза ц ии

SYNC, а также сигналов приема DBIN или вьда4и 6NIT6"йнформа»ц»ии (за исключением»»ко мЪФф HLT è DAD).

"" ""Ана лиз -реж"йм ов функцион ирования мйк»рВйроц» е»"с»с»ор»а К580ИК80А показал, что каждый машинный цикл каждой йз команд м»йкр»огГроце»с»сора (за исключением" команд

HLN и DADJ "сой«ровождается выдачей" сйгйалов у»йpaeneH éÿ SYNC, а также DBIN«или

WRITE (4). Следовательно, отсутствие этих сйгйЫЪв свйае1ельствует =о» неп ра»вйЪ йбм фуйкционйровайийм«й» кройро«цессора. В ко..вн ц ф »-ц»«» @ @у » .---.. »щ ау., ., «@-.;д««»,*»;»...«=„ .—

" 1й." оМТ ) &@93 = - " 9 8%5B6. - "Ж-«6< (51)5 G 06 F 11/00

» :«> « »,.«» »» !

ЕТЕНИЯ .1 . - -: "й«зя :" л - ФФю1ИФГ»1 3 % =.-;Фц": .Й Йхщ =--.й

2* зо»в»»айо "и р и йос троейи»и м»» и»к р о и»-роцес"сорных"систем и микроЭВМ с контролем.

Целью изобретения является сокращение аппаратурных затрат, Цель достигается путем введения в устройство триггеров, элемента НЕ и элемента ИЛИ. Сущность изобретения состоит в использовании для организации контроля сведений о закономерности йоявл»ей«ия контролйруе»мйх» уй- равляющих сигналов в машинных циклах микропроцессора, отйосящих»ся" к различ ным типам, 2 ил. ,, «» мандах HLT u DAD эти с»йгналы выдаются только в машйнном цикле М1, поэтому при вый«олн»ен»йи" эти»х" ком»" а @ вйдачу сигй»ал«а ошибки необходимо блокировать.

Сущность изобретения реализуется путем введения следующей совокуй«ности от- личительных признаков (новых элементов и связей), определяющих соответствие заявляемого «устро»йства к»р»йтер»й ю "новизна".

Введение второго триггера и его связей и озволяет у пр а влят ь работой дешифратора ком»аЫд B момЪйт Ъйборки кода комайд (во время выполнения машинного цикла М1).

Введенйе третьего трйггера и его связей позволяет фиксировать отсутствие сигналов DBIN u WRITE в каждом машинном цикле каждой команды микройроцессора.

Введение четвертого триггера и его связей позволяет осуществлять блокй ровку выдачи сигнала ошибки при выполнении команд HLT ил и DAD.

Введейие йятого триггера и его связей позволяет фиксировать отсутствие в каж»»» - - . ; »Г «йю» фИ&»., у. +».«»» ÉÈ ÔÔ« .. ..» - . «»»„-,. « . «» .«Щй . .Ф Й„-»«»g:."C: Г. .».:"-фйфффжз М Aj»»- "«»Q>»;««!» .

1765828

15 дом машинном цикле сигнала SYNC микропроцессора и формировать сигнал ошибки.

Введение элемента не позволяет получить неинвертированное (единичное) значение управляющего сигнала WRITE микропроцессора, Введение пятого элемента ИЛИ позволяет формировать сигнал ошибки как при отсутствии сигнала SYNC, так и сигналов

DBIN или WRITE в каждом машинном цикле каждой команды микропроцессора (за исключением команд HLT и DAD), Введение связей, соответствующих второму и четвертому элементам ИЛИ, позволяет осуществлять начальную установку счетчика и четвертого триггера соответственно по сигналу с входа устройства, Введение связей, соответствующих третьему элементу ИЛИ, позволяет формировать сигнал установки третьего триггера в ноль, запрещая тем самым выдачу сигнала ошибки при выполнении команд HLT и DAD, а также при наличии сигналов DBIN u

WRITE.

Введение указанной совокупности признаков обеспечивает достижение цепи изобретения — снижение аппаратурных затрат при контроле управляющих сигналов микропроцессоров.

Предлагаемое техническое решение соответствует критерию "существенные отличия", поскольку в известных устройствах (1-3) вследствие отсутствия указанной совокупности конструктивных признаков не достигалось свойство снижения аппаратурных затрат при контроле управляющих сигналов микропроцессора за счет проверки наличия в каждом машинном цикле каждой команды (за исключением команд

HLT и DAD) сигналов управления SYNC, DBIN u WRITE.

Положительный эффект, который может быть получен при использовании предлагаемого устройства, состоит в снижении затрат на производство и эксплуатацию за счет уменьшения по сравнению с прототипом сложности устройства контроля при той же совокупности управляющих сигналов, подвергающих контролю.

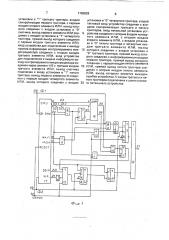

На фиг. 1 представлена функциональная схема устройства для контроля управляющих сигналов управления микропроцессора; на фиг. 2 — временные диаграммы работы устройства, Устройство для контроля управляющих сигналов микропроцессора (фиг. 1) содержит четвертый 1, второй 2, пятый 3, третий

4, первый 4 триггеры, счетчик 6, первый 7 и второй 8 элементы И, элемент ИЛИ-НЕ 9, элемент НЕ 10, четвертый 11, пятый 12, вто20

55 рой 13, первый 14, третий 15 элементы ИЛИ, дешифратор команд 16. На фиг. 1 обозначен также контролируемый микропроцессор 17

На фиг. 1 цифрами 18-22 обозначены соответственно второй WAIT, третий HLDA, четвертый DBIN, пятый WRITE, первый

SYNC выходы микропроцессора, 23 — шина данных микропроцессора, 23,1, 23.2 — выходы разрядов DO и D5 шины данных 23 микропроцессора; 24 — прямой выход второго триггера; 25, 26 — соответственно первый и второй выходы дешифратора команд 16; 27 — выход ошибки устройства; 28, 29, 30— соответственно первый, второй и третий входы устройства.

Рассмотрим работу предлагаемого устройства.

Перед началом работы на вход 30 устройства подается сигнал высокого уровня длительности не менее трех периодов тактовой частоты микропроцессора 17, которым микропроцессор устанавливается в исходное состояние. Этим же сигналом в исходное нулевое состояние устанавливаются триггеры 1,3,4, счетчик 6. После этого в микропроцессоре начинается такт Т1 машинного цикла выборки команды М1 (см. фиг. 2), На входы 28 и 29 устройства поступают неперекры вающиеся последовател ьности тактовых импульсов первой Ф1 и второй Ф2 фазы соответственно.

Каждый машинный цикл сопровождается выдачей с выхода 22 микропроцессора сигнала синхронизации SYNC в такте Т1.

При этом на шину данных 32 выдается слово состояния микропроцессора, При появлении на входах элемента И 7 сигнала SYNC высокого уровня и разрядов D5 = 1 и DO = 0 слова состояния, выставленного на шине данных, элемент И 7 открывается и триггер

2 по заднему фронту импульса Ф1, поступившему на его синхровход, переходит в единичное состояние, разрешая тем самым дешифратору команд 16 работу (см, фиг. 2), Код команды поступает по шине данных в дешифратор команд, где по синхроимпульсу Ф1 (со входа 28 устройства) происходит дешифрация кода команды и в случае появления кода команды DAD или HLT на выходах соответственно 25 или 26 дешифратора появится единичный сигнал.

Выявление команд HLT u DAD необходимо, так как только при выполнении этих команд для микропроцессора К580ИК80 в машинных циклах отсутствуют сигналы

DBIN и WRITE; Поэтому, чтобы при выполнении этих команд устройство контроля не формировало ложного сигнала ошибки, необходимо заблокировать выдачу этого сиг1765828

50 нала на время выполнения этих команд. Это . происходит следующим образом. П ри поя влении кодов команд DAD или HLT триггер 1 едйййчйым"сйгналом с выходов 25 или 26

- дешифратора команд 16 устанавливается в, едиййчйое состояййе и сйгналом со своего . прямого выхода через элемент ИЛИ 15 блокйрует триггер 4, удерживая его в нулевом состоянии дО прихода следующей команды, При йриходе следующей команды триггер 1 устанавливается в нулевое состояние сигналом, йостугФВщим на его вход установим в

"0" с выхода элемента И 7. Если текущая комайда на DAD и не HLT, то сигналом

SYNC с выхода 22 микропроцессора по задйему фройту-импульса фазы Ф2 с входа 29 устройства триггер 4 переходит в единичное сост оя н"ие ui"е диничным сигн алом со своего прямого вь хбда готовит триггер 5 к переходу в единичйое состояние. Этот переход произойдет в начале следующего машинного цикЛа в случае, если триггер 4 не будет установлен в ноль сигналами DBIN с выхода

20 микропроцессора или WRITE с выхода 21 микропроцессора. При наличии одного из этих сигналов, что соответствует правильной работе микропроцессора, триггер 4 устанавливается в нулевое Состояние до прихода следующего сигнала SYNC, а триггер 5 остается в нулевом состоянии, Если же при выполнении команды (кроме HLT u

DAD) в машинном цикле не оказалось ни сигнала DBIN, ни сигнала WRITE, то следующим импульсом SYNC с выхода 22 микропроцессора триггер 5 переводится в единичное состояние и на выход 27 устройства через элеМент ИЛИ 12 выдается сигнал ошибки.

В та*кте Т1 машинного цикла М1 начинает работать счетчик 6 с коэффициентом пересчета 4. Он считает поступающие на его счетный вход «через элемент И 8 тактовые импульсы фазы Ф1 с входа 28 устройства.

При появлений сигнала SYNC на выходе 22 микропроцессора счетчик 6 устанавливается в нулевое Состоянйе этйм единичным сиг= налом, поступающим на его вход установки в ноль через элемент ИЛИ 13, При отсутствии сигнала в любом машинном цикле, что соответствует неправильной работе микропроцессора, счетчик переполняется и на его выходе появляется единичный сигнал, который переводит триггер 3 в единичное состояние. На прямом выходе триггера 3 появляется единичный сигнал, который через элемент ИЛИ 12 выдается на выход 27 устройства как сигнал ошибки. Для исклю чения ложного сигнала ошибки вследствие переполнения счетчика, что возможно в режимах "Ожидание" и "Захват" (в этих режи5

45 мах до их окончания сигнал SYNC не выдается, а выдача тактовых импульсов Ф1 и Ф2 продолжается (4), счетный вход счетчика 6 блокируется нулевым сигналом элемента

И8, который, в свою очередь, заперт нулевым сигналом с-выхоДа элемента ИЛИ-НЕ 9.

Нулевой сигнал на выходе элемента ИЛИНЕ 9 появляется только при наличии на его входах единичных сигналов WAIT (что соответствует режиму "Ожидание" ) или HLDA (что соответствует переходу к режиму "3aхват" ). Таким образом, можно считать, что сигналы управления WAIT с выхода 18 микропроцессора и HLDA с выхода 19 микропроцессора косвенно контролируются, а при их отсутствии в нужный момент будет также сформирован сигнал ошибки.

Формула изобретения

Устройство для контроля микропроцессора, содержащее первый и второй элементы И, счетчик, дешифратор команд, четыре элемента ИЛИ, элемент ИЛИ-НЕ, первый триггер, причем вход устройства для подключения к выходу синхронизации контролируемого микропроцессора соединен с первым входом первого элемента И, первый и второй выходы дешифратора команд соединены соответственно с первым и вторым входами первого элемента ИЛИ, входы устройства для подключения к выходам ожидания и захвата контролируемого микропроцессора соединен соответственно с первым и вторым входами элемента ИЛИНЕ, первый тактовый вход устройства соединен с первым входом второго элемента И, выход которого соединен со счетным входом счетчика, о т л и ч а ю щ е е с я тем, что, с целью уменьшеййя аппаратурных затрат, устройство содержит второй, третий, четвертый и пятый триггеры, элемент НЕ, пятый элемент ИЛИ, причем пятый и нулевой разряды информационного входа для подключения к шине данных контролируемого микропроцессора соединены соответственно с вторым и третьим инверсными входами первого элемента И, выход которого соединен с информационным входом второго триггера, первый тактовый вход устройства соединен с синхровходом дешифратора команд и с синхровходом второго триггера, прямой выход которого соединен с входом разрешения дешифратора команд, инфор- мационный вход устройства для подсоединения к шине данных микропроцессора соединен с группой информационных входов дешифратора команд, выход элемента

ИЛИ-НЕ соединен с вторым входом второго элемента И, вход устройства для подключения к выходу синхронизации контролируемого микропроцессора соединен с входом

1765828

С6РОС установки в "1" третьего триггера, входом синхронизации первого триггера, с первым входом второго элемента ИЛИ, выход которого соединен с входом установки в "0" счетчика, выход первого элемента ИЛИ соединен с входом установки в "1" четвертого триггера, прямой выход которого соединен с первым входом третьего элемента ИЛИ, вход устройства для подключения к выходу приема информации контролируемого микропроцессора соединен с вторым входом третьего элемента ИЛИ, вход устройства для подключения к выдаче информации выходу контролируемого микропроцессора соединен через элемент HE с третьим входом третьего элемента ИЛИ, выход счетчика подключен к входу установки в "1" пятого триггера, выход первого элемента И соединен с первым входом четвертого элемента

ИЛИ, выход которого соединен с входом установки в "0" четвертого триггера, второй тактовый вход устройства соединен с входами синхронизации третьего и пятого триггеров, вход начальной установки уст5 ройства соединен с вторым входом четвертого элемента ИЛ И, с вторым входом второго элемента ИЛИ, с входом установки в "0" пятого триггера и четвертым входом третьего элемента ИЛИ, выход

10 которого соединен с входом установки в - 0" третьего триггера, прямой выход которого соединен с информационным входом первого триггера, прямой выход которого соединен с первым входом пятого элемента

15 ИЛИ, прямой выход пятого триггера соединен с вторым входом пятого элемента . ИЛИ, выход которого является выходом ошибки устройства, К-входы третьего и пятого триггеров подключены к шине нулево20 го потенциала устройства...-1 765828

%A ГГ

si DA .1 .

* ° — Составитель И.Сафронова

Редактор Т.Орловская Техред M.Ìîðãåíòàë

Корректор Э.Лончакова

Заказ 3386 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательскйй комбинат "Патент", г. Ужгород. ул.Гагарина, 101