Гармонический корректор

Иллюстрации

Показать всеРеферат

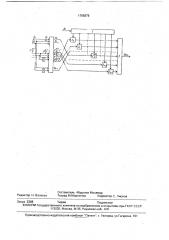

Изобретение относится к радиотехнике и электронике и предназначено для коррекции линейных искажений передаточных функций каналов связи. Целью изобретения является уменьшение времени настройки корректора за счет уменьшения вычислительной сложности пересчета коэффициентов и упрощения аппаратурной реализации гармонического корректора. Гармонический корректор содержит N-отводную линию задержки 1, N умножителей 2-2м-1. сумматор 3, блок дискретного преобразования Фурье 4 и N/2 инверторов 5. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 Н 03 В 5/04

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4869822/09 (22) 24,09.90 (46) 30,09,92. Бюл. N- 36 (71) Одесский электротехнический институт связи им. А.С.Попова (72) Абдуллах Мохамад (SV) В.А.Балашов, В.Ю,Ильиченко и А.М.Темесов (SU) (56) Нудельман П.Я.Полиномные синтезаторы частотных и временных характеристик.

М.: Связь, 1975, с.24 — 30, рис, 3.2.

Коррекция искажений в Трактах и каналах связи. Под ред. Поповой H.Ý. М.: Связь, 1979, с.97, рис. 7,10.

Авторское свидетельство СССР

N 1166317,,кл,,Н 04 ВЗ/04,,1983.

Изобретение относится к технике связи и предназначено для коррекции линейных искажений передаточных функций каналов связи, Известны гармонические корректоры (ГК), описанные в (1) и (2).

Из известных ГК наиболее близким яв= ляется корректор, описанный в (3). Корректор содержит N-отводную линию задержки, выходы которой соединены с первыми входами перемножителей, к вторым входам которых подключены выходы блока преобразования управляющих сигналов, а выходы перемножителей подключены к входам сумматора, выход которого является выходом корректора, С целью уменьшения времени настройки ГК и увеличения ее точности в корректоре по а.с. ¹ 1166317 настройка осуществляется по коэффициентам bk, k=0,1,2...„N — 1, которые затем пересчитываются в коэффициенты ап, n = 0,1,2„„, N — 1 традиционного ГК по соответствующей формуле, » Ы 1765879 А1 (54) ГАРМОНИЧЕСКИЙ КОРРЕКТОР (57) Изобретение относится к радиотехнике и электронике и предназначено для коррекции линейных искажений передаточных функций каналов связи. Целью изобретения является уменьшение времени настройки корректора за счет уменьшения вычислительной сложности пересчета коэффициентов и упрощения аппаратурной реализации гармонического корректора. Гармонический корректор содержит N-отводную линию задержки 1, N умножителей 2-2и-1, сумматор 3, блок дискретного преобразования Фурье 4 и N/2 инверторов 5. 1 ил.

Недостатки предложенной процедуры настройки заключаются в сложности реализации пересчетной формулы. Для случая аналогового построения корректора при N

100 пересчетная схема будет содержать порядка 10 000 только резисторов, не включая усилителей и других элеметов. При цифровой реализации корректора пересчет коэффициентов потребует выполнения N перемножений комплексных чисел.

Цель изобретения — уменьшение времени настройки корректора за счет уменьшения вычислительной сложности пересчета коэффициентов, В изобретении вместо блока преобразования управляющих сигналов в схеме ГК применен блок дискретного преобразования Фурье (ДП Ф), N — комплексных входов которого попарно объединены, за исключеN,...;. нием нулевого и — "входов (N — четное), 2

A-действительный вход соединен с N — и действительным входом непосредственно, а п17G5879 мнимый вход с N — и мнимым входом через

N — 1 инвертор, где и =1,2,..., Выходы блока

ДПФ соединены с входами соответствующих перемножителей по схеме: n — выход 5 соединен с входом m — перемножителя, где

m=((N — 1)/2+n)modN при N — нечетном и m=(N/2+n)modN при N — четном.

На чертеже представлена блок-схема 10

ГК, Корректор содержит линию задержки 1, N перемножителей (2о...2N-1), сумматор 3, блок ДПФ 4, инверторы 5.

Устройство работает следующим абра- 15 зом. Входной сигнал поступает на вход линии задержки 1, в которой задерживается на время (N — 1)Т, где N — число отводов линии задержки; Q — верхняя частота корректируемого спектра; Т=1/Q — время задержки од- 20 ного элемента линии задержки.

С выходов линии задержки сигнал, задержанный соответственно на время пТ, п=0,1,2...„N — 1, поступает на первые входы перемножителей 2p...2è-<, где перемножа- 25 .ется на управляющие сигналы an, n

=0,1,2,..., N — 1, поступающие с выходов блока ДПФ 4. С выходов перемножителей сигналы поступают на входы сумматора 3, выходной сигнал которого является выход- 30 ным сигналом корректора.

На входы блока 4 поступают управляющи сигналы Ь, k = О, 1, 2,.„, N — 1, значения которых устанавливаются в режиме "Настройка". Сигналы Ьк — комплексные, т,е. 35 представлены двумя сигналами

Ьк = Ск+ idy, (1) где Ск — действительная составляющая bI< (действительный сигнал);

dk — мнимая составляющая bk (мнимый 40 сигнал).

В силу свойств спектра вещественного сигнала сигналы Ьк К=0,1,2,...,N — 1, удовлетворяют требованию

Ьо= Со 45

bk = ЬМ-k где — k = 1,2,..., (N — 1)/2 (N — нечетное), k = 1,2,..., К/2 (N — четное).

В соответствии с этим достаточно задавать значения лишь половины сигналов Ьк, а вторую половину сигналов формировать в соответствии с (1), инвертируя сигналы бк.

С этой целью включены инверторы сигналов 5.

Блок 4 осуществляет стандартное преобразование ДПФ.! — кп и — 1 2r

an= —, Ьке ч

N„o (2) k = 0,1,2,..., N — 1; n=0,1,2...„N — 1.

Выходные сигналы ал блока 4 поступают на входы перемножителей 2p...2è-1 в следующем порядке: и — сигнал поступает на ((N — 1)/2+п)гпобМ вЂ” перемножитель, если N— нечетное и (N/2+n)modN — перемножитель, если К вЂ” четное.

N — 1

m =(— + и) mod N npu N — нечетном

N и m =(— + n)modN при N — четном.

Формула изобретения

Гармонический корректор, содержащий

N-отводную линию задержки, вход которой является входом гармонического корректора, каждый отвод подключен к первому входу соответствующего из N умножителей, выход каждого умножителя подключен к соответствующему входу сумматора, выход которого является выходом гармонического корректора, а также блок преобразования управляющих сигналов с N входами, о т л ич а ю шийся тем, что, с целью уменьшения времени настройки, блок преобразования управляющих сигналов выполнен в виде блока дискретного преобразования Фурье с

N комплесными входами, и-й вход которого объединен с (N-n)-м входом для действительной составляющей непосредственно, а для мнимой составляющей — через инвертор, и-й выход блока дискретного преобразования Фурье соединен с вторым входом

m-го умножителя, где

1765879

Составитель Абдуллах Мохамад

Техред М.Моргентал Корректор С, Лисина

Редактор Н. Волкова

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101

Заказ 3388 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5