Устройство для вычисления симметрических булевых функций

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано при построении многофункциональных устройств цифровой обработки информации. Цель изобретения - повышение быстродействия устройства. Устройство для вычисления симметрических булевых функций содержит два элемента сложение по модулю 2 1 и 2, элемент 3 мажоритарности с порогом два, три элемента И 4-6, семь входов и один выход. На входы устройства подаются сигналы настройки UiU, значения которых принадлежат множеству {0, 1, xi, xi, X2, х, хз, хз, хз, Х4}, а на выходе реализуется симметрическая булевая функция Fj FI (xi, X2, хз, Х4), определяемая вектором О (Ui, U2, ..., U), где 1 0. 131. 1 табл., 1 ил.

(19) (!! ) СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (s»s G 06 F 7/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИ

К ABTOPCKOMY СВИДЕТЕЛЬСТВУ

g 7

У

g 9

d 3

Ф о 4 Ь М (л (ху,тц (21) 4484782/24 (22) 20,09.88 (46) 07.10,92. Бюл, М 37 (72) Л.Б. Авгуль, О.Т. Аликов, В.П. Супрун и

H À. Егоров (56) Авторское свидетельство СССР

М 1396137, кл. G 06 F 7/00, 1986.

Авторское свидетельство СССР

М 1689943, кл. G 06 F 7/00, 1988, (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ

СИММЕТРИЧЕСКИХ БУЛЕВЫХ ФУНКЦИЙ (57) Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано при построении многофункциональных устройств цифровой обработки информации. Цель изобретения — повышение быстродействия устройства.

Устройство для вычисления симметрических булевых функций содержит два элемента "сложение по модулю 2" 1 и 2, элемент 3 мажоритарности с порогом два, три элемента И 4-6, семь входов и один выход. На входы устройства подаются сигналы настройки U>, .„07, значения которых принадлежат множеству (О, 1, х1, х1, хг, х"„, х3, х3, х4, х4), а на выходе реализуется симметрическая булевая функция F< = Fi (x1, хг, х3, х4), определяемая вектором U = (01, 0г,,.„07), где i = О. 1, ..., 31. 1 табл., 1 ил, 1767495

Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано при построении многофункциональныхустройств цифровой обработки информации.

Цель изобретения — повышение быстро- 5 действия устройства.

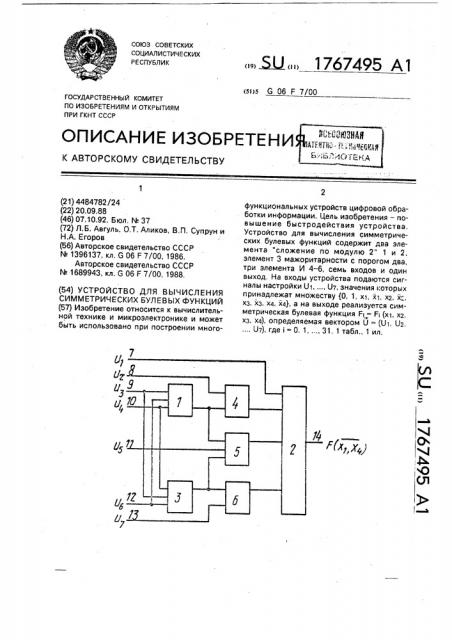

На чертеже представлена схема устройства для вычисления симметрических булевых функций (с.б.ф.)

Устройство содержит два элемента 10

"сложение по модулю 2" 1 и 2, элемент 3 мажоритарности с порогом два, три элемента И.4, 5, и 6, семь входов 7...13 и выход 14.

Устройство работает следующим образом. 15

На входы 7...13 устройства подаются сигналы настройки Ui ... 07 соответственно, значения которых принадлежат множеству (О, 1, хт, хт, х2, х2, хз, хз, х4, х4). На выходе 14 реализуется с. б, ф. Fi = FI (хт, х2, х3, х4), 20 определяемая вектором U = (Ui 02..... U7), где i =О, 1, ...,31, Первообразная устройства имеет вид

f(Ui, U2, ..., От) = От З 02(0з9 04 О Обф

9(03 9 049 00) Об М (U3, 04, Ue)O+Uz М (Оз, 25

04, 00), где функция мажоритарного элемента определяется как

1, если zi + z2 + z3 >2

M(Zi 22, Z3) = 30

О, ЕСли zi + z2+ З Ы, где zg 6 (О, 1) и к = 1. 2, 3.

Сигналы настройки

У п/п

8 (88

9 U 10 U тт U612 ттт тз

"г оооо о

2 О

ОООО ОООО ОО0О х, х, х, х, х, т

3 О

4 О х, . т х, О

5 О

6 0 х+ хэ

Х2 х, 7

8 О х, т х, 0

9 Хг то Хэ

Х4 т2 х, т3 х, т4 х< т5 Х4 тб х, т7 х, is х, х, х

X)

0 т

Х2 х, Х+

Хг

Х2

Хэ х„ х, х, т х, Х2 х, ХХэ х, х, х, х, Хг

Х4 х, Х2 х, х, х<

Х4 х„

Хг х< х, х, х, Хв х, Х4 х, "+ х, х, х, Х2

Х, х, Х3 х, х+ х, х, х, Х, х, х х, Х4

Хэ

Х2 х, х, Хэ

Х, х, х4

Х3

Хэ х, Х4

Реализуемые устройством с. б, ф. Fi (i =

=О, 1, ..., 31) и соответствующие им значения сигналов настройки От, U2, „., От представлены в таблице.

Ф ормула изобретения

Устройство для вычисления симметрических булевых функций, содержащее два элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА и три элемента И, причем выход J-ro элемента

И соединен с j-м входом первого элемента

СЛОЖЕНИЕ ПО МОДУЛЮ ДВА (j = 1, 2, 3), выход которого является выходом устройства, четвертый вход первого элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА соединен с первым входом устройства, второй вход которого соединен с первым входом первого элемента И, выход второго элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА соединен с первыми входами второго и третьего элементов

И, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит элемент мажоритарности с порогом два, выход которого соединен с вторыми входами первого и второго элементов И, третий вход последнего из которых соединен с третьим входом устройства, (j + 3)-й вход которого соединен с j-ми входами элементов СЛОЖЕНИЕ ПО МОДУЛЮ ДВА и мажоритарности с порогом два, седьмой вход устройства соединен с вторым входом третьего элемента И, Двоичный номер (таблица истинности) реализуемой функции на выходе т4 устройства

oooo oooo oooo ооот оооо аоот ооот отто

0000 Ооот Ооот оттт

Ооот Отто Отто i000

Ооот Отто отто т001

0001 оттт Оттт ттто ооот o» i оттт тттт отто тооо тооо оооо отто тооо тооо ооот

0тто looi тоот отто о»о тоат тоот oiii

Оттт ттто ттто тооо

oiii ттто ттто iooi

o»»»i ii»»io о»т тттт ттт«ттт

iOOO OOOO 0000 ОООО тооо 0000 0000 000т

1767495

Продолжение таблицы

Двоичный номер (таблица истинности) реализуемой

Еункции на выходе 14 устройства

Н и/п

Сигналы настройки

0 7 0 8 U3 9 U+10 U 11 UЕ12 0т 13

Х4

20 Хе

21 Х2

22 Х

23 Х„

24 х<

1000 0001 0001 0110

1000 0001 0001 0111

1001 0110 0110 1000

1001 0110 0110 1001

1001 0111 .0111 1110

Х, Х4

Х

Х<

Х4

Х, Xf

Х, Х

Х, 0

Х, 1

1001

1110

0111 0111 1111

1000 1000 0000

Х

Х

Х4

xf

Х4

Х4

Х3

26 1

27 1

28 1

29

30 1

31 1

1110 1000 1000 0001

1110 1001 1001 0110

1110 1001 1001 0111 1111 1110 1110 1000

1111 1110 1110 1001

1111 1111 1111 1110

1111 1111 1111 1111

Х, Х

Х, э

32 1

Х4

35

45

Редактор Л.Волкова

Заказ 3549 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101

Х2

Х, Х4

Х2

Х2

Х4

Х, Х4

Х, Х4

Х, Х

Х, X(Хэ 1

Х, 1

Х3 0

Х1 Х4

Х, Х, Х, Х

Х Х

Х Х, Х Х

Х

Х4 0

Х, 0

Составитель В.Сорокин

Техред М.Ыоргентал Корректор Л.Филь