Микропрограммное устройство управления

Иллюстрации

Показать всеРеферат

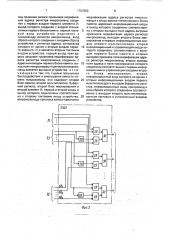

Изобретение относится к вычислительной технике и может быть использовано для построения блоков микропрограммного управления ЭВМ. Изобретение позволяет повысить быстродействие и уменьшить емкость памяти микрокоманд. Для этого устройство (фиг. 1) содержит блок 1 памяти микрокоманд, регистр 3 микрокоманд, первый блок 2 памяти, первый мультиплексор 5, первый элемент И 6, первый блок 7 маскирования , второй мультиплексор 8. буферный регистр 9, второй блок 10 маскирования, второй блок 11 памяти, второй элемент И 12 и регистр 4 адреса. 9 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)ю G 06 F 9/22

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4353949/24 (22) 18.11.87 (46) 07,10.92. Бюл. hL 37 (72) А.П. Акимов. О.И. Дапин, В.Б. Матвеев, Е.О. Поливода, А.Н. Скворцов и А.У. Ярмухаметов (56) Машина вычислительная электронная цифровая ЕС 1045, Процессор (Техническое описание) ЩК1.700.026 НТ02. ..Машина вычислительная электронная цифровая ЕС 1033. Процессор — каналы ЕС

2433 (Техническое описание, Часть 2) ПР

3.055.014. Т01 (прототип).,, Я2„„1767500 А1 (54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО

УПРАВЛЕНИЯ (57) Изобретение относится к вычислительной технике и может быть использовано для построения блоков микропрограммного управления ЭВМ. Изобретение позволяет rloвысить быстродействие и уменьшить емкость памяти микрокоманд. Для этого устройство (фиг. 1) содержит блок 1 памяти микрокоманд, регистр 3 микрокоманд, первый блок 2 памяти, первый мультиплексор 5, первый элемент И 6, первый блок 7 маскирования, второй мультиплексор 8, буферный регистр 9, второй блок 10 маскирования, второй блок 11 памяти, второй элемент И 12 и регистр 4 адреса. 9 ил.

17b7500

Изобретение относится к вычислительной технике и может быть использовано для построения блоков микропрограммного управления ЭВМ.

Цель изобретения — повышение быстродействия и уменьшение емкости памяти микрокоманд, На фиг, 1 показана структурная схема устройства; на фиг. 2 — пример реализации блока маскирования; на фиг, 3 — временная диаграмма постуйления сйнхросигналов; на фиг. 4...9 — граф-схемы алгоритмов.

Устройство (фиг. 1) содержит блок 1 памяти микрокоманд, первый блок 2 памяти, регистр 3 микрокоманд, регистр 4 адреса, первый мультиплексор 5, первый элемент И

6, первый блок 7 маскирования, второй мультиплексор 8, буферный регистр 9, второй блок 10 маскирования, второй блок 11 памяти, второй элемент И 12, второй тактовый вход 13, вход 14 сброса, вход 15 логических условий, первый 16 и третий 17 тактовые входы, первый выход 18-поля адреса, первый выход 19 поля маскирования, первый выход 20 признака типа модификации адреса, второй выход 21 признака записи признаков типа модификации адреса, второй выход 22 поля адреса загрузки признаков типа модификации адреса, второй выход 23 поля адреса, второй выход 24 поля маскирования, второй выход 25 признака типа модификации адреса, первый выход 26 поля адреса загрузки признаков модификации адреса и первый выход 27 признака записи признаков модификации адреса регистра 3 микрокоманд, Блок 7(10) маскирования (фиг, 2) содержит элементы НЕ 28, элементы И 29, элементы ИЛИ 30, первый 31, второй 32 информационные и управляющий 33 входы, Временная диаграмма поступления .синхросигналов приведена на фиг, 3, Синхросигналы С1, С2, СЗ следуют последовательно друг за другом и разделены временными промежутками.

B каждой микрокоманде задается режим формирования адреса следующей микрокоманды (безусловный или условчый переходы). Безусловный переход задается нулевыми значениями сигналов маски, поступающими с выхода 19 регистра 3 на вход

33 блока 7 маскирования, Условный переход кодируется ненулевыми значениями маски, В режиме безусловного перехода, непосредственно задаваемый в текущей микрокоманде адрес, поступающий с выхода 18 регистра 3 на вход 32 блока 7 маскирования без изменений выдается на выход блока 7 маскирования. С выхода блока 7 маскирова15 памяти в ходе выполнения микропрограм20

50

5

45 ния данный адрес поступает на информационный вход регистра 4 адреса.

При условном переходе непосредственно задаваемый адрес модифицируется. Модификация заключается в замене разрядов непосредственно задаваемого адреса (соответствующих единичным значениям маски) на значения разрядов источников модификации. Имеется три источника модификации; — признаки, поступающие на вход 15 устройства;

- признаки, буфериэированные в предыдущих тактах работы в блоке 2 памяти;

- признаки, установленные в блоке 11 мы, Источник модификации задается управляющими сигналами, поступающими с выходов 20 и 25 регистра 3 на управляющие входы мультиплексора 5 и мультиплексора

8 соответственно.

При использовании первого источника модификации, признаки через вход 15устройства поступают на выход мультиплексора 5.

При использовании в качестве источника модификации блока 2 памяти или блока

11 памяти, информация поступает с выхода регистра 9 на выход мультиплексора 5.

Микропрограммное устройство работает следующим образом.

Устройство приводится в исходное состояние по сигналу, поступающему через вход 14 устройства на входы сброса регистра 3, регистра 4 и регистра 9, При этом регистры 3 и 9 устанавливаются в состояние

"0", а в регистр 4 заносится первый исполнительный адрес микропрограммы (на фиг.

1 цепи занесения первого исполнительного адреса не показаны). С выходов регистра 4 данный адрес поступает на вход блока 1 памяти.

В каждом такте работы устройства на

его тактовые входы 16, 17, 13 подаются синхросигналы С1, С2, СЗ соответственно.

С поступлением на вход 16 устройства синхросигнала С1, происходит чтение микрокоманды из блока 1 памяти в регистр 3.

С выхода блока 2 памяти (выхода блока

11 памяти) производится чтение информации из ячейки памяти. Адрес при этом задается сигналами с выхода 26 (22).

Прочитанная информация поступает на информационные входы мультиплексора 8.

В соответствии с управляющим сигналом, поступающим с выхода 25 регистра 3 на управляющий вход мультипилексора 8, производится выдача на выход мультиплексора 8 тех или иных данных.

По синхросигналу С2, поступающему на синхровход регистра 9 производится запись

1767500 в регистр 9 значения строки блока 2 памяти блока 11 памяти), поступающего с выхода мультиплексора 8 на информационный вход регистра 9.

На выход блока 10 маскирования выда- 5 ются разряды кода или старого значения строки блока 11 памяти (или блока 2 памяти) в соответствии со значениями разрядов маски.

При необходимости буферизации при- 10 знаков в данном такте работы в микрокоманде устанавливаются соответствующие разряды. Буферизация признаков, поступающих на вход 15 устройства, задается управляющими сигналами, поступающими с 15 выходов 26 и 27 регистра 3 соответственно на адресный вход и через элемент И 6 (стробирование синхросигналом СЗ) на вход чтения/записи блока 2 памяти.

При установке признаков в блоке 11 па- 20 мяти выбор номера строки производится адресными сигналами, поступающими с выхода 22 регистра 3 на адресный вход блока

11 памяти.

Запись в блок 11 памяти стробируется 25 синхросигналом СЗ, поступающим со входа

13 устройства через элемент И 12 на вход чтения/записи блока 11 памяти, На соответствующий вход блока 7 маскирования подаются сигналы с выхода 30 мультиплексора 5, то есть либо сигналы со входа 15, либо сигналы с выхода регистра 9, На выход блока 7 маскирования выдаются непосредственно задаваемые разряды адреса (с выхода 18 регистра 3), либо 35 информация с выхода мультиплексора 5, в соответствии со значениями разрядов маски, Синхросигналом СЗ, поступающим на синхровход регистра 4, производится эа- 40 пись s регистр 4 сформированного в данном такте адреса следующей микрокоманды, поступающего с выхода блока 7 маскирования на информационный вход регистра 4.

Поступление синхросигнала С3 завер- 45 шается такт работы устройства. Затем все повторяется снова.

На фиг. 4 приведены две граф-схемы алгоритмов, имеющих одинаковые последовательности управляющих сигналов: Н1, 50

Н2, ..., Н9.

На фиг. 5 приведена обобщенная графсхема алгоритма, .включающая последовательность управляющих сигналов: Н1, Н2, ..., Н9. При выполнении микрокоманды А1 в 55 блоке 11 памяти устанавливается разряд

F(0): = О, а при выполнении микрокоманды

В1 в блоке 11 памяти устанавливается разряд F(0); = 1, Во время выполнения микрокоманды Н9 производится проверка условия F(0) = О, после чего выполняются действия по первому (фиг. 4а) или по второму (фиг. 4б) алгоритму. Использование, в данном случае, блока 11 памяти позволило уменьшить объем первого блока 1 памяти на

9 ячеек.

На фиг. 6 приведена граф-схема алгоритма с объединением и разветвлением ветвей. Микрокоманды 61. G2, G3 производят подготовку анализа К = (например, анализа кода команды).

На фиг. 7 приведена та же-самая графсхема, но с использованием установки (F(0)

: = О или F(O) = 1) и анализа признака (F(0) =

О), что позволило исключить микрокоманды (G1, G2, G3) подготовки анализа.

При выполнении сложных микропрограмм бывает необходимо выбрать нужную ветвь микропрограммы, соответствующую всем предыдущим событиям, произошедшим при выполнении микропрограммы (фиг. 8). При этом анализ признаков проводится последовательно друг эа другом, причем каждому анализу (L1, 1 2) предшествуют микрокоманды подготовки признака к анализу ((.1, 2 ).

Предлагаемое устройство реализует установку независимо друг от друга (и последовательно друг за другом) нескольких разрядов (F(0), F(1) строки блока 11 памяти, Это позволяет в дальнейшем выбрать в течение одного такта нужную ветвь микропрограммы, соответствующую всем предыдущим событиям, произошедшим при выполнении микропрограммы (фиг. 9) (при одновременном исключении микрокоманды

L1, L2 подготовки анализа).

Формула изобретения

Микропрограммное устройство управления, содержащее первый блок памяти, регистр микрокоманд, блок памяти микрокоманд, регистр адреса, первый мультиплексор, первый элемент И, первый блок маскирования, первый, второй и третий информационные входы и выход которого соединены соответственно с выходом первого мультипилексора, первыми выходами поля адреса микрокоманд и поля маскирования регистра микрокоманд и информационным входом регистра адреса, выход которого соединен с адресным входом блока памяти микрокоманд, выход которого соединен с информационным входом регистра микрокоманд, первый выход признака типа модификации адреса которого соединен с управляющим входом первого мульгиплексора, первый информационный вхоц которого соединен с информационным входом первого блока памяти и является входом логических условий устройства, первый вы1767500

7(70) ход признака записи признаков модификации адреса регистра микрокоманд соединен с первым входом первого элемента И, выход которого соединен с входом чтениязаписи первого блока памяти, первый тактовый вход устройства подключен к синхровходу регистра микрокоманд, вход сброса которого соединен с входами сброса устройства и регистра адреса, синхровход которого сс".динен с вторым входом первого элемента И и является вторым тактовым входом устройства, первый выход поля адреса. загрузки признаков модификации адреса регистра микрокоманд соединен с адресным входом первого блока памяти, выход поля микроопераций регистра микрокоманд является выходом устройства, о т л ич а ю щ е е с я тем, что, с целью повышения быстродействия и уменьшения емкости памяти микрокоманд, оно содержит второй блок памяти, второй мультиплексор, буферный регистр, второй блок маскирования и второй элемент И, первый и второй входы и выход которого подключены соответственно к второму тактовому входу устройства, второму выходу признака записи признаков модификации адреса регистра микрокоманд.и к входу записи-чтения второго блока памяти, адресный, информационный входы и выход которого соединены соответствен5 но с вторым выходом поля адреса загрузки признаков модификации адреса регистра микрокоманд, выходом второго блока маскирования и первым информационным входом второго мультиплексора, второй

10 информационный и управляющий входы которого соединены соответственно с выхо дом первого блока памяти и вторым выходом признака типа модификации адреса регистра микрокоманд, вторые выходы

15 поля адреса и поля маскирования которого соединены соответственно с первым информационным и управляющим входами второго блока маскирования, второй информационный вход которого соединен с

20 вторым информационным входом первого мультиплексора и выходом буферного регистра, информационный вход, синхровход и вход сброса которого соединен ы соответственно с выходом второго мультиплексора, 25 третьим тактовым и установочным входами устройства.

К2 нз

Н5

1767500

Н:4

L7::

Г"Л ) (3

-..9

Составитель Ю.Ленцов

Редактор Л.Волкова Техред М.Моргентал Корректор M.Ìàêñèìèøèíåö

Заказ 3549 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035. Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101