Устройство для умножения

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и предназначено для использования в универсальных и специализированных вычислительных устройствах . Цель изобретения - сокращение аппаратурных затрат за счет уменьшения числа колонок вычислительных ячеек и реализации коррекции результата, выполняемой введенной в устройство цепочкой элементов И. 5 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛ И СТИЧ Е С К ИХ

РЕСПУБЛИК (l9) () )) О05 G 06 F 7/52

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

Г)О ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

6 (21) 4694790/24 (22) 22;05.89 (46) 23.10.92. Бюл. f .3 (71) Харьковский as o чобильно-дорожный институт им. Комсовк, i Украины (72) В.В.Шатилло, С,Н. прохоров и Л.С.Явиц (56) Самофалов К.Г. и др. Прикладная теория . цифровых автоматов. — Киев, Высшая школа, 1987; с.95, рис.4.6.

Патент США

М 4598382, кл. G 06 F 7/52, опублик, 1986.

Изобретение относится к цифровой вычислительной технике и предназначено для использования в универсальных и специализированных вычислительных устройствах.

Цель изобретения — сокращение аппаратурных затрат.

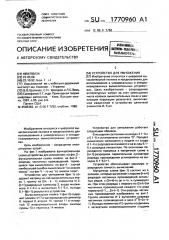

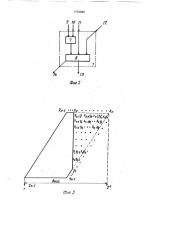

На фиг.1 изображена функциональная схема устройства для умножения; на фиг.2.— функциональная схема ячейки; на фиг.3— разряды частичных произведений, теряющиеся при вычислениях; на фиг.4 — случай наибольшей ошибки вычислений "со знаком минус"; на фиг 5 — то же "co знаком плюс".

Устройство для умножения (фиг.1) содержит матрицу из nxk вычислительных we.ек 1, группу из (2п - k - 1) элементов И 2, (и+1)-разрядный сумматор 3, входы множимого 4.1 — 4.п и множителя 5.1 — 5.п, выходы

6.1-6(k+1) результата устройства.

Вычислительная ячейка 1 (фиг:2) содержит элемент И 7 и одноразрядный сумматор

8, первый 9, второй 10, третий 11 и четвертый 12 информационные входы. выходы суммы 13 и переноса 14 ячейки. (54} УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ (57) Изобретение относится к цифровой вычислительной технике и предназначено для использования в универсальных и специализированных вычислительных устройствах. Цель изобретения — сокращение аппаратурных затрат за счет уменьшения числа колонок вычислительных ячеек и реализации коррекции результата, выполняемой введенной в устройство цепочкой элементов И. 5 ил.

Устройство для умножения работает следующим образом.

В исходном состоянии на входах 4, 1-4,л и 5.1-5.п установлены сигналы "0". Процесс вычисления начинается с подачи нэ. входы

4,1-4 и разрядов множимого и на входы 5.15,п разрядов множителя. По. окончании переходного процесса в матричной схеме и (и+1)-разрядном параллельном сумматоре разряды произведения установлены на выходах 6.1 — б.k+1.

Устройство обеспечивает минимум иразрядную точность вычислений.

Матричная схема (фиг.1) состоит из k колонок, которые вычисляют старшие (k-и+1) разрядов частичных произведений остальных рядов, с (2n-k)-го до n-ro, и суммируют их. При этом разряды с первого по (2п-М+й частичных произведений каждого 1-го ряда теряются (И,...,2п-k-1). Эти разряды частичных произведений изображены нз фиг.3

Группа элементов И 2 вычисляет )азряды частичных произведений в весе 2 (1=2п-k)1), Выходы элементов И 2 группы соединены с четвертыми информационными входами

1770960 (переноса) вычислительных ячеек 1 (!+1)-й колонки, имеющими вес 2. Таким образом разряды частичных произведений в весе 2 суммируются в основным результатом, вычисляемым матричной схемой, с весом 2. В 5 результате этого, если в !-м ряду (i=-1,l) разряд частичного произведения с весом 2 равен нулю, а разряды с меньшими весами равны единице, возникает "частичная" ошибка "со знаком мин1ус". Аналогично, ес- 10 ли разряд с весом 2 равен единице, а разряды с меньшими весами равны нулю, возникает "частичная" ошибка "со знаком плюс", Благодаря тому, что ошибки со знаком "плюс" и "минус" в разных радах частич- 15 но компенсируют друг друга, полная ошибка результата вычислений уменьшается, Применение такого подхода вызывает в общем случае появление ошибки, изменяю- 20 щейся в зависимости от величины операндов от максимальной "со знаком минус" до максимальной "со знаком плюс", со средним значением, равным нулю, Максимальная ошибка "со знаком ми- 25 нус" получается, когда максимальное число

"частичных" ошибок "со знаком минус" не компенсируется "частичными" ошибками

"со знаком плюс", т,е. когда разряд част1 чного произведения каждого ряда в весе 2 30 равен. нулю, а возможно большее число разрядов с меньшими весами этого частичного произведения равно единице. Этот случай отражен на фиг.4. Кружками обведены разряды частичных произведений, которые в 35 сумме создают ошибку.

Для определения величины ошибки суммируют "частичные" ошибки всех рядов, полагая нечетным;

40 е-=(2 +2 +...+2}+(2 +2 +... ...+ 2 + О)+ ... +)2 2 + 0 + ... +... + 0 +

+ 0)= — 2 2I2 4214+ +21 (1)

2 2

Чтобы определи-ь величину е-, переходят к более простому выражению, превышающему по величине е+. 50

I = — 2 2I-2 + - 22I 4+ + — 221 (2)

2 2 "" 2

Выражение (2) является частичной суммой бесконечн0 убы.вающей геометрической 55 прогрессии, полная сумма которой равна ! — 2 1-2

$- 4 1-2.2 -2 (3)

1 2 2 !

Таким образом, справедливо неравенство е- < е- < S =-.

I.уе < 3(i-г)г -3

Случай, приводящей к наибольшей ошибке

"со знаком плюс", противоположен вышеизложенному случаю наибольшей ошибки "со знаком минус". Она возникает, когда максимальное число "частичных" ошибок "со знаком плюс" не компенсируешься "частичными" ошибками "со знаком минус", Этот случай отражен на фиг.5. Максимальная ошибка

"со знаком плюс" несколько отличается по абсолютной величине от максимальной ошибки "со знаком минус", но не превышает

S по выражению (3). Таким образом. справедливы соотношения е- =е-, + i< — 3(i-2) 4

Максимальная относительная ошибка, возникающая при вычислениях в предлагаемом устройстве для 24-разрядных чисел с плавающей запятой (считая, что число отброшенных колонок i= 241. определяется из соотношения

4,7Р. 21 е+ 3 - 224.81

2 — 2О, 19

IImln /min 223.223 246

Етах=

21 е+. 3 22 2

Е пих=

Xmin dmin 223.223 223

Формула изобретения устройство для умножения, содержащее матрицу из nxk вычислительных ячеек (где и — разрядность операндов, k — количество колонок в матрице, k = (n+int(tag2n)-3) и

Таким образом, предлагаемое устройство обеспечивает по меньшей мер» 20-разрядную точность, в отличие от устройства-прототипа, обеспечивающего лишь 18-разрядную точность.

Отсюда следует, что для обеспечения такой же точности. как в устройстве-прототипе. предлагаемое устройство тоебует на две колонки вычислительных ячеек меньше. чем устройство-прототип. При атом для данного примера максимальная относительная ошибка равна

1770960 (и - )-разрядный параллельный суммагор, причем первыи и второй входы (i,j}-и вычисли1ельной ячейки матрицы (! — номер строки, I=1 ...,и, j — номер столбца, j=1,...,п) со динены соответственно с входом I-ro разряда множимого и входом j-го разряда множителя устройства, третий вход р-й вычислительной ячейки, в каждой I-й колонке . а1пиц,I соединен соответственно с выходом суммы (р-1)-й вычислительной ячейки в каждой 1-й колонке матрицы р=2„.,п;

I=1,...,k), четвертый вход р-й вычислительной ячеики первого столбца магрицы соединен состветственно с выходом переноса (р-1)-й

"-ь.. ::--..исли гельной ячейки первого столбца матриць „третий вход первой вычислительной ячейки е кKа ждой 1-й колонке матрицы соединен с входом логического нуля устройства, выход суммы (n,j)-й вычислительной ячейки матрицы соединен соответственно с первым входом i-ro разряда (n+1) разрядно

ro параллельного сумматора. второй вход (и-"1;-го разряда котосого соединен с выходом переноса (1,1)-й вычислительной ячейки матрицы, выходы разрядов (n+1)-р-зрядного параллельного сумматора соединены соoTBeTcTB8Hko с выходами старших разрядов результата устройства, о т л и ч à ю щ е е с я гем, что, с целью сокращения аппаратурных затрат, в него введена группа из (2n-k-1)

5 элементов И, причем первый вход m-го элемента И группы соединен соответственно с входом (2п-k-m)-ro разряда множимого устройства (m=1,...,2ï-k-1), второй вод m-ro элемента И группы соединен соответственно с

0 входом m-ro разряда множителя устройства, выходы элементов И группы соединены с четвертыми входами соответствующих вычислительных ячеек — колонки матрицы, выход переноса (Ц)-й вычислительной ячейки

5 матрицы, кроме (n,j)-x вычислительных ячеек матрицы, соединен соответственно с четвертым входом (I+1,j)-й вычислительной ячейки матрицы, выход переноса (п,1)-й вычислительной ячейки матрицы соединен со2 0 ответственно с вторым входом (i 1)-разряда (и+1)-разрядного параллельного сумматора, выход суммы (I,n)-x вычислительных ячеек матрицы, кроме (n,n)-й вычислительной ячейки матрицы, соединен соответственно

25 с (и-k) выходами младших разрядов результата устройства.

177О9бО

910V

Хи " хг ° ° ° ° ° АЪ ьИ ««-«% «t-«9 4/, и% -з " 4%/° г Д е е е е в в /

/ е

/ в / ° ьх

/ °

) i

17709бО

1 1! i

Составитель Е.Мурзина

Техред M.Moðãåíòàë Корректор M.Êåðåöìàí

Редактор Г.Бельская

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина. 101

Заказ 3743 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКН1 СССР

113035, Москва, Ж-35, Раушская наб., 4/5