Устройство приема двоичной информации в последовательном коде

Иллюстрации

Показать всеРеферат

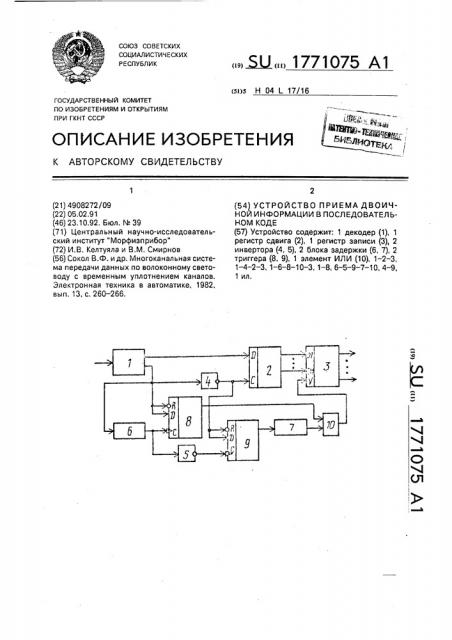

Устройство содержит: 1 декодер (1), 1 регистр сдвига (2), 1 регистр записи (3), 2 инвертора (4, 5), 2 блока задержки (6, 7), 2 триггера (8, 9), 1 элемент ИЛИ (10). 1-2-3, 1-4-2-3, 1-6-8-10-3, 1-8, 6-5-9-7-10, 4-9. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (ll) (sl)s н 04 L 17/16

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

"@..ь|., а „

- ®,„

Б щд

Яр"

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

О 4

Ql (21) 4908272/09 (22) 05.02.91 (46) 23.10.92, Бюл. М 39 .(71) Центральный научно-исследовательский институт "Морфизприбор" (72) И.В, Келтуяла и В.М. Смирнов (56) Сокол В.Ф. и др, Многоканальная система передачи данных по волоконному световоду с временным уплотнением каналов.

Электронная техника в автоматике, 1982, вып. 13, с. 260 — 266. (54) УСТРОЙСТВО ПРИЕМА ДВОИЧНОЙ ИНФОРМАЦИИ В ПОСЛЕДОВАТЕЛ6НОМ КОДЕ (57) Устройство содержит: 1 декодер (1), 1 регистр сдвига (2), 1 регистр записи (3), 2 инвертора (4, 5), 2 блока задержки (6, 7), 2 триггера (8, 9), 1 элемент ИЛИ (10). 1 — 2 — 3, 1-4-2-3, 1-6-8-10-3. 1-8, 6-5-9-7-10, 4-9, 1 ил.

1771075

Изобретение относится к технике связи, предназначено для приема двоичной информации в биимпульсном коде и может быть использовано в аппаратуре передачи данных.

Известны устройства, в которых синхросигналом служат короткие импульсы (см., например, статью Абрамова B.Â. и др. Радиотехника, 1982, % 2, с. 18-50). Они обеспечивают прием информации с низкой скоростью, поскольку передаваемый сигнал с укороченным синхроимпульсом имеет расширенную полосу частот, которая должна укладываться в ограниченную полосу пропускания канала передачи, Известны и другие устройства приема двоичной информации, в которых синхроимпульсами служат импульсы, запрещенные в используемом биимпульсном коде (см., например, статью Коровкин В.В., Пермиков С.В„Таценко В.Г. Радиотехника, 1986, N6,,с. 79 — 81; пат. Великобритании N.

2180712;. пат. США N 4276656).

Наиболее близким к заявляемому по технической сущности и наиболее быстродействующим является устройство приема, известное из статьи В.Ф. Сокол и др. (Многоканальная система передачи данных по волоконному световоду с временным уплотнением каналов, Электронная техника в автоматике, 1982, вып 13, с. 60 — 266).

В этой системе передачи синхросигналом служит длительная пауза,,имеющая низкий уровень, и следующая за ней "логическая 1" в биимпульсном коде.

Устройство содержит приемный блок (включающий светодиод и микросхемы А2, АЗ), выдел ител ь тактовых импул ьсов (микросхемы А1, А4, А7), триггер (Д1,1), схему управления (Д1,2, Д4), формирователь импульсов (Д2, ДЗ), счетчик (Д5, Д6,1), инвертор (Д6.2), регистр сдвига (Д8 — Д11) и регистр записи (Д12 — Д15).

Вход выделителя, S-вход триггера и первый вход формирователя подключены к выходам приемного блока соответственно.

R-входы триггера и схемы управления соединены с выходом инвертора. Тактовый и третий входы и первый выход схемы управления соединены с выходами выделителя и триггера и вторым входом формирователя соответственно. Вход счетчика подключен к второму выходу схемы управления и сдвиговому входу регистра сдвига, а выход — к входу записи регистра сдвига. Информационный вход регистра сдвига соединен с выходом формирователя, а информационные выходы — с информационными входами регистра записи соответственно.

Входом устройства является вход приемного блока, а выходами — выходы регистра записи.

Устройство приема работает следующим образом.

Приемный блок преобразует сигнал из линии связи в форму, пригодную для работы остальных блоков. Выделитель выделяет иэ полученного сигнала тактовые импульсы.

Триггер переходит в состояние "логическая

1" при поступлении на его S-вход первой

"логической 1" во входном слове, а после поступления импульса от инвертора на Rвход триггер возвращается в состояние "логический 0". Схема управления пропускает тактовые импульсы на свой выход при наличии "логической 1" на третьем входе и отсутствии импульса на R-входе.

Формирователь подформировывает импульсы входного сигнала для их записи в регистр сдвига. Счетчик считает тактовые импульсы и вырабатывает импульс переноса через число тактов, равное числу разрядов в слове, По этому импульсу происходит перезапись информации из регистра сдвига в регистр записи. Регистр сдвига сдвигает последовательный код, а регистр записи хранит параллельный код до поступления следующего слова. Для надежного восстановления синхронизации при поступлении первого же синхроимпульса в данном устройстве пауза должна иметь длительность не менее длительности слов данных, поскольку в противном случае ее нельзя гарантированно отличить от информационного слова. Таким образом, например, для передачи M=15 информационных разрядов требуется 2M+2=32 разрядов, содержащих информацию и синхросигнал. Такая избыточность понижает скорость передачи информации в известном устройстве е

2(М+1)/М оаз по сравнению с потенциальнс возможным. Цель изобретения — повыше. ние помехоустойчивости за счет ускорени установления синхронизации, Сущность изобретения заключается декодировании входных данных и выделе нии из них тактовых импульсов, последую щем сдвиге декодированных данных ь перезаписи их по сигналу, полученнному k результате сложения тактовых импульсов протактированных задержанными тактовы ми импульсами, с задержанным сигналом являющимся результатом тактирования ин вертированных тактовых импульсов выдер жанными и инвертированными тактовым импульсами.

На чертеже показана структурная схем, — пример конкретной реализации изобрете ния, 1771075 которого либо отсутствует синхрокомбинация, либо она сдвинута ближе к началу слова, чем в предыдущем слове.

40

50

Составитель Л.Синолицина

Техред M. Ìîðãåíòàë Корректор М.Андрушенко

Редактор

Заказ 3749 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101

Устройство содержит декодер 1, вход которого является входом устройства приема, регистр 2, сдвига, информационный вход которого соединен с информационным выходом декодера, регистр 3 записи, выходы которого являются выходами устройства, а информационные входы подключены к выходам регистра 2 соответственно, инверторы 4 и 5 (первый и второй соответственно), блоки 6 и 7 задержки (первый и второй соответственно), триггер 8 (первый объединенные инверсный R- u D-входы которого подключены к входам элемента 6 и инвертора 4 и тактовому выходу декодера 1, а С-вход — к выходу элемента 6 и входу инвертора 5, триггер 9 (второй), объединенные инверсный R- u D-входы которого соединены с выходом инвертора 4 и тактовым входом регистра 2, С-вход — с выходом инвертора 5, а выход — с входом элемента ИЛИ 10, входы которого подключены к выходам триггера 8 и элемента 7 соответственно, и выход — к входу записи регистра 3.

Устройство, реализующее изобретение, обеспечивает более высокую помехоустойчивость, выражающуюся в меньшей потере информации при сбое синхронизации, так как она устанавливается после первого же синхросигнала, в отличие от известного устройства, где синхронизация устанавливается после синхросигнала следующего за первым словом, в информационной части

5 Формула изобретения

Устройство приема двоичной информации в последовательном коде, содержащее первый инвертор, первый триггер, регистр сдвига, выходы которого соединены с ин10 формационными входами регистра записи, выходы которого являются выходами устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости путем ускорения установления синхрониза15 ции, в него введены второй инвертор, второй триггер, два блока задержки, элемент ИЛИ и декодер, вход которого является входом устройства, а информационный выход соединен с информационным входом

20 регистра сдвига, тактовый выход декодера соединен с инверсным R- и 0-входами первого триггера, через первый инвертор — c тактовым входом регистра сдвига и инверсным R- u D-входами второго триггера, а че25 рез первый блок задержки с С-входом первого триггера и входом второго инвертора, выход которого соединен с С-входом второго триггера, выход которого через второй блок задержки соединен с первым вхо30 дом элемента ИЛИ, второй вход которого соединен с выходом первого триггера, а выход — с входом записи регистра записи.