Источник опорного напряжения

Иллюстрации

Показать всеРеферат

Использование; в различных устройствах измерительной, вычислительной и радиоэлектронной аппаратуры с высокой стабильностью опорного напряжения источника . В устройство, содержащее выходной транзистор, эмиттерный повторитель, узел температурной компенсации, дифференциальный каскад, введены неинвертирующий усилитель с шунтирующим выходным каскадом, подключенным между выходной и общей шинами. Управляющий вход усилителя соединен с коллектором выходного транзистора. Введены также первый транзистор , база которого подключена к базе транзистора эмиттерного повторителя, а эмиттер - к выходу делителя опорного напряжения на двух резисторах, включенных между выходной и общей шинами. Коллектор первого транзистора через последовательно соединенные дополнительный резистор и второй транзистор в диодном включении соединен с выходной шиной, к которой подключен эмиттер третьего транзистора , и его база соединена с коллектором первого транзистора, коллектор третьего транзистора через ограничивающий резистор подключен к соединению базы дополнительного транзистора и коллектора транзистора дифференциального каскада. Практически исключен дрейф, обусловленный изменениями тока, потребляемого от питающего источника. 1 ил. сл с

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (si>s G 05 F 1/567

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР ф@®Щ

ОПИСАНИЕ ИЗОБРЕТЕНИ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4860072/07 (22) 1С.08,90 (46) 30.10.92. Бюл. М 40 (71) Всесоюзный научно-исследовательский институт электроизмерительных приборов (72) Е.В.Беконин (56) Авторское свидетельство СССР

М 408428, кл. 8 05 F 1/56, 1974, Авторское свидетельство СССР

ЬЬ 1146646, кл. G 05 F 3/22, 1985.

Авторское свидетельство СССР

N. 536484, кл. G 05 F 1/567, 1974. (54) ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ (57) Использование; в различных устройствах измерительной, вычислительной и радиоэлектронной аппаратуры с высокой стабильностью опорного напряжения источника. В устройство, содержащее выходной транзистор, эмиттерный повторитель, узел температурной компенсации, дифференциальный каскад, введены неинвертирующий усилитель с шунтирующим выходным

Изобретение относится к электротехнике и может быть использовано в различных устройствах измерительной, вычислительной и радиоэлектронной аппаратуры.

Известен низковольтный источник опорного напряжения,, выполненный на двух транзисторах и двух резисторах, При этом коллектор выходного транзистора соединен с одним выводом источника, а эмиттер — с другим выводом, Недостатком известного устройства является значительный дрейф выходного напряжения, обусловленный изменениями тока, протекающего через источник (выходной транзистор)... Ж 1772796 А1 каскадом, подключенным между выходной и общей шинами. Управляющий вход усили- теля соединен с коллектором выходного транзистора. Введены также первый транзистор, база которого подключена к базе транзистора эмиттерного повторителя, а эмиттер — к выходу делителя опорного напряжения на двух резисторах, включенных между выходной и общей шинами. Коллектор первого транзистора через последовательно соединенные дополнительный резистор и второй транзистор в диодном включении соединен с выходной шиной, к которой подключен эмиттер третьего транзистора, и его база соединена с коллектором первого транзистора, коллектор третьего транзистора через ограничивающий резистор подключен к соединению базы дополнительного транзистора и коллектора транзистора дифференциального каскада. Практически исключен дрейф, обусловленный изменениями тока, потребляемого от питающего источника. 1 ил.

Существенно меньший дрейф выходно- ЬЭ го напряжения обеспечивает низковольтный опорный элемент, в котором в со сравнении с известным устройством, допол- Ос, нительно введены третий и четвертый резисторы, второй и третий транзисторы.

Недостатком укаэанного ниэковольтного опорного элемента является наличие составляющей дрейфа выходного напряжения, обусловленной изменениями тока базы второго транзистора. протекающего через первый резистор, Наиболее близким K изобретению является источник опорного напряжения, содержащий транзисторы, два последовательно 172796 включенных транзистора с закороченными коллектор-базовыми переходами, причем коллектор одного из транзисторов соединен с резистором и базой транзистора, включенного по схеме эмиттерного повторителя, а его эмиттер соединен с базой выходного транзистора, эмиттер которого соединен с одной из выходных шин, дифференциальный каскад на транзисторах и дополнительный транзистор, при этом базы транзисторов дифференциального каскада соединены с коллекторами выходного транзистора и транзистора эмиттерного повторителя, в эмиттерную цепь которого включен переход коллектор-эмиттер дополнительного транзистора, а база указанного транзистора подключена к коллектору одного из транзисторов дифференциального каскада, эмиттерный резистор которого подключен к другой выходной шине.

Недостатком прототипа является снижение стабильности за счет дрейфа опорного напряжения, обусловленного изменениями тока, потребляемого источником от питающего устройства.

Цель изобретения — повышение стабильности опорного напряжения источника, Это достигается тем, что в источник опорного напряжения, содержащий транзисторы, два последовательно вклю:-;енных транзистора с закороченными коллекторбазовыми переходами, причем коллектор одного из транзисторов соединен с резистором и базой транзистора, включенного по схеме эмиттерного повторителя, à его эмиттер соединен с базой выходного транзистора, эмиттер которого соединен с одной из выходных шин, дифференциальный каскад на транзисторах и дополнительный транзистор, при этом базы транзисторов дифференциального каскада соединены с коллекторами выходного транзистора и транзистора эмиттерного повторителя, в эмиттерную цепь которого включен переход коллектор-эмиттер дополнительного транзистора, а база указанного транзистора подключена к коллектору одного из транзисторов дифференциального каскада, эмиттерный резистор которого подключен к другой выходной шине, введены неинвертирующий усилитель с шунтирующим выходным каскадом, подключенный между выходными шинами и управляющим входом соединенный с коллектором выходного транзистора, первый транзистор, база которого подключена к базе транзистора эмиттерного повторителя, а эмиттер подключен к выходу введенного елителя опорного напряжения на двух резисторах, включенного змиттерный резистор 11 подключены к выходной шине.

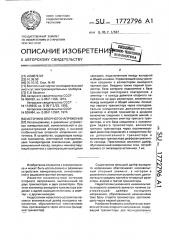

База транзистора 9 подключена к коллектору транзистора 2 эмиттерного повто40 рителя и через резистор смещения 12 к выходной шине, а коллектор транзистора 9 соединен с общей шиной. Коллектор транзистора 10 через резистор 13, с которого снимается сигнал управления на базу до45 полнительного транзистора 14, подключен к общей шине. Дополнительный транзистор

14 эмиттером подключен к общей шине, а коллектором — к соединению базы выходного транзистора 1 и эмиттера транзистора 2.

50 База транзистора 10 соединена с коллектором выходного транзистора 1 через резистор 15, и через резистор 16 подключена к выходной шине.

Первый транзистор 11 базой подключен

55 к базе транзистора 2, а эмиттером к выходу делителя опорного напряжения на резисторах 10, 19, включенного между выходной и общей шинами. Коллектор первого транзистора 17 через последоватсльно соединенные дополнительный резистор 20 и второй

35 между выходной и общей шинами, коллектор первого транзистора через введенные последовательно соединенные дополнительный резистор и транзистор в диодном включении — с выходной шиной, к которой подключен эмиттер введенного третьего транзистора, база которого соединена с коллектором первого транзистора, коллектор третьего транзистора через ограничивающий резистор подключен к точке соединения базы дополнительного транзистора с коллектором транзистора дифференциального каскада.

На чертеже приведена принципиальная электрическая схема предлагаемого источника опорного напряжения, Источник опорного напряжения содержит выходной транзистор 1, база которого подключена к эмиттеру эмиттерного повторителя на транзисторе 2, а змиттер соединен с общей шиной. Коллектор выходного транзистора 1 соединен с управляющим входом 3 неинвертирующего усилителя с шунтирующим выходным каскадом 4, который подключен между выходной и общей шинами. База эмиттерного повторителя на транзисторе 2 подключена к последовательно соединенным транзисторам 5, 6 в диодном включении и резистору 7, соединенному с общей шиной, Через резистор 8 база транзистора 2 эмиттерного повторителя подключена к выходной шине.

Транзисторы 9, 10 образуют дифференциальный каскад, эмиттеры этих транзисторов соединены между собой и через

1772796

30 транзистор 21 в диодном включении соединен с выходной шиной, к которой подключей эмиттер третьего транзистора 22, à его база соединена с коллектором первого транзистора 17. Коллектор третьего транзистора 22 через ограничивающий резистор

23 подключен к точке соединения базы дополнительного транзистора 14 с коллектором транзистора 10 дифференциального каскада.

Конденсаторы 24, 25 препятствуют самовозбуждению схемы и снижают уровень шумов на выходе источника опорного напряжения.

Источник опорного напряжения работает следующим образом, При включении питающего устройства (подаче питающего напряжения через внешний резистор к выходной шине) по мере нарастания опорного напряжения транзисторы 1, 2 и 5, 6 приоткрываются благодаря току, протекающему через резистор 8 в базы указанных транзисторов, При этом первый транзистор 17 оказывается в открытом состоянии, так как напряжение на его базе находится на уровне 1,1 — 1 2 В как сумма напряжений переходов эмиттер-база транзисторов 1 и 2, а его эмиттер будет под потенциалом не более 0,5 — 0,6 В, определяемым выбором соответствующего коз рфициента деления делителя опорного напряжения на резисторах 18, 19. Благодаря этому по дополнйтельному резистору 20 и второму транзистору 21 в диодном включении течет ток, создающий падение напряжения, отпирающее третий транзистор 22.

Коллекторный ток транзистора 22, протекая через ограничивающий резистор 23 и резистор 13, создает на последнем падение напряжения, открывающее дополнительный транзистор 14, Коллекторный ток транзистора 14, протекая по резистору смещения 12, создает падение напряжения, отпирающее транзистор 9, запуская тем самым дифференциальный каскад на транзисторах 9, 10.

При этом опорное напряжение еще увеличится и возрастет напряжение на выходе делителя на резисторах 18, 19, что приведет к уменьшению напряжения на переходе база-змиттер первого транзистора 17, который в результате начнет подзапираться. И, наконец, при определенном значении опорного напряжения, зависящем от выбранного коэффициента деления делителя на резисторах 18, 19, первый транзистор 17 будет закрыт. В результате второй 21 и третий 22 транзисторы также запираются и дополнительный транзистор 14 будет управляться только с выхода дифференциального каскада.

При этом схема выходит на режим стабилизации, а опорное напряжение окончательно устанавливается до значения, равного

Ra

Up = 1)бэ1 + 0бз2 + Uj, (1)

Я7 где 0бз1 v 0бэ2 — падения напряжений на переходах база-эмиттер соответственно транзисторов 1 и 2;

07 — падение напряжения на резисторе 7:

Ят и Йэ — значения сопротивлений соот ветственно резисторов 7 и 8.

Сигналы управления дифференциальным каскадом на транзисторах 9, 10 снимаются с резисторов смещения 12, 16. Это дает возможность поддерживать постоянным отношение токов коллекторов выходного транзистора 1 и транзистора 2 эмиттерного повторителя благодаря отрицательной обратной связи, осуществляемой через дополнительный транзистор 14.

Причем даже изменения тока базы выходного транзистора 1, обусловленные, например, старением элементов, будут компенсированы при этом соответствующими изменениями колпекторного тока дополнительного транзистора 14, что повышает в целом стабильность опорного напряжения источника.

Кроме того, оказывается возможным существенно уменьшить ток эмиттера транзистора 2 эмиттерного повторителя и тем самым уменьшить дрейф опорного напряжения источника, обусловленный изменениями тока базы транзистора 2 эмиттерного повторителя, так как при этом нет необходимости поддерживать ток эмиттера транзистора 2 много большим по значению, чем ток базы выходного транзистора 1

Значения токов эмиттера транзисторов

1, 2 и 5, 6 выбираются таким образом, чтобы одновременно с вышеизложенным обстоятельством выполнялось условие, при котором суммарный отрицательный температурный коэффициент напряжения (TKH) переходов база-змиттер транзисторов

5 и 6 по абсолютному значению был больше суммарного отрицательного ТКН переходов база-эмиттер транзисторов 1 и 2, Тогда падение напряжения на резисторе 7 будет иметь положительный ТКН. Это достигается при обязательном условии, если выходной транзистор 1 работает при значительно большей плотности тока эмиттера, чем транзисторы 5, 6. При этом очев ",дно, что температурная компенсация опорного напряжения источника (т.е. нулевой ПКН опор1772796

20 ного напряжения), как следует из уравнения (1), будет определяться условием, при котором

1+ + Й7 0

Яв где у1 u p — значения ТКН переходов базазмиттер соответственно транзисторов 1 и 2;

)7- значение ТКН на резисторе 7.

В предлагаемом источнике ток эмиттера выходного транзистора 1 неизменен и практически не зависит от колебаний тока, потребляемого от питающего устройства, поскольку благодаря введенному неинвертирующему усилителю с шунтирующим выходным.каскадом 4, все изменения тока потребления происходят в этом каскаде, а ток, протекающий по управляющему входу

3 усилителя 4, много меньше тока змиттера транзистора 1.

Это. позволяет повысить стабильность опорного напряжения Uo, исключая его дрейф, обусловленный изменениями тока, потребляемого источником от питающего устройства.

Изобретение осуществляется по интегральной технологии или с использованием интегральных микросхем.

Предлагаемый источник опорного на. пряжения был реализован в виде гибридной интегральной микросборки в стандартном металлостеклянном корпусе типа 1203.148. Неинвертирующий усилитель, каскады на транзисторах 1,2,5,6, 14 и 17 выполнены на

4-х бескорпусных микросхемах К129НТ1В1, дифференциальный каскад и каскады на

"транзисторах 21, 22 — на микросхеме

КГ 90НТ5-4, шунтирующий каскад реализован на транзисторе КТ214Д-1.

Формула изобретения

Источник опорного напряжения, содержаший цепь иэ последовательно соединенных двух транзисторов с закороченными коллектор-базовыми переходами, включен25

145 ную между выходной и общей шинами, причем коллектор одного из транзисторов соединен с базой транзистора, включенного по схеме змиттерного повторителя и эмиттером соединенного с базой выходного транзистора, эмиттер которого соединен с общей шиной, дифференциальный каскад на транзисторах и дополнительный транзистор, при этом базы транзисторов дифференциального каскада соединены соответственно с коллекторами выходного транзистора и. транзистора эмиттерного повторителя, в змиттерную цепь которого включена цепь коллектор-эмиттер дополнительного транзистора. база которого подключена к коллектору одного из транзисторов дифференциального каскада, змиттерный резистор которого подключен к выходной шине, отл и ч а ющ и йс я тем, что, с целью повышения стабильности опорного напряжения, в него введены неинвертирующий усилитель с шунтирующим выходным каскадом, подключенный между выходной и общей шинами и управляющим входам соединенный с коллектором выходного транзистора, первый транзистор, база которого подключена к базе транзистора змиттерного повторителя, а эмиттер подключен к выходу введенного делителя опорного напряжения на двух резисторах, включенного между выходной и общей шинами, коллектор первого транзистора через введенные последовательно соединенные дополнительный резистор и второй транзистор в диодном включении -оединен с выходной шиной, к которой подключен эмиттер введенного третьего транзистора, база которого соединена с коллектором первого транзистора, коллектор через введенный ограничивающий резистор подключен к точке соединения базы дополнительного транзистора с коллектором транзистора дифференциального каскада.

1772796

Составитель В,Ееконин

Техред M.Moðãåíòàë Корректор Л,Филь

Редактор

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101

Заказ 3846 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035. Москва, Ж-35. Раушская наб., 4/5