Устройство для выделения кадрового синхронизирующего слова

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике, может быть использовано в системах передачи цифровой информации для синхронизации приема непрерывного цифрового потока, разделенного на информационные кадры, и является усовершенствованием изобретения по авт. св.№ 1704146.Цель изобретения - уменьшение времени восстановления синхронизма. Устройство для выделения кадрового синхронизирующего словз дополнительно к основному устройству содержит триггер, двоичный счетчик, одновибраторы, элемент задержки, элементы ИЛИ. Предлагаемое устройство обеспечивает обнуление ячеек блока оперативной памяти после первого же обнаружения КСС, что исключает вероятность ложного срабатывания устройства после кратковременных срывов кадровой синхронизации и тем самым уменьшает время восстановления синхронизма.1 ил.

CO)03 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 6 06 F 1/12

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 р ( (61) 1704146 (21) 4907670/24 (22) 26.12,90 (46) 07.11.92, Бюл, ¹ 41 (75) B.È.ßðû÷ и А.M.Ðîìàøåíêîâ (56) Авторское свидетельство СССР

¹ 1704146 кл. 6 06 F 1/12, 1989, (54) УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ КАДРОВОГО СИНХРОНИЗИРУЮЩЕГО СЛОВА (57) Изобретение относится к автоматике, может быть использовано в системах передачи цифровой информации для синхронизации приема непрерывного цифрового потока, разделенного на информационные кадры, и является усовершенствованием

Изобретение относится к автоматике, может быть использовано в системах передачи цифровой информации для синхронизации приема непрерывного цифрового потока, разделенного на информационные кадры, и является усовершенствованием изобретения по авт. св. ¹ 1704146.

Цель изобретения — уменьшение времени восстановления синхронизма.

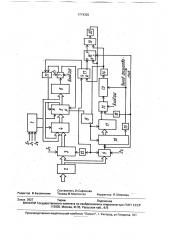

На чертеже представлена структурная схема устройства.

Устройство для выделения кадрового синхронизирующего слова содержит блок 1 управления, преобразователь 2 кода, формирователь 3 адресов, блок 4 оперативной памяти, реверсивный счетчик 5, блок 6 постоянной памяти, первый блок 7 сравнения, первый триггер 8, делитель 9 частоты, счетчик 10 формата кадра, генератор 11 кадрового синхронизирующего слова (КСС), второй блок 12 сравнения, счетчик 13 оши„, Ы„„1774325 А2 изобретения по авт. св.N 1704146,Цель изобретения — уменьшение времени восстановления синхронизма. Устройство для выделения кадровага синхрониэирующего слова дополнительно к основному устройству содержит триггер, двоичный счетчик, одновибраторы, элемент задержки, элементы

ИЛИ. Предлагаемое устройство обеспечивает обнуление ячеек блока оперативной памяти после первого же обнаружения КСС. что исключает вероятность ложного срабатывания устройства после кратковременных срывов кадровой синхронизации и тем самым уменьшает время восстановления синхронизма. 1 ил. бок, одновибратары 14, 15, элемент 16 задержки, второй триггер 17, двоичный счетчик 18, первый элемент ИЛИ 19, третий одновибратор 20, второй элемент ИЛИ 21, четвертый одновибратор 22.

В исходном состоянии при отсутствии входного цифрового потока на выходах преобразователя 2 кода присутствует двоичный код, соответствующий периоду появления элемента КСС среди элементов цифрового потока. Триггер 8 находится в состоянии

"лог,1" íà его инверсном выходе, что блокирует работу счетчика 10 формата кадра и генератора 11 КСС, Триггер 17 находится в состоянии "лог, 1" на его инверсном выходе и блокирует работу двоичного с <етчика 18.

На выходах одновибраторов 14, 15, 20, 22, присутствуют потенциалы "лог. 0", Устройство для выделения кадрового синхронизирующего cfloBB работает следующим образом.

1774325

На входы преобразователя 2 поступает код скорости передачи (ЦИ) или, что то же самое, код структуры цикла. Полученную входную информацию преобразователь 2 преобразует в код предварительной установки, который поступает на входы формирователя 3 адреса и делителя 9.

Формирователь 3 адреса на своих выходах последовательно формирует коды адресов, число которых равно кратности частоты следования КСС частоте появления символов

ЦИ, В исходном состоянии после включения напряжения питания блок 4 обнуляется (схема обнуления на чертеже не показана), Работа блока 1 управления заключается в том, чтобы при появлении на входе устройства информационного символа (элемента цифровой последовательности) сформировать на своем выходе два сигнала, обеспечивающих управление работой блоков 4 и 5.

Тактовый сигнал Г1 проходит на выход блока

1 управления, формируя тем самым сигнал предварительной установки формирователя 5 адреса, Следующий за тактом f> тактовый сигнал fg формирует сигнал записи в блок 4, Работа формирователя 3 адреса заключается в том, чтобы при появлении каждого последующего тактового сигнала, сопровождающего информационный символ, сформировать адрес для блока 4. В качестве основного элемента формирователя 3 адреа применяется двоичный счетчик, выходной код которого является адресом блока 4.

С приходом тактового импульса состояние двоичного счетчика изменяется и, соответственно, изменяется адрес блока 4.

Формирователь 3 адреса формирует заданное число адресов, соответствующее минимальному числу информационных символов, расположенных между символами КСС, т. е. на выходе счетчика присутствует линейно изменяющийся двоичный код, После формирования последнего адреса формирователь 3 адреса возвращается в исходное состояние и цикл его работы повторяется, т, е. он работает циклично в процессе поиска КСС.

В соответствии с адресом NA на выходе блока 4 появляется двоичный код Nc (в первый момент времени — нулевой), соответствующий числу совпадений кода КСС с элементами ЦИ. Этот код является кодом предварительной установки реверсивного счетчика 5, который формирует коды адресов блока 6, хранящего эталонное KCC.

Поступление цифровой информации на вход устройства сопровождается тактовыми сигналами Т и Т2, сдвинутыми относительно Т> на половину периода.

ro счетчика 5 проходит очередной тактовый

35 импульс, который вызывает его переполне40

5

Цикл работы в процессе поиска КСС не превышает длительности периода тактового сигнала. В каждом цикле работы с приходом тактового сигнала Т> изменяется NA, на выходе блока 4 при этом появляется код Nc, который по сигналу блока 1 управления переписывается в реверсивный счетчик 5. На выходе блока 6 при этом появляется соответствующий элемент КСС. В блоке 7 сравнения происходит сравнение элементов эталонного КСС и цифровой информации.

По спаду тактового сигнала Т1 на выходах блока 7 сравнения появляется сигнал совпадения (несовпадения), который проходит на счетный вход (или выход сброса через элемент ИЛИ 21) формирователя 5 адреса. Код

Ив с выхода реверсивного счетчика 5 поступает на входы данных блока 4 и по сигналу блока 1 управления переписывается в блок

4. Формирователь 3 адреса работает циклически, длина его цикла при этом n ° Т, Реверсивный счетчик 5 в каждом цикле работы устройства формирует адрес (номер элемента КСС) в зависимости от результатов сравнения в предыдущих и текущем цикле.

Через некоторое число циклов работы устройства в ячейке блока 4 с адресом NAi оказывается код Ncl, равный

Ncl = k-1 где k — число элементов КСС.

При совпадении в блоке 7 сравнения в текущем цикле последнего элемента КСС с элементом ЦИ на счетный вход реверсивноние и приводит к появлению на его выходе переполнения сигнала "лог.1". Этим сигналом триггер 8 переключается в единичное состояние. Переполнение реверсивного счетчика 5 свидетельствует о том, что в ЦИ обнаружен код КСС, После этого устройство переходит в режим поддержания синхронизма, В этом режиме сфазированный делитель 9 формирует на своем выходе сигналы с частотой, пропорциональной частоте появления КСС. Счетчик 10 формата кадра отсчитывает длину кадра, причем в процессе этого отсчета на выходах блока 11 появляется код КСС, который поэлемектно сравнивается с кодом КСС, поступающим в ЦИ, а результат сравнения стробируется сигналом с выхода элемента 16 задержки, Если число несовпадений, подсчитываемое счетчиком 13 ошибок, превысит некоторое пороговое значение, на выходе счетчика 13 появляется сигнал, запускающий одновибратор 24, выходным сигналом которого триггер 6 переключается в нулевое состояние, Устройство при этом переходит

1774325 в режим поиска КС0, Если число несовпадений не превышает порогового значения, по окончании отсчета длины кадра на выходе счетчика 10 появляется сигнал, запускаю-, щий одновибратор 15, Выходной сигнал од- 5 новибратора 15 является сигналом кадровой синхронизации.

После обнаружения КСС сигналом переполнения реверсивного счетЧика 5 триггер 17 переключается в состояние "лог. 1" 10 на его прямом выходе, и запускается одновибратор 22, который своим сигналом фази- . рует формирователь 3 адресов. Счетчик 18 начинает отсчет интервала до начала следующего КСС, по истечении которого сигна- 15 лом переполнения двоичного счетчика 18 через элемент ИЛИ 19 запускается одновибратор 20,своим выходным сигналом обнуляющий триггер 17 и двоичный счетчик 18. В процессе работы двоичного счетчика 18 триггер 17 20 сигналом "лог. 1" с прямого выхода через элемент ИЛИ 21 удерживает реверсивный счетчик 5 в нулевом состоянии. Таким образом, после обнаружения КСС и перехода устройства в режим поддержания синхро- 25 низма в ячейки блока 4 оперативной памяти заносится нулевая информация, т, е, ячейки блока 4 очищаются в интервале двумя соседними КСС.

Так как по истечении длительности кад- 30 ра блок 4 оперативной памяти приводится в нулевое состояние, то это позволяет начать поиск КСС без учета результатов, накопленных в предыдущем цикле поиска. Это исключает вероятность ложного переполнения 35 реверсивного счетчика 5 и тем самым уменьшает время установления синхронизма.

Формула изобретения

Устройство для выделения кадрового синхронизирующего слова по авт. св, N

1704146, о т л и ч а ю щ е е с я тем, что, с целью уменьшения времени восстановления синхронизма, в него введены второй триггер, двоичный счетчик, первый и второй элементы ИЛИ, третий и четвертый одновибраторы и элемент задержки, включенный между выходом делителя частоты и вторым входом второго блока сравнения, при этом выход переполнения реверсивного счетчика соединен с установочным входом формирователя адресов через третий одновибратор и с единичным входом второго триггера, инверсный выход которого соединен с входом разрешения двоичного счетчика, выход переполнения которого соединен с первым входом первого элемента

ИЛИ, выход которого через четвертый одновибратор соединен с входами установки в

"0" второго триггера и двоичного счетчика, синхровход двоичного счетчика соединен с выходом делителя частоты, выход второго одновибратора соединен с вторым входом первого элемента ИЛИ, первый выход первого блока сравнения соединен с первым входом элемента ИЛИ, второй вход которого соединен с прямым. выходом второго триггера, выход второго элемента ИЛИ соединен с выходом установки в "0" реверсивного счетчика, 1774325

Составитель И.Сафонова

Редактор В.Бугренкова Техред М,Моргентал Корректор И.Шмакова

Заказ 3927 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101