Микропрограммное устройство управления

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для -# построения блоков микропрограммного управления ЭВМ. Цель изобретения - сокращение емкости памяти микрокоманд. Указанная цель достигается за счет того, что устройство содержит блок 1 памяти микрокоманд , регистр 2 микрокоманд, модификатор 4 адреса, блок 5 коммутации логических условий, первый и второй элементы И 6 и 7, первый и второй счетчики 8 и 9 адреса, регистры 3, ТО адреса, мультиплексор 11 адреса и ключ 12. Такая организация устройства позволяет за счет применения развитой системы адресации уменьшить длину микропрограмм (количество микрокоманд), а за счет совмещения полей - уменьшить формат микрокоманды. 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (s <) s G 06 F 9/22

ГОСУДАР СТ В Е ННЫ и КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКР6!ТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

75 (21) 4336107/24 (22) 28.10.87 (46) 07.11.92. 6юл, М 41 (72) А.П.Акимов, О.И,Дапин, В,Б,Матвеев, Е.О, Поливода, A.Н Скворцов и А,У.Ярмухаметов (56) Машина вычислительная электронная цифровая ЕС1045. Процессор. Техническое описание ЩК1, 700. 026. Т02.

Машина вычислительная электронная цифровая ЕС1033. Процессор-каналы

ЕС2433. Техническое описание. Ч2.ПРЗ.

055. 014. Т01, . (54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО

УПРАВЛЕНИЯ (57) Изобретение относится к вычислительной технике и может быть использовано для

5U() 1774335 A 1 построения блоков микропрограммного упра аления Э В M. Цел ь изобретен ия — сокращение емкости памяти микрокоманд, Указанная цель достигается эа счет того, что

-устройство содержит блок 1 памяти микрокоманд, регистр 2 микрокоманд, модификатор 4 адреса, блок 5 коммутации логических условий, первый и второй элементы И 6 и 7, первый и второй счетчики 8 и 9 адреса, регистры 3, 10 адреса, мультиплексор 11 адреса и ключ 12. Такая организация устройства позволяет за счет применения развитой системы адресации уменьшить длину микропрограмм (количество микрокоманд), а за счет совмещения полей — уменьшить формат микрокоманды. 4 ил.

1774335

Изобретение относится к вычислительной технике и может быть использовано для построения блоков микропрограммного управления 3ВМ.

Цель изобретения — сокращение емко- 5 сти памяти микрокоманд.

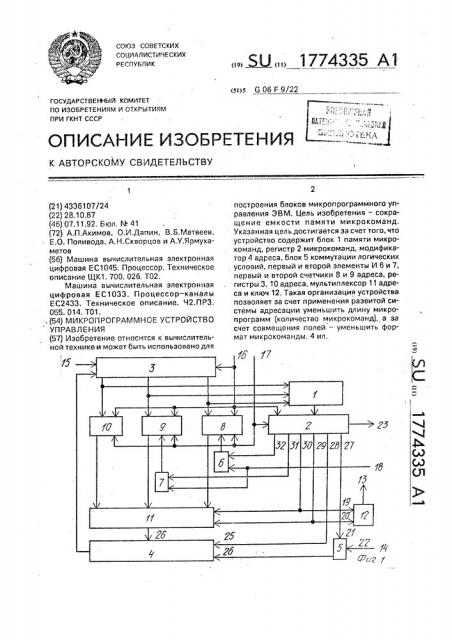

На фиг. 1 показана структурная схема устройства; на фиг. 2 — пример реализации модификатора адреса; на фиг. 3 — временная диаграмма поступления синхросигна- 10 лов; на фиг. 4 — пример формирования адреса следующей микрокоманды с помощью счетчиков, Устройство (фиг.1) содержит блок 1 памяти микрокоманд, регистр 2 микрокоманд, 15 первый регистр 3 адреса, модификатор 4 адреса, блок 5 коммутации логических условий, первый и второй элементы И 6 и 7, первый и второй счетчикй 8 и 9 адреса, второй регистр 10 адреса, мультиплексор 11 20 адреса и ключ 12, второй выход 13, вход 14 логических условий, второй 15 тактовый вход, установочный вход 16, первый 17 и третий 18 тактовые входы, управляющий вход 19 и информационный вход 20 ключа 25

12, управляющий 21 и информационный 22 входы блока 5, первый выход 23, первый информационный 24, управляющий 25 и второй информационный 26 входы модификатора 4, выход 27 поля анализа логических 30 условий регистра 2, выход 28 полл управления модификацией адреса регистра 2, группа выходов 29 совмещенного поля адресов и микроопераций регистра 2, выход 30 признака идентификации регистра 2, выходы 35

31, 32 признака режима адресации регистра

2, Модификатор 4 адреса (фиг. 2) может содержать группу элементов НЕ 33, группу элементов И 34 и группу элементов И/1И 35, На фиг.4 обозначено: А — переход по 40 счетчику 8;  — переход по счетчикам 8 и 9.

Блок 1 памяти является запоминающим устройством, хранящим Z-разрядные слова.

Первые S разрядов (S

Регистр 2 предназначен для хранения информации, считанной с выхода блока 1 памяти. Запись информации в регистр 2 осуществляется по сигналу с входа 17 устройства. на который поступают синхросиг- 55 налы (например, синхросерия С1).

Регистр 3 хранит адрес ячейки блока 1 памяти. Запись информации в регистр 3 осуществляется по синхросигналам (например синхросерия СЗ), поступающим с входа

15 устройства, Модификатор 4 адреса (фиг, 2) формирует адрес следующей микрокоманды,из адреса, поступающего с выхода мультиплексора

11 на вход 26, и признаков, поступающих с выхода блока 5 на вход 24, по сигналам маски, поступающим на вход 25 с выхода 28 регистра 2. При сигнале маски, равном "0", на выход модификатора 4 адреса проходит сигнал с входа 26, при сигнале маски, равном "1", — с входа 24.

Блок 5 пропускает на вход 24 модификатора 4 адреса признаки, поступающие на вход 22 по сигналу, поступающему на вход

21.

Элементы И 6, 7(по сигналам с выходов

32, 31 регистра 2) разрешают прохождение сигналов синхронизации с входа 18 устройства на счетные входы счетчиков 8, 9.

Регистр 10 в совокупности с первым и ,вторым счетчиками 8 и 9 формируют адрес следующей микрокоманды, записанной в блок 1 памяти. В регистре 10 формируется старшие разряды адреса, а в счетчиках 8, 9 — младшие разряды. Запись информации в регистр 10, в счетчики 8, 9 осуществляется сигналами, поступающими с входа 17 устройства (например синхросерия С1). Счетчики 8, 9 изменяют свое состояние на следующие по сигналам с входа 18 устройства (например синхросерия С2).

Мультиплексор 11 пропускает на вход модификатора 4 адреса либо адрес, сформированный регистром 10 и счетчиками 8, 9 (при поступлении управляющего сигнала, например "1", с выхода 30 регистра 2 на управляющий вход мультиплексора 11), либо адрес, записанный в регистре 2 (при поступлении управляющего сигнала, например "0", с выхода 30 регистра 2 на управляющий вход мультиплексора 11).

Временная диаграмма поступления синхросигналов приведена на фиг, 3. Синхросигналы С1, С2, С3 следуют последовательно друг за другом и разделены временными промежутками.

Вход 16 является входом установки начального состояния, например "0", в регистрах 2, 10 и счетчиках 8, 9 и определенного состояния регистра 3.

Безусловный режим адресации задается нулевыми значениями сигналов маски (поступающих на вход 25 модификатора

4 адреса с выхода 28 регистра 2). При этом адрес, поступающий с выхода мультиплексора 11 на вход 26 модификатора 4 адреса, передается без изменений на выход модификатора 4 адреса.

1774335

В режиме условной адресации сигналы маски (поступающие на вход 25 модификатора 4 адреса с выхода 28 регистра 2), соответствующие модифицируемым разрядам адреса, имеют значение "1". Немодифицируемым разрядам адреса соответствуют сигналы маски, равные "0". Модификация заключается в замене значений соответствующих разрядов адреса, который поступает с выхода мультиплексора 11 на вход 26 модификатора 4 адреса, значениями признаков, поступающих с выхода блока 5 на вход 24 модификатора 4, Выбор признаков, подаваемых в данном такте на модификацию адреса, из всех признаков логических условий, поступающих через вход 14 устройства, производится сигналом, поступающим на вход 21 блока 5 с выхода 27 регистра

2.

Адрес следующей микрокоманды может формироваться непосредственным заданием адреса в пределах всего объема блока памяти и адресацией по счетчикам; d — разрядному счетчику 8 и m — разрядному счетчику 9, Адрес микрокоманды состоит из двух частей: старшей — адреса страницы (под страницей понимается часть блока памяти объемом 2 ) и младшей — адреса внутри страницы. При адресации по счетчикам с помощью счетчиков 8 и 9 задается адрес внутри страницы.

Пример формирования адреса внутри страницы представлен на фиг, 4. С помощью счетчика 9 формируется номер строки страницы. Число строк в странице равно

2". С помощью счетчика 8 формируется номер ячейки памяти в строке. Длина строки равна 2 .

При способе формирования адреса по счетчикам ключ 12 пропускает на выход коды управляющих сигналов (микрооперэций) по сигналу "1" с выхода ЗО регистра 2, Микропрограммное устройство управления работает следующим образом.

Устройство приводится в исходное состояние по сигналу, поступающему через вход 16 устройства на установочные входы счетчиков 8, 9, регистра 10, 3, 2. При этом в регистр 3 заносится первый исполнительный адрес микропрограммы (нэ фиг. 1 вход занесения первого исполнительного адреса не показан). С выходов регистра 3 данный адрес поступает нэ адресные входы блока I памяти.

В каждом такте работы устройства на

его входы 17, 18, 15 подаются синхросигналы С1, С2, СЗ соответственно (см, фиг, 3).

В первом такте с поступлением на вход

17 устройства синхросигнала С1 происходит чтение микрокоманд из блока 1 памяти в регистр 2. Кроме того, по синхросигнэлу

С1, поступающему на вход записи регистра

10, производится перепись в регистр 10

5 старших разрядов адреса текущей микрокоманды, поступающих с соответствующего выхода регистра 3 на информационный вход регистра 10. Также по синхросигналу С1, . поступающему на входы записи счетчиков 9

10 и 8, производится перепись в счетчики 9 и 8 младших разрядов адреса текущей микрокоманды, поступающих с соответствующих выходов регистра 3.

По синхросигнэлу С2, поступающему на

15 вход 18 устройства при наличии на выходе

32 регистра 2 управляющего сигнала, поступающего на соответствующий вход элемента И 6, на его выходе вырабатывается сигнал, поступающий на счетный вход счет20 чика 8. По этому сигналу содержимое счетчика 8 увеличивается на единицу.

Аналогичным образом по синхросигналу С2, поступающему на соответствующий вход элемента И 7, и при наличии на выходе 31

25 регистра 1 управляющего сигнала, поступающего на соответствующий вход элемента

И 7, на его выходе вырабатывается сигнал, поступающий на счетный вход счетчика 9.

По этому сигналу содержимое счетчика 9

ЗО увеличивается на единицу, Переносы из старших разрядов счетчиков 8 и 9 игнорируются.

По синхросигналу СЗ, поступающему через вход 15 устройства на вход записи

35 регистра 3, производится запись в регистр

3 сформированного в данном такте адреса следующей микрокоманды, поступающей с выхода модификатора 4 адреса.

Формирование адреса следующей мик40 рокоманды производится на мультиплексоре 11. Способ формирования адреса следующей микрокоманды задается в текущей микрокоманде. Сигнал, задающий способ формирования адреса, поступает с

45 выхода 30 регистра 2 на управляющий вход мультиплексора 11.

Поступлением синхросигнала С3 завершается такт работы устройства. Затем все

50 повторяется.

При способе формирования адреса по счетчикам поле микрокомэнды, предназначенное для непосредственного задания адреса, используется для кодирования мик55 роопераций. При этом сигнал, задающий способ формирования адреса, идущий с выхода 30 регистра 2 на вход 19 ключа 12, разрешает прохождение кода микрооперэ ций с выхода 29 регистра 2 на вход 20 клю а

12 и далее на выход 13 устройства...

1774335

Формула изобретения

Микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр микрокоманд, первый регистр адреса, блок коммутации логических условий и модификатор адреса, причем выход модификатора адреса соединен с информационным входом первого регистра адреса, установочный вход которого соединен с установочным входом регистра микро- команд и является установочным входом устройства, выходы первого регистра адреса соединены с адресными входами блока памяти микрокоманд, выход которого соединен с информационным входом регистра микрокоманд, выход поля управления модификацией адреса которого соединен с управляющим входом модификатора адреса, первый информационный вход которого соединен с выходом блока коммутации логических условий, информационный и управляющий входы которого подключены соответственно к входу логических условий устройства и выходу поля анализа логических условий регистра микрокоманд, вход записи которого является первым тактовым входом устройства, второй тактовый вход которого подключен к входу записи первого регистра адреса, выход несовмещенного поля микроопераций регистра микрокоманд является первым выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью сокращения емкости памяти микрокоманд, оно содержит мультиплексор адреса, ключ, два элемента И,два счетчика адреса и второй регистр адреса, причем первый и второй выходы при"нака режима адресации реги.стра микрокоманд соединены с первыми входами соответственно первого и второго

5 элементов И, вторые входы которых соединены и подключены к третьему тактовому входу устройства, выходы первого- и второго элементов И соединены со счетными входами соответственно первого и второго счет10 чиков адреса, установочные входы которых соединены с установочным входом второго регистра адреса и подключены к установочному входу устройства, соответствующие выходы первого регистра адреса соединены

15 к соответствующим информационным входам второго регистра адреса и первого и второго счетчиков адреса, входы записи первого и второго счетчиков адреса и вход второго регистра адреса соединены между

20 собой и подключены к первому тактовому входу устройства, входы второго регистра— адреса и первого и второго счетчиков адреса подключены к первой группе информационных входов мультиплексора адреса, 25 вторая группа информационных входов которого соединена с группой выходов сонмещенного поля адресов и микроопераций регистра микрокоманд и группой информационных входов ключа, управляющий вход

30 которого соединен с управляющим входом мультиплексора адреса и с выходом признака идентификации регистра микрокоманд, выход ключа является вторым выходом устройства, выход мультиплексора подключен

35 к второму. информационному входу модификатора адреса.

Синхросигнм CI (вход I7)

Синхросигнал С2 (вход Т8), Синхросигнал С3 (вход IS) 1774335

Составитель Ю.Ланцов

Редактор В.Бугренкова Текред М,Моргентал Корректор С.Патрушева

Заказ 3927 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Латент", г. Ужгород, уп.Гагарина, 101