Устройство для прямого и обратного косинусного преобразования

Иллюстрации

Показать всеРеферат

Изобретение относится к построению устройств цифровой вычислительной техники и дискретной автоматики. Устройство вычисляет последовательность коэффициентов ДКП длиной К по известной последовательности отсчетов длиной N в кодере и обратное преобразование в декодере. Целью изобретения является сокращение аппаратных затрат за счет уменьшения объема памяти. Дискретный косинусный преобразователь содержит умножитель, сумматор функции, выходной регистр, регистр функции, счетчик и блок памяти, формирователь адреса. Новым является то, что введен формирователь адреса, позволяющий обращаться к ячейкам памяти в определенном порядке. Объем ПЗУ уменьшен в N/4 раза, число разрядов счетчика сокращено в 2 раза. 3 ил. сл с

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я) s G 06 F 15/347

ГОСУДАРСТВЕННЫИ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4389883/24 (22) 25.12.87 (46) 07.11.92. Бюл. N. 41 (71) Всесоюзный научно-исследовательский институт радиовещательного приема и акустики им. А.С.Попова (72) О.В.Михайлова и. Б.И.Шехтман (56) 1. Мурога С. Системное проектирование сверхбольших интегральных схем, М.: Мир, т. 2, с. 83, рис. 7.6.4.

2. Авторское свидетельство СССР

М 1711331, кл. Н 03 М 3/00, 1987. (54) УСТРОЙСТВО ДЛЯ ПРЯМОГО И ОБРАТНОГО КОСИНУСНОГО ПРЕОБРАЗОВАНИЯ (57) Изобретение относится к построению устройств цифровой вычислительной техниИзобретение относится к построению устройств цифровой вычислительной техники и дискретной автоматики. Оно может быть использовано в радиотехнике и связи, а именно: в цифровых системах радиовещания и многофункциональной связи, звукового стереосопровождения телевидения, записи, хранения и воспроизведения звуковых сигналов.

Целью изобретения является сокращение аппаратных затрат за счет уменьшения в N/4 раз объема блока памяти, где N— объем выборки реализации процесса.

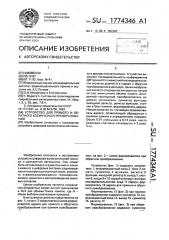

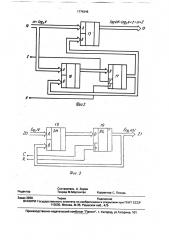

Блок-схема устройства представлена на фиг. 1; нв фиг. 2 представлена схема формирователя адреса для прямого и обратного преобразования при прямом преобраэова5U, 1774346 А1 ки и дискретной автоматики. Устройство вычисляет последовательность коэффициентов

ДКП длиной К по известной последовательности отсчетов длиной N в кодере и обратное преобразование в декодере. Целью изобретения является сокращение аппаратных затрат эа счет уменьшения объема памяти. Дискретный косинусный преобразователь содержит умножитель, сумматор функции, выходной регистр, регистр функции, счетчик и блок памяти, формирователь адреса.

Новым является то, что введен формирователь адреса, позволяющий обращаться к ячейкам памяти в определенном порядке.

Объем ПЗУ уменьшен в N/4 раза, число разрядов счетчика сокращено в 2 раза.

3 ил. нии; на фиг. 3 — схема формирователя при обратном преобразовании.

Устройство (фиг. 1) содержит умножитель 1, информационный вход 2, блок 3 памяти, сумматор 4 функции, регистр 5 функции, выходной регистр 6. выход 7, счетчик 8, входы 9 и 10 первой и второй тактовых последовательностей. вход 11 сброса, формирователь 12 адреса для прямого и обратного преобразования.

Формирователь 12 (фиг. 2) при прямом преобразовании содержит сумматор 13, информационный вход 14, выход 15, сумматор

16, регистр 17.

Формирователь 12 (фиг. 3} при обратном преобразовании содержит сумматор

1774346

18. регистр 19, информационный вход 20 и выход 21.

Устройство вычисляет последовательность коэффициентов дискретного косинусного преобразования (ДКП) У» по исходной 5 последовательности отсчетов Хл согласно выражению:

И вЂ” 1

Y»=- X С»Хп сов (1) 10 где V=0, 1, ..., К-1, К-й из коэффициентов

ДКП, которые представляют мгновенный спектр обрабатываемого сигнала;

15 п=О, 1, ..., ¹1, и-ый ИКМ отсчет в интервале преобразования;

К вЂ” количество коэффициентов ДКП;

N — обьем выборки (число отсчетов в интервале преобразования)

С»=- — при К=О;

С»=1 при К=1, 2, ..., К-1, и выполняет обратное преобразование восстановленной в декодере последова- 2 тельности коэффициентов спектрального и преобразования У» в блоки отсчетов Х согласно выражению: к — с

Xn=- Z С»У» cos. К (2) к =-о

Обычно

И=К=2, rn C (4, 5....)

На вход 9 устройства поступает такта- 35 вая последовательность, cooTBGTcTBóþùàë периоду подачи отсчетов на вход 2. На вход 10 поступает тактовая последовательность с периодом, r> К раз большим, чем на входе 9. 440

Для каждого коэффициента ДКП происходит перемножение умнажителем 1 всех N отсчетов, поступающих на информационный вход 2, на соответствующее значение

45 косинусов, записанных в блок 3 памяти. Со- 4 > гласно выра>кению (1), при вычислении всех (N.Ê) произведений достаточна использовать только 4N различных значений косину. са, т.е, косинус — функция периодическая, с йериодом 2к. В блок памяти записына|от 50 значения cos (К= 0, 1, ..., 4N-1) — всего ж К

4N значений, и с помощью формирователя

12 адреса организуют обращение к соответствующей ячейке памяти при вычислении соответствующего произведения.

В сумматоре 4 результат текущего умно>кения, поступающий на один вход сумматора 4 функции с выхода умно>кителя, складывается с результатол1 предыдущего умножения, записанным в регистре 5 функции в предыдущем такте.

В выходной регистр 6 последовательно записываются значения всех коэффициентов ДКП. Выход 7 регистра 6 является выходом устройства.

При вычислении К-го коэффициента

ДКП при переходе от одного произведения к следующему необходимо в каждом такте увеличивать адрес ячейки блока 3 памяти, из которой считывается значение косинуса, на 2К. При переходе к вычислению К+1-го коэффициента необходимо считывать значения косинусов с шагом 2К+2. Такой цикл обращения к нужным ячейкам обеспечивает формирователь 12 адреса.

Отметим, что при реализации обратного

ДКП согласно выражению (2) структурная схема устройства идентична схеме устройства ДКП, приведенной па фиг. 1, что вытекает из сравнения выражений (1) и (2).

Отличие заключается лишь в построении формирователя l2 адреса, т.к. при восстановлении и-го отсчета - см, выражение (2)

- необходимо при переходе от вычисления .текущего произведения к вычислению последующего увеличивать номер ячейки, из которой считывается соответствующее значение косинуса. на 2п+1.

Формирователь адреса, схема которого приведена HG фиг. 2, обеспечивает обращен»е к ячейкам блока памяти, номера которых определяются согласно выражению

К+2К и, п-О, 1, ÄÄ N-1 при вычислении К-го коэффициента ДКП при прямом ДКП.

Формирователь адреса, схема которого приведена на фиг. 3, обеспечивает обращение к ячейкам блока памяти, номера которых определяются согласно выражению (2п+1) К, К=-О, 1, ..., К-1 при вычислении и-го отсчета по восстановленным в декодере коэффициентам ДКП.

По сравнению с прототипом обьем памяти сокращен в N/4 раз и составляет 4N слов, число разрядон счетчика 8 сокращено н2 раза, Формула изобретения

1. Устройство для прямого и обратного косинусного преобразования, содержащее счетчик, блок памяти, умножитель, сумматор функции, регистр функции и выходной регистр, причем информационный вход устройства соединен с входом первого сомножителя умножителя, вход второго сомно>кителя которого соединен с выходом блока памяти, выход умножителя соединен с входом первого слагаемого сумматора функции, вход второго слагаемого которого соединен с выходом

177434б регистра функ) ии, и)4формационнhlй вход которого соединен с выходом сумматора функции и информационным входом выходного регистра, выход которого соединен с выходом устройства, вход первой тактовой последовательности которого соединен с входами синхронизации умножителя и регистра функции, вход установки о "0" которого соединен с входом синхронизации выходного регистра и входом второго тактовой последовательности устройства, вход сброса которого соединен с входом установки в

"0" счетчика. о т л и ч а ю щ е е с я тем, что, с целью сокращения аппаратных затрат за счет уменьшения в N/4 раз обьема блока памяти, где N — обьем выборки реализации процесса, оно содержит формирователь адреса для прямого и обратного преобразований, информационные входы с первого по

m-й разрядов которого соединен с выходами соответствующих разрядов счетчика, где

m=logzN, выходы с первого по (m+2)-й разрядов формирооателя адреса для прямого и обратного преобразований соединены с адресными входами соответствующих разрядов блока памяти, входы синхронизации и установки формирователя адреса для прямого и обратного преобразований соединены соответственно с входами первой и второй тактовых последовательностей устройства, вход второй тактовой последовательности которого соединен с входом синхронизации счетчика.

2. Устройство по п. 1, о т л и ч а ю щ е ес я тем, что формирователь адреса для прямого и обратного преобразований в режиме прямого преобразования содержит два сумматора и регистр, причел1 информационные входы с первого по m-й разрядов формирователя соединены с информационными входами соответствующих разрядов первого слагаемого первого и второго сумматоров, выходи с первого по (m+2)-й разрядов первого сумматора соединены с выходами соответствующих разрядов, вход синхронизации

5 которого соединен с входом синхронизации регистра, выходы с первого по (m+1)-й разрядов которого соединены с информационными входами соответственно с второго по (m+2}-й разрядов второго слагаемого перво10 ro сумматора и информационными входэл;и соответственно с первого по (m+1)-й разрядами второго слагаемого второго сумматора, выходы разрядов которого соединены с информационнычи входами соответствую15 щих разрядоо регистра, вход установки в "0" которого соединен с входом установки формирователя, вход логического нуля которого соединен с входом первого разряда второго слагаемого первого сумматора.

20 3. Устройство по ri. 1, о т л и ч а ю щ е ес я тем, что формирователь адреса для прямого и обратного преобразований в режиме обратного преобразования содержит сумматор и регистр, выходы с первого по (m+2)25 и разрядов которого соединены с выходами соответствующих разрядов формирователя и информационными входами соответствующих разрядов второго слагаемого сумматора, информационные входы с второго по

30 (и)+1)-й разрядов первого слагаемого которого соединены с входами соответственно с первого по rn-й разрядов формирователя, входы синхронизации и установки которого соединены с входами соответственно синх35 ронизации и установки в "0" регистра, информационные входы разрядов которого соединены с выходами соответствующих разрядов сумматора, информационный вход первого разряда первого слагаемого

40 которого соединен с входом логической единицы формирователя.

1774346

Составитель А. Зорин

Техред М,Моргентал Корректор С. Пекарь

Редактор

Заказ 392В Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035. Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент". г. Ужгород, ул.Гагарина, 101