Устройство цикловой синхронизации

Иллюстрации

Показать всеРеферат

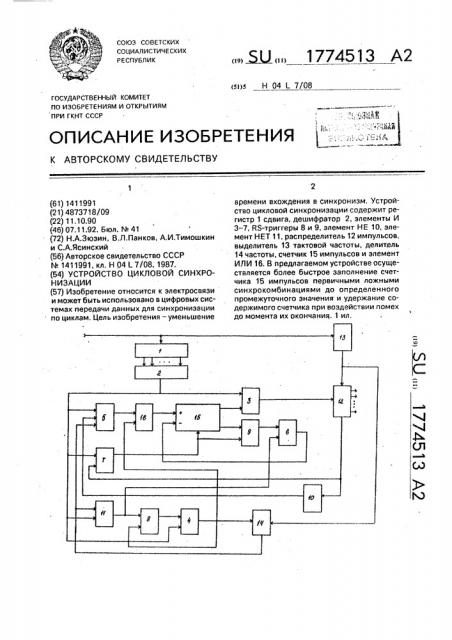

Изобретение относится к электросвязи и может быть использовано в цифровых системах передачи данных для синхронизации по циклам. Цель изобретения - уменьшение времени вхождения в синхронизм. Устройство цикловой синхронизации содержит регистр 1 сдвига, дешифратор 2. элементы И 3-7, RS-триггеры 8 и 9, элемент НЕ 10, элемент НЕТ 11, распределитель 12 импульсов, выделитель 13 тактовой частоты, делитель 14 частоты, счетчик 15 импульсов и элемент ИЛИ 16. В предлагаемом устройстве осуществляется более быстрое заполнение счетчика 15 импульсов первичными ложными синхрокомбинациями до определенного промежуточного значения и удержание содержимого счетчика при воздействии помех до момента их окончания. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛ ICTNVECKNX

РЕСПУБЛИК (si>s Н 04 1 7/08

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) 1411991 (21) 4873718/09 (22) 11.10.90 (46) 07,11.92, Бюл. N 41 . (72) Н.А.Зюзин, В.Л.Панков, А.И,Тимошкин и С.А.Ясинский (56) Авторское свидетельство СССР

М 1411991, кл, Н 04 1 7/08, 1987. (54) УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ (57) Изобретение относится к электросвязи и может быть использовано в цифровых системах передачи данных для синхронизации по циклам. Цель изобретения — уменьшение!

Ж,, 1774513 А2 времени вхождения в синхронизм. Устройство цикловой синхронизации содержит регистр 1 сдвига, дешифратор 2, элементы И

3-7, RS-триггеры 8 и 9, элемент НЕ 10, элемент НЕТ 11, распределитель 12 импульсов, выделитель 13 тактовой частоты, делитель

14 частоты, счетчик 15 импульсов и элемент

ИЛИ 16. В предлагаемом устройстве осуществляется более быстрое заполнение счетчика 15 импульсов первичными ложными синхрокомбинациями до определенного промежуточного значения и удержание содержимого счетчика при воздействии помех до момента их окончания, 1 ил.

1774513

Изобретение относится к электросвязи, может быть использовано в цифровых системах передачи данных для синхронизации по циклам и является усовершенствованием изобретения по авт.св. Иг 1411991, По основному авт.св. N 1411991 известно устройство цикловой синхронизации, содержащее элемент НЕ, пятый элемент И, последовательно соединенные регистр сдвига, дешифратор, первый элемент И и распределитель импульсов, последовательно соединенные выделитель тактовой частоты, делитель частоты, элемент НЕ, первый

RS-триггер и второй элемент И, последовательно соединенные второй RS-триггер и четвертый элемент И, последовательно соединенные третий элемент И и счетчик импульсов. При этом выход выделителя тактовой частоты подключен к тактовому входу распределителя импульсов, выход дешифратора — к первому входу третьего элемента И и объединенным вторым входам элемента НЕТ, второго элемента И и пятого элемента И, выход которого подключен к

R-входу второго RS-триггера входу "Сброс", счетчика импульсов, основной выход которого подключен к второму-входу первого элемента И, дополнительный выход подключен к S-входу второго RS-триггера, а дополнительный вход соединен с выходом четвертого элемента И. второй вход которого соединен с S-входом первого RS- p rreра, R-вход которого соединен с выходом второго элемента И и входом "Сброс" делителя частоты, выход цикловой частоты распределителя импульсов непосредственно и через элемент НЕ подсоединен соответственно к первому входу пятого элемента И и второму входу третьего элемента И, третий вход которого подключен к выходу делителя частоты, причем объединенные входы регистра сдвига и выделителя тактовой частоты являются входом устройства, а выходы распределителя импульсов являются выходами устройства.

Однако известное устройство имеет большое время вхождения в синхронизм.

Цель изобретения -уменьшение времени вхождения в синхронизм.

Указанная цель достигается тем, что в устройство цикловой синхронизации, содержащее счетчик импульсов, элемент НЕ; третий и пятый элементы И, последовательно соединенные регистр сдвига, дешифратор, первый элемент И и распределитель импульсов, последовательно соединенные выделитель тактовой частоты, делитель частоты, элемент НЕТ, первый RS-триггер и второй элемент И, последовательно соединенные второй RS-триггер и четвертый эле40. триггеры 8 и 9, элементы НЕ t0, элемент

HET 11, распределитель 12 импульсов, выделитель 13 тактовой частоты, делитель 14 частоты, счетчик 15 импульсов и элемент

ИЛИ 16.

5 t0

35 мент И. При этом выход выделителя тактовой частоты подключен к тактовому входу распределителя импульсов, выход дешифратора — к первому входу третьего элемента

И и объединенным вторым входам элемента

НЕТ, второго элемента И и пятого элемента

И, выход которого подключен к R-входу второго RS-триггера и входу "Сброс" счетчика импульсов, основной выход которого подключен к второму входу первого элемента И, дополнительный выход подключен к S-входу второго RS-триггера, а дополнительный вход соединен с выходом четвертого элемента И, второй вход которого соединен с

S-входом первого RS-триггера, R-вход которого соединен с выходом второго элемента

И и входом "Сброс" делителя частоты, выход цикловой частоты распределителя импульсов непосредственно и через элемент НЕ подсоединен соответственно к первому входу пятого элемента И и второму входутретьего элемента И, третий вход которого подключен к выходу делителя частоты, причем объединенные входы регистра сдвига и выделителя тактовой частоты являются входом устройства, а выходы распределителя импульсов являются выходами устройства, введен элемент ИЛИ, При этом третий элемент И и счетчик импульсов соединены последовательно через вновь введенный элемент ИЛИ, другой вход которого соединен с выходом второго элемента И, На чертеже изображена структурная электрическая схема предложенного устройства.

Устройство цикловой синхронизации содержит регистр 1 сдвига, дешифратор 2, первый 3, второй 4, третий 5, четвертый 6 и пятый 7 элементы И, первый и второй RSУстройство работает следующим образом. Входной цифровой сигнал поступает на вход регистра 1 сдвига и на вход выделителя

13 тактовой частоты. Поступающий цифровой сигнал, продвигаясь по разрядам регистра 1 сдвига в параллельном коде, поступает на входы дешифратора 2 и каждая комбинация символов, аналогичная синхронизирующей, вызывает формирование сигнала на его выходе. Если устройство цикловой синхронизации находится в состоянии синхронизма, сигнал с выхода дешифратора 2 совпадает с цикловым синхросигналом распределителя

12 импульсов, появляющимся один раз за цикл.

1774513

При их одновременном поступлении на пятый элемент И 7 íà его выходе появляется сигнал, сбрасывающий в нулевое состояние счетчик 15 импульсов и второй

RS-триггер 9, нулевой сигнал с выхода которого закрывает четвертый элемент И 6. При этом первый элемент И 3 находится в закрытом состоянии из-за отсутствия разрешающего сигнала с выхода счетчика 15 импульсов, Сигнал разрешения формируется только при поступлении на вход счетчика

15 импульсов числа импульсов, равного его коэффициенту счета. Кроме того, сигнал с выхода делителя 14 частоты также совпадает с инверсией сигнала с выхода распределителя 12 импульсов, а следовательно, и с сигналом, формируемым дешифратором 2.

Инверсия сигнала распределителя 12 импульсов с выхода элемента НЕ 10 закрывает третий элемент И 5 на время своей длительности.

Несовпадение по времени сигнала с выхода дешифратора 2 и сигнала цикловой частоты с выхода распределителя 12 импульсов является следствием сбоя циклового синхронизма или поражения цикловой синхрокомбинации помехой.

При сбое циклового синхронизма и iloявлении с выхода дешифратора 2 хотя бы одного (первого) сигнала, не совпадающего

ilo времени с цикловым синхросигналом, вырабатываемым распределителем 12 импульсов, сигнал с выхода элемента HET 11 устанавливает первый RS-триггер 8 в единичное состояние, и он открывает второй элемент И 4, подготавливая тем самым делитель 14 частоты к новому фазированию.

Если следующий (второй) сигнал с выхода дешифратора 2 вновь не совпадает по времени с сигналом на выходе распределителя

12 импульсов, делитель 14 частоты устанавливается в нулевое состояние и начинает вырабатывать сигнал цикловой частоты, сфазированный по данному (второму) сиг.налу отклика дешифратора 2, Одновременно этот (второй) сигнал через элемент ИЛИ

16 проходит на вход счетчика 15 импульсов, в который записывается первая единица.

Первый RS-триггер 8 при этом обнуляется и закрывает второй элемент И 4, Если следующий (третий) сигнал с выхода дешифратора 2 совпадает по времени с сигналом цикловой частоты с выхода делителя 14 частоты и не совпадает с сигналом на выходе распределителя 12 импульсов (ложная синхрокомбинация в результате проверки оказалась истинной), этот (третий) сигнал через открытый сигналом с выхода элемента НЕ 10 третий элемент И 5 проходит на вход счетчика 15 импульсов, который изменяет свое состояние на единицу. Дальнейшее подтверждение новой фазы делителя 14 частоты сигналами откликов дешифратора 2 на истинные синхрокомби5 нации сопровождается увеличением содержимого счетчика 15 импульсов на единицу.

Если (третий) сигнал с выхода дешифратора 2 не совпадает по времени с сигналом, сформированным делителем 14 частоты

10 (ложная синхрокомбинация оказалась действительно ложной), процесс срабатывания элемента НЕТ 11, первого RS-триггера 8, второго элемента И 4 повторяется, оканчиваясь каждый раз при обнаружении очеред15 ной ложной синхрокомбинации сбросом делителя 14 частоты в нулевое состояние и увеличением содержимого счетчика 15 импульсов на единицу.

При однократном поражении цикловой

20 синхрокомбинации помехой сигнал с выхода делителя 14 частоты проходит через элемент НЕТ 11 íà S-вход первого RS-триггера

8, который устанавливается в единичное состояние и открывает второй элемент И 4.

25 Независимо от того, будет или нет новое фазирование делителя 14 частоты, следующий сигнал отклика дешифратора 2 на истинную синхрокомбинацию совпадает по времени с цикловым синхросигналом рас30 пределителя 12 импульсов, поэтому на выходе пятого элемента И. 7 появляется сигнал, сбрасывающий счетчик 15 импульсов в нулевое состояние, При многократном подряд искажении

35 цикловой синхрокомбинации процесс срабатывания элемента НЕТ 11, первого RSтриггера 8, второго элемента И 4, делителя

14 частоты и элемента ИЛИ 16 повторяется, окачиваясь каждый раз увеличением содер40 жимого счетчика 15 импульсов на единицу до промежуточного значения а р .

Независимо от причин, вызвавших поиск состояния циклового синхронизма, при заполнении счетчика 15 импульсов до опре45 деленного промежуточного р значения на его втором выходе появляется сигнал, устанавливающий второй RS-триггер в единичное состояние. Открывается четвертый элемент И 6 и разрешает поступление сиг50 налов с выхода элемента НЕТ 11 на дополнительный вход счетчика 15 импульсов, обеспечивая тем самым ".îñëåäóþùóþ работу счетчика 15 импульсов в качестве реверсивного. Таким образом, после

55 достижения счетчиком 15 импульсов минимально допустимого оставшегося его объема обеспечивается анализ соотношения между поступающими искаженными и неискаженными синхрокомбинациями и за1774513

Составитель А, Тимошкин

Техред М.Моргентал Корректор M. Андрушенко

Редактор

Заказ 3936 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035. Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101 полнение счетчика 15 импульсов в случае преобладания неискаженных синхрокомби.+1 наций или удержание в промежуточном акр .-о состоянии в противном случае. Удержание

+1 счетчика в промежуточном акр -всостоянии обеспечивается за счет поочередной записи единичного сигнала с выхода элемента HET 11 через открытый четвертый элемент И 6 на дополнительный вход счетчика 15 импульсов и единичного сигнала с выхода второго элемента И 4 через элемент

ИЛИ 16 на основной вход счетчика 15 импульсов. В результате распределитель 12 импульсов сохраняет фазу сигналов до окончания воздействия сколь угодно долгих по времени помех на линейный сигнал, а после окончания воздействия помех для установления новой фазы распределителя 12 импульсов потребуется минимально необходимое время. Если после окончания воздействия помех состояние циклового синхронизма подтверждается, т.е. сигналы с выхода распределителя 12 импульсов и с выхода дешифратора 2 совпадают по времени, на выходе пятого элемента И 7 появля ется сигнал, который сбрасывает счетчик 15 импульсов и второй RS-триггер 9 в нулевое состояние, Промежуточное значение объема счетчика 15 импульсов надо выбирать, кроме того, равным среднему числу ложных синхрокомбинаций, определяемым длиной ис5 тинной синхрокомбинации, ее структурой и длиной цикла передачи. Этим учитывается то, что при вхождении в синхронизм.при незначительной вероятности искажения символов линейного сигнала счетчика 15 импульсов, на10 ходясь в режиме только суммирования и не подвергаясь сбрасыванию, увеличивает свое содержимое преимущественно за счет ложных синхрокомбинаций, а к моменту приема первой истинной синхрокомбина15 ции он с определенной вероятностью оказывается заполненным до промежуточного апр значения, При этом на проверку истинной синхрокомбинации на периодичность остается минимально необходимое время.

20 Формула изобретения

Устройство цикловой синхронизации по авт.св. % 1411991, о т л и ч а ю щ е е с я тем, что, с целью уменьшения времени вхождения в синхронизм, третий элемент И и счеr25 чик импульсов соединены последовательно через вновь введенный элемент ИЛИ, >ругай вход которого соединен с выходом второго элемента И.