Устройство для ввода информации

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано в автоматизированных системах управления для ввода и контроля информации от двухпозиционных датчиков. Цель изобретения - повышение достоверности ввода информации от двухпозиционных датчиков за счет организации их контроля и линии связи. Устройство содержит группы элементов нагрузки на резисторах 1-6, коммутаторы 7,8, блок управления 9, блок обмена 10, компараторы 11-13, триггеры 14-16, блок постоянной памяти 17, регистры 18, 19, блок оперативной памяти 20. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 G 06 F 13/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

l.,б

* :б.

ОПИСАНИЕ ИЗОБРЕТЕНИ

I» б»

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4804469/24 (22) 22.03.90 (46) 15.11.92. Бюл. ¹ 42 (71) Московский институт электронной техники (72) B.Â,Ïûñèí, Ю.А.Михайлов, Ю.И.Разумов и В.Н.Ануфриев (56) Авторское свидетельство СССР

¹ 1242972, кл. G 06 F 13/00, 1984. (54) УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ (57) Изобретение относится к автоматике и вычислительной технике и может быть ис Ы 1775723 Al пользовано в автоматизированных системах управления для ввода и контроля информации от двухпозиционных датчиков.

Цель изобретения — повышение достоверности ввода информации от двухпозиционных датчиков за счет организации их контроля и линии связи. Устройство содержит группы элементов нагрузки на резисторах 1 — б, коммутаторы 7,8, блок управления

9, блок обмена 10, компараторы 11 — 13, триггеры 14 — 16, блок постоянной памяти 17, регистры 18, 19, блок оперативной памяти 20.

3 ил.

1775723

Устройство относится к автоматике и вычислительной технике и может быть использовано в автоматизированных системах управления для ввода и контроля информации от двухпозиционных датчиков, Целью изобретения является повышение достоверности ввода информации от двухпозиционных датчиков за счет организации их контроля и линии связи.

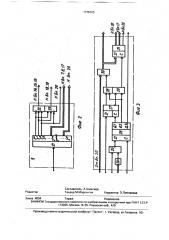

На фиг. 1 представлена структурная схема устройства для ввода информации; на фиг, 2 — представлена функциональная схема блока управления; на фиг. 3 — функциональная схема блока обмена, Устройство содержит с первой по шестую группы элементов нагрузки, выполненные на резисторах 1 — б, первый 7 и второй 8 коммутаторы, блок управления 9, блок обмена 10, с первого по третий компараторы

11 — 13, первый 14, второй 15 и третий 16 триггеры, блок постоянной памяти 17, первый 18 и второй 19 регистры, блок оперативной памяти 20.

Блок управления 9 (см.фиг.2) содержит счетчик 21, элемент ИЛИ вЂ” НЕ 22, элемент И

23, Блок обмена 10 (см,фиг.3) содержит селектор адреса 24, второй элемент ИЛИ вЂ” НЕ

25, третий регистр 26, четвертый триггер 27, со второго по четвертый элементы И 28 — 30, четвертый регистр 31, Устройство работает следующим образом.

На устройство подаются сигналы от двух групп датчиков: группа Р1, в которой при замыкании контактов подается значение входного напряжения, равное нулю, и группа Р2, в которой замыкание контактов обеспечивает подачу напряжения И1.

Переключение входных каналов производится последовательно коммутатором 7 в соответствии с адресом, выдаваемым блоком управления 9, Второй коммутатор 8 обеспечивает подключение входного делителя из резисторов 1,2,5 к источнику напряжения И1 для входов группы Р1 и из резисторов 3,4,6 для входов группы Р2. Напряжение с выходов коммутаторов 7 и 8 поступает на сигнальные входы компараторов 11,12,13, на вторые входы которых подаются опорные напряжения И2, ИЗ, И4.

Соотношение входных напряжений в каждом компараторе определяет значение выходного сигнала — единицу или ноль. В свою очередь значения напряжений на первых входах компараторов зависят от состояния датчиков, контактов реле и входной цепи. Для конкретной реализации устройства приняты следующие соотношения опорных напряжений И1 ИЗ И2 И4. При этом

30

35 на шину данных поступает содержимое блока памяти 20.

При выводе информации из микроЭВМ

50 резисторы входных делителей можно выбрать исходя из следующих соотношений:1+2 = 6; 3 = 2x1; 4 = 5.

В таблице приведены состояния датчиков и значения выходных сигналов устройства.

В блоке постоянной памяти 17 осуществляется преобразование кода выходных сигналов компараторов. Через регистры 18, 19 информация о состоянии датчиков в виде слова заносится в блок памяти 20.

Проверка работоспособности датчиков объекта управления и исправности входных цепей осуществляется путем задания соответствующего состояния объекта управления,Для этого системой управления формируются определенные контрольные воздействия на объект управления, в результате которых проверяется срабатывание датчиков.

Блок управления 9 выполняет функции распределения синхроимпульсов и формирователя адресов коммутаторов 7 и 8, блока постоянной памяти 17 и блока памяти 20, Блок обмена 10 обеспечивает обмен информацией междууправляющей микроЭВМ и устройством, Реализация обмена осуществляется по соответствующей шине обмена ЭВМ. Для конкретного примера реализации блока обмена 10 (фиг. 3) в случае ввода информации в микроЭВМ сигнал ввода/вывода, равный единице, с выхода элемента И 28 открывает элемент И 30, имеющий выход с открытым коллектором, и на шине данных устанавливается адрес ячейки памяти, которую предполагается считывать. Этот адрес заносится в регистр

31 сигналом с элемента 30.

Один из разрядов регистра 31 служит для формирования сигнала чтения памяти, остальные разряды соответствуют содержанию команда — включение или выключение соответствующего датчика.

По завершению обмена блок 10 вырабатывает сигнал квитирования обмена, По этому сигналу снимается информация с шин адреса и шины данных.

Таким образом, предлагаемое устройство обеспечивает более высокую достоверность вводимой информации.

Формула изобретения

Устройство для ввода информации, содержащее первый и второй коммутаторы, первый триггер, блок оперативной памяти, о т л и ч а ю щ е е с я тем, 470, с целью повышения достоверности вводимой ин1775723

0: .!спря::;-1о

: B. -".- ..!!; 1,; .:3-„-л -.ч,-.,-.ra .

I: 06р!1в Зло,4г1О. :

: 1..СВК

1 . т..Ск..,:. 1.спи

: В иПЯС11О

:3:(;;!эч11Г : В . .:! " 1О:!О

;, ;;)i!".ñ,.!:уь . Дьг, i!: o т формации, в него ведены нагрузочные элементы на резисторах с первой по шестой групп, блок управления, блок обмена, с первого по третий компараторы, второй и третий триггеры, блок постоянной памяти, первый и второй регистры, причем одни выводы резисторов первой и шестой групп соединены с общей шиной питания устройства. другие выводы резисторов первой группы соединены с соответствующими выводами резисторов второй группы и являются информационными входами первой группы устройства, другие выводы резисторов второй группы соединены соответственно с первой группой входов первого коммутатора, вторая группа входов которого соединена с одними выводами соответствующих резисторов четвертой группы, другие выводы которых соединены с соответствующими информационными входами второй группы устройства и одними выводами соответствующих резисторов третьей группы, другие выводы которых соединены с первой шиной источника питания устройства и одними выводами соответствующих резисторов пятой группы, другие выводы которых соединены соответственно с первой группой входов второго коммутатора, вторая группа входов которого соединена с выводами соответствующих резисторов шестой группы, адресные входы первого и второго коммутатора соединены с первой группой адресных выходов блока управления и первой группой адресных входов блока постоянной памяти, вторая группа адресных входов которого соединена с

)1.,тЧ ..П;ОВ ЯЗ110..1С11 1О ПОЛО .О:1,!с

ОСто-. . т: и. .1 ;-,:.". группой информационных выходов блока обмена, группа адресных выходов которого соединена с второй группой адресных входов блока оперативной памяти, вторые уп5 равляющие входы которого соединены с соответствующим выходом блока обмена, группа информационных входов которого соединена с выходами блока оперативной памяти, первая группа адресных входов ко10 торого соединена с второй группой адресных выходов блока управления, управляющий выход которого соединен с первым управляющим входом блока оперативной памяти, информационные входы ко15 торого соединены с выходами первого и второго регистров, информационные входы которых соединены с выходами блока постоянной памяти, третья группа адресных входов которого соединена с выходами пер20 вого, второго и третьего триггеров, информационные входы которых соединены с выходами соответствующих компараторов, сигнальные входы которых соединены с выходами первого и второго коммутаторов, а

25 входы опорного сигнала соединены соответственно с второй, третьей и четвертой шинами питания устройства. тактовые входы первого, второго и третьего триггеров соединены с первым тактовым выходом бло30 ка управления, второй тактовый выход которого соединен с тактовыми входами первого и второго регистров, тактовый вход устройства соединен с тактовым входом блока управления и тактовым входом блока обмена, 35 шина обмена которого соединена с шиной обмена с ЭВМ устройства.

0: I 6 0:;- еиспрсв11о рслс

0: I: C :.,â:;ñ.òð-,. яо Ос.-.с

: /11О Р о 7"::т"../

0: 0: OQD" гхо/ :-1D..

0: I 0: . с.-;-..О:!î

0 0 0:0С, -..1 .-,.:од:1о l

:нсл .

1775723

Редактор

Заказ 4034 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101 ф

Ч»

Составитель А.Алексеев

Техред М.Моргентал

Корректор Э.Лончакова