Усилитель-ограничитель тока

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и может быть использовано в интегральных аналоговых устройствах, Цель - изменение крутизны передаточной характеристики при одновременном снижении входного сопротивления . Задавая то или иное отношение площадей объединенных эмиттеров транзисторов 7 и 8, можно устанавливать требуемый вид нелинейности передаточной характеристики усилителя-ограничителя тока , 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

17758441 (si>s Н 03 К 5/08, Н 03 G 11/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Фиг. 1 (21) 48746 О/09 (22) 16.10,90 (46) 15.11,92. Бюл, ¹ 42 (75) В, Г. Прокопенко (56) Патент США № 4868429, кл, Н 03К5/08, 1989. (54) УСИЛИТЕЛЬ-ОГРАНИЧИТЕЛЬ ТОКА (57) Изобретение относится к радиотехнике и может быть использовано в интегральных аналоговых устройствах, Цель — изменение крутизны передаточной характеристики при одновременном снижении входного сопротивления, Задавая то или иное отношение площадей объединенных эмиттеров транзисторов 7 и 8, можно устанавливать требуемый вид нелинейности передаточной характеристики усилителя-ограничителя тока, 3 ил.

1775848

35 сопротивления

ЗО

50

Изобретение относится к радиотехнике и может быть использовано в интегральных аналоговых устройствах, Известен огранйчитель тока, содержащий выходной транзистор, выполненный по схеме с общей базой, к эмиттеру которого подключена переключательная диодная матрица, имеющая входы для приема опорных токов и входного тока.

Этот ограничитель така имеет следующие недостатки, Крутизна и характер нелинейности малосигнального участка передаточной характеристики данного ограничителя фиксированы и не могут быть изменены путем перестройки опорных токов или при изменении параметров элементов схемы, что сужает функциональные возможности ограничителя. Входное сопротивление ограничителя не остается малым во всем диапазоне изменения входного тока. В области порогов ограничения оно резко возрастает вследствие работы диодов переключательной диодной матрицы в режиме отпирания-запирания.

Также известен ограничитель выходного тока, содержащий токовое зеркало, напряжением питания которого служит входное напряжение, выход которого является выходом ограничителя, а вход соединен через импедансный двухполюсник с коллектором первого,транзистора, базовый ток которого задается источником постоянного тока. а эмиттер соединен с эмиттером второго транзистора, коллектор которого заземлен, а база подключена к источнику опорного напряжения.

Недостатками данного ограничителя являются невозможность электронного управления крутизной передаточной характеристики, а также высокое значение и непостоянство входного сопротивления, которое в области ограничения близко к сопротивлению запертого эмиттерного перехода второго транзистора, а в линейной области приблизительно равно сопротивле нию импедансного двухполюсника.

Наиболее близким по технической сущности к предлагаемому устройству является усилитель-ограничитель токй, содержащий первый транзистор, база которого является первым входом усилителя-ограничителя тока, эмиттер соединен с эмиттером второго транзистора и через первый генератор тока соединен с общей шиной. а также третйй, четвертый, пятый и шестой транзисторы, при этом база третьего транзистора соединена с базой четвертого и базой и коллектором пятого транзисторов и через второй генератор тока соединена с соответствующей шиной питания.

Недостатком данного усилителя-ограничителя тока является невозможность изменения крутизны передаточной характеристики: электронного управления крутизной малосигнального участка характеристики и задания требуемого вида ее нелинейности. Кроме этого, входное сопротивление усилителя-ограничителя тока не остается малым во всем диапазоне изменения входного тока, резко возрастая при достижении последним порогов ограничения.

Цель изобретения — изменение крутизны передаточной характеристики при одновременном снижениИ входного

Поставленная цель достигается тем, что в усилитель-ограничитель тока, содержащий первый транзистор, база которого является первым входом усилителя-ограничителя тока, эмиттер — соединен с эмиттером второго транзистора и через первый генератор тока соединен с общей шиной, а также третий, четвертый, пятый и шестой транзисторы, при этом база третьего транзистора соединена с базой четвертого и базой и коллектором пятого транзисторов, и через второй генератор тока соединена с соответствующей шиной питания, дополнительно введены седьмой, восьмой транзисторы и третий генератор тока, а первый и второй транзисторы выполнены двухэмиттерными, при этом второй эмиттер первого транзистора через третий генератор тока соединен с общей шиной и непосредственно — со вторым эмиттером второго транэистора, база которого соединена с эмиттером третьего и с коллектором и базой восьмого транзисторов и является вторым входом усилителя-ограничителя тока, а коллекторы первого и второго двухэмиттерных транзисторов являются первым и вторым выходами усилителя-дграничителя тока, эмиттер четвертого транзистора соединен с коллектором и базой седьмого транзистора и с базой первого двухзмиттерного транзистора, эмиттер пятого транзистора соединен с коллектором и базой шестого транзистора, причем коллекторы третьего и четвертого транзисторов, эмиттеры шестого, седьмого и восьмого транзисторов соединены с шинами питания, соответственно.

По отношению к прототипу заявляемое устройство имеет следующие новые существенные признаки: каждый из входов усилителя-ограничителя подключен к базе и коллектору одного транзистора в диодном включении и к эмиттеру второго транзистора, включенного по схеме с общей базой, база которого подключена к выходу источ1775848

55 ника напряжения смещения. образованного дяумя последовательно соединенными транзисторами в диодном включении и генератором постоянного тока, при этом выходная цепь ограничителя образована дифференциальным каскадом, выполненным на паре двухэмиттерных транзисторов.

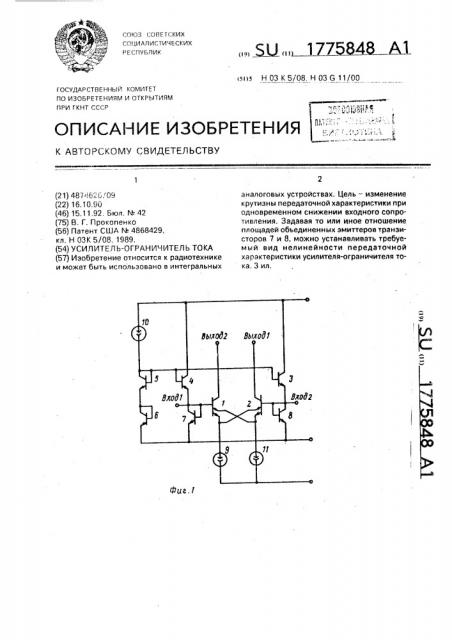

Достижение положительного эффекта обеспечивается следующим образом. Так как эмиттерные переходы транзисторов в диодном включении и транзисторов, включенных по схеме с общей базой, образующих входные цепи усилителя-ограничителя тока, открыты и включены встречно-параллельно по отношению к входному сигналу, исключается переход данных входных транзисторов в режим отсечки даже при существенном превышении входным током их токов смещения, Благодаря этому входное сопротивление усилителя-ограничителя остается низким во всем диапазоне изменения входного тока. Применение двухэмиттерных транзисторов в выходном дифференциальном каскаде позволяет задавать требуемый вид нелинейности передаточной характеристики, т.е. получать необходимую зависимость крутизны передаточной характеристики от уровня входного тока. Возможность изменения малосигнального значения крутизны передаточной характеристики обусловлена ее пропорциональностью отношению эмиттерных токов входных транзисторов и транзисторов выходного дифференциального каскада, На фиг, 1 приведена электрическая схема устройства, на фиг. 2 показано распределение токов в схеме усилителя-ограничителя тока при его работе; на фиг. 3 представлена передаточная характеристика ограничителя при трех различных соотношениях площадей эмиттеров двухэмиттерных транзисторов, Усилитель-ограничитель тока содержит первый 1, второй 2, третий 3, четвертый 4. пятый 5, шестой б, седьмой 7 и восьмой 8 транзисторы, первый 9, второй 10 и третий

11 генераторы тока.

Работу предложенного усилителя-ограничителя тока будем рассматривать при следующих допущениях: транзисторы 3-8 идентичны, транзисторы 1 и 2 отличаются только площадями эмиттеров, токи базы всех транзисторов пренебрежимо малы по сравнению с их токами коллектора, транзисторы работают на частотах, много меньших

f — граничной частоты коэффициента передачи транзисторов по току в схеме с общей базой а.

Первоначально подаются напрчженич на шины питания и токи генераторов тока такой величины, чтобы вывести все 1ранзисторы в активный режим. При этом транзисторы 3 — 8 имеют одинаковые токи эмиттера. ра ные току 101 генератора тока

10, а токи змиттеров транзисторов 1 и 2 определяются следую цими выражениями:

S11

111 = + 1ог:

112= +5 1Оз:

512 (1) 12 + 522

Sz1

1гт = + „ loz;

S22

Iгг = + 1оз, где 111, 112 — токи первого и второго эмиттеров транзистора 1 соответственно;

S11, S1z — площади первого и второго эмиттеров транзистора 1 соответственно;

121, 122 — токи первого и второго эмиттеров транзистора 2;

S21, S22 — площади первого и второго эмиттеров транзистора 2, I0z, lоз — токи генераторов тока 9 и 1! соответственно.

Входной сигнальный ток 1х, подаваемый на вход усилителя-ограничителя тока, равен (см. фиг. 2) сумме токов 14 и 17, протекающих через транзисторы 4 и 7 соответственно, а также сумме токов 1з и 18, протекающих через транзисторы 3 и 8.

1вх = 14 + 17 = 13 + 18 (2)

Связь между этими токами найдем из соотношения базо-эмиттерных напряжений транзисторов по замкнутым контурам, в соответствии со вторым законом Кирхгофа.

Сумма база-эмиттерных напряжений 06З5 и

06,6 транзисторов 5 и 6 равна сумме базозмиттерных напряжений 06g4 и 06gj транзисторов 4 и 7, а также сумме базо-эмиттерных напряжений Обзз.и Обэп транзисторов 3 и 8:

Обэ5+ Обзб = Обэ4+ Обэ7 = Обэз+ Обээ (3)

Разность базо-эмиттерных напряжений

Обэ11 и Обзг1 в цепи первых эмиттеров транзисторов 1 и 2 равна разности базо-эмиттерных напряжений Обэ12 и 06szz по вторым эмиттерам этих транзисторов, а также разности база-эмиттерных напряжений транзисторов 3 и 4 и транзисторов 7 и 8:

Обэ11 Обз21 = Обэ12 Обэ22 =

= Обэз Обэ4 = Обэ7 Обэб (4)

Представим базо-эмиттерные напряжения транзисторов с помощью уравнения

Эберса-Молла с точностью до величины обратного тока эмиттерного перехода I . При этом уравнение {3) примет следующий вид; р, ln — +p!и — -p, ln +

101 101 101 14

41 Is1 121

1775848

p In!

11 + !1

Is»!

12 + !2

= re)r In! S12!

01+ !з

= р, !и

Is1!

01 + !7

1S1

Ф1 !и!

21 !1

Is21!

22 !2!

$22 (7) in !01 !4

Is1

p, In!

01 !8!

81 где l1 — переменный ток,протекающий в цепи первых эмиттеров транзисторов 1 и 2, I2 — переменный ток,протекающий в цепи вторых эмиттеров транзисторов 1 и 2;

ls», !812 — обратные токи эмиттерных р-и-переходов первого и второго эмиттеров транзистора 1; Is21 !822 — обратные токи эмиттерных р-п-переходов первого и второго эмиттеров транзистора 2.

Преобразуя выражение (7), с учетом тоr0, что отношение обратных токов базоэмиттерных р-и-переходов равно отношению площадей их эмиттеров, а значит, отношению постоянных составляющих их эмиттерных токов, получим;

1 + — 1 +.---!

1 !

1 !12 !

21 l22 (8)

1+ — 1+— 3, !7 !

01 l01

1 — — 1 ——

lo1 lo1

Совместное решение уравнений (2) и (6)

ПОЗВОЛЯЕТ ВЫРазИтЬ !З. Ц, i7 и i8 ЧЕРЕЗ !вх .

4 l8=lo1 2 +1 — ч1 +(!вх )2

2 !01!

3=!7=!01 — "- — 1 + Ч . !вх 2 (9) (, -, () Сравнивая выражения (б). (8) и (9), получим:

l1 !2

1+— I + —— !

» !12!

1 — —--!

21!

1 -- —"!

+Fr lrl =pт In = +!

01 + I7 I01 + Io (5)!

01 !8

+ re)r ln - — — 1!

51 где р — температурный потенциал, Is1 — обратный ток эмиттерных переходов транзисторов 3 — 8.

Преобразовав (5) получим, 141-! -)(1+ -) =(1+! -)(1-! )(8) Уравнение (4) будет выглядеть так: (12) 30

35 =pl

2 lol

Из выражения (14) видно, что входное сопротивление имеет максимальное значение при !вх = 0 и уменьшается с ростом i».

Анализ зависимости (12) показывает, что при k = 1 участок передаточной характе50 ристики усилителя-ограничителя тока, соответствующий значениям входного тока, не превышающим по модулю 2 lol, близок к линейному, при k < 1 этот участок имеет

"выпуклый" характер, а при k > 1 — "вогну55 тый" (см, фиг. 3), В уравнение (12) входит коэффициент, равный отношению токов генераторов тока

10 и 9, 11: I02/lo1. Это позволяет изменять крутизну передаточной характеристики, изменяя соотношение укаэанных токов. При

5 (10)

Уравнение (10) позволяет найти зависимость I1 и !2 от !вх и, таким образом, величину выходного сигнального тока !ввх, который равен их сумме, 10 В симметричном варианте схемы предлагаемого усилителя-ограничителя тока, т.е. при выполнении условий:

S» = S22:

S12 = S21: (11)

15 I02 = I03, выходной ток равен:

?og

t rol

" 2 ., где k =(S» — S12

312

Определим входное сопротивление предлагаемого усилителя-ограничителя тока. Переменное напряжение на его входе равно разности база-эмиттерных напряжений транзисторов 3 и 4, а также 7 и 8;

1+ 3 !

О1

Овх = !-!бэз !)бэ4 = P In

1- и !

01

1 +(1вх )2+ !вх

2 !01 2 lo1 (13)

+(вх )2 !вх

2 lo1 2 lo1

ДИффЕРЕНЦИРУЯ Uax ПО !вх НайДЕМ ВХОД

) ное сопротивление усилителя-ограничите40 ЛЯ

» Pr (14)

d !вх !01

1775848

10 этом изменению тока lo> генератора тока 10 при фиксированном токе Im генераторов тока 9 и 11 соответствует изменение только крутизны малосигнального участка передаточной характеристики, без изменения порогов ограничения, равных + log, При фиксированном токе Io> и изменении тока

lm изменяются и пороги ограничения, которые увеличиваются вместе с увеличением крутизны, При одновременном изменении токов loi u Im (так, чтобы отношение Im/1оj оставалось постоФ ным) крутизна остается неизменной, изменяются только пороги ограничения выходного тока.

Таким образом, преимуществом заявляемого ограничителя тока по отношению к прототипу и аналогам является пониженное значение входного сопротивления, которое не претерпевает резких скачков в диапазоне изменения входного тока, а плавно уменьшается с его увеличением, а также возможность изменения крутизны передаточной характеристики путем выбора требуемого вида нелинейности малосигнального участка передаточной характеристики и электронного управления его крутизной.

Формула изобретения

Усилитель-ограничитель тока„содержащий первый транзистор, база которого является первым входом усилителя-ограничителя тока, эмиттер соединен с эмиттером второго транзистора и через первый генератор тока соединен с общей шиной, а также третий, четвертый, пятый и шестой транзисторы, при этом база третьего транзистора соединена с базой

5 четвертого и базой и коллектором пятого транзисторов, и через второй генератор тока соединена с соответствующей шиной питания, о т л и ч à ю шийся тем, что. с целью изменения крутизны передаточной характе10 ристики при одновременном снижении входного сопротивления, введены седьмой, восьмой транзисторы и третий генератор тока, а первый и второй транзисторы выполнены фвухэмиттерными, при этом второй

15 эмиттер первого транзистора через третий генератор тока соединен с общей шиной и непосредственно — с вторым эмитте ром второго транзистора, база которого соединена с эмиттером третьего и с коллектором и ба20 зой восьмого транзисторов и является вторым входом усилителя-ограничителя тока, а коллекторы первого и второго двухэмиттерных транзисторов являются первыми и вторыми выходами усилителя-ограничителя

25 тока, эмиттер четвертого транзистора соединен с коллектором и базой седьмого т ранзистора и с базой nepaoro двухэмиттерного транзистора, эмиттер пятого транзистора соединен с коллектором и базой шестого

30 транзистора, причем коллекторы третьего и четвертого транзисторов, эмиттеры шестого. седьмого и восьмого транзисторов соединены с шинами питания соответственно.

1775848

Составитель В. Прокопенко

Техред М.Моргентал Корректор B. Петрами

Редактор

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 4041 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, ?К-35, Раушская наб., 4/5