Вычислительная система

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для использования в многопроцессорных вычислительных комплексах высокой производительности. Цель изобретения - повышение производительности на скалярных и векторных вычислениях и сокращение времени выполнения управляющих воздействий. Система выполнена в виде следующих модулей устройства - 1-1-1-8 общей оперативной памяти, цент

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (я)з G 06 F 15/16, 15/76

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4691857/24 (22) 30.05.89 (46) 23.11.92. Бюл. N. 43 (71) Институт точной механики и вычислительной техники им. С.А.Лебедева (72) Б.А.Бабаян, В.Ю.Волконский, В.Я.Горштейн, А.К.Ким, Л,H.Íàçàðîâ, Ю.Х.Сахин и

С.В.Семенихин (56) Патент США NЬ 4240143, кл, G 06 F

15/16, 1980, Авторское свидетельство СССР

bh 692400, кл. G 06 F 15/16, 1977. (54) ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА (57) Изобретение относится к вычислительН0А технике и предназначено для использования в многопроцессорных вычислительных комплексах высокой производительности.

Цель изобретения — повышение производительности на скалярных и векторных вычислениях и сокращение времени выполнения управляющих воздействий. Система выполнена в виде следующих модулей устройства—

1-1-1-8 общей оперативной памяти, цент1777148

35 ральных процессоров 2-1-2-16 и процессоров 3-1-3-8 ввода-вывода, Узел центрального управления системой содержит блоки программного управления, выполненные в виде управляющих ЭВМ 5-1-5-8 и коммутатора 4 линий связи. Наличие связей между модулями системы типа каждый с каждым

Изобретение относится к вычислительной технике и может быть использовано при проектировании многопроцессорных вычислительных комплексов высокой производительности, Цель изобретения — повышение производительности на скалярных и векторных вычислениях и сокращение времени выполнения управляющих воздействий.

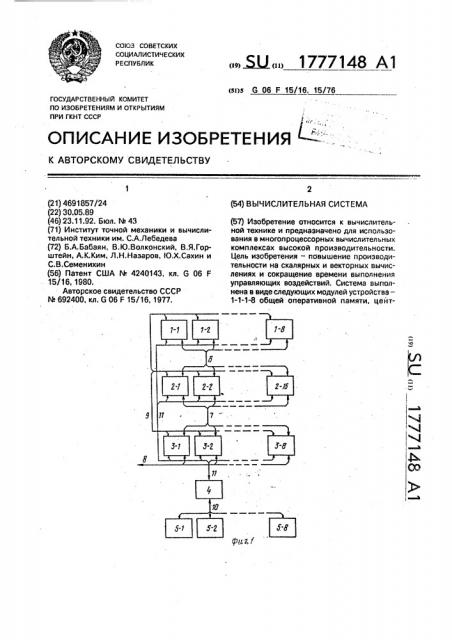

На фиг. 1 представлена структурная . схема вычислительной системы; на фиг. 2— структурная схема центрального процессора; на фиг. 3 — структура командного слова центрального процессора; на фиг. 4 — структурная схема устройства буферной памяти команд, устройства управления, устройства буферной памяти данных и блока управления устройством буферной памяти команд; на фиг, 5 — структурная схема коммутатора данных; нэ фиг. 6 — структурная схема блока индексации; на фиг. 7 — структурна схема блока перевода математического адреса в физический; на фиг. 8 — структурная схема блока подпрограмм; на фиг. 9 — структурная схема арифметика-логического устройства; на фиг. 10- структурная схема коммутатора линий связи узла центрального управления вычислительной системой; нэ фиг, 11— структурная схема устройства сопряжения; нэ фиг. 12 — структурная схема блока вызова-записи данных; на фиг. 13 — структурная схема алгоритма работы управляющей

ЭВМ, Вычислительная система (фиг. 1) выполнена в виде следующих модулей К=В устройств общей оперативной памяти 1-1 — 1-8, M = 16 центральных процессоров 2-1- 2-16, N - 8 процессоров ввода-вывода 3-1 — 3-8, коммутатор 4 линий связи, К = 8 блоков программного управления, выполненные в виде управляющих ЭВМ 5-1-5-8 например, типа ЕС-1845. Кроме того, система содержит адресную и числовую шину 6 для обмена информацией между центральными процессорами и устройствами 1 общей оперативной памяти, командную и числовую шину 7 для обмена информацией между всеми центральными процессорами 2 и пропозволяет достичь поставленной цели изобретения при высокой надежности и живучести системы за счет резервирования модулей. Наличие управляющих ЭВМ 5 позволяет иметь в системе режимы ручного и автоматического управления системой. 1 з.п. ф-лы, 13 ил, цессорами ввода-вывода 3,. каналы обмена

8 для обмена информацией между процессарами ввода-вывода 3, внешними запоминающими устройствами, устройствами ввода-вывода и процессорами передачи данных по линиям связи, управляющую шину 9 для передачи сигналов прерывания между центральными процессорами 2, процессорами ввода-вывода 3 и устройствами 1 общей оперативной памяти, шины 10 и 11 обмена через коммутатор 4 линий связи между всеми процессорами, устройствами 1 общей оперативной памяти и управляющими ЭВМ 5.

Центральный процессор (фиг. 2) содержит устройство 12 буферной памяти команд, устройство управления 13, устройство 14 буферной памяти данных, коммутатор 15 данных, арифметико-логическое устройство 16, блок 17 вызова-записи данных, блок 18 индексации, ассоциативное запоминающее устройство 19, блок 20 перевода математического адреса в физический, устройство 21 сопряжения, устройство 22 локальной one25 рэтивной памяти, коммутатор 23 ввода-вы. вода, блок 24 подпрограмм, блок 25 управления устройством буферной памяти команд, шины 26 — 1-26-4 выдачи данных в устройство 12 буферной памяти команд, устройство 14 буферной памяти данных, ассоциативное запоминающее устройство 19 и блок 24 подпрограмм, шину 27 выборки команд, шины 28-1 — 28-7 распакованной команды, шину 29 выборки данных, шины 30-1

-30-2 выдачи операндов из коммутатора 15 данных; шины 31-1 — 31-3 выдачи результа тов операций из коммутатора 15 данных, шины 32-1 — 32-2 результатов операций арифметико-логического устройства 16 и

40. блока 17 вызова-записи, шину 33 передачи данных из блока 17 вызова-записи в блок 18 индексации, шину 34 выдачи адресов и данных в ассоциативное запоминающее устройство 19 и блок 20 перевода математического адреса в физический, шину 35 выдачи адреса в ассоциативное запоминающее устройство 19 и блок 20 перевода математических адресов в физи1777148

10

30

55 ческие, шину 36 выда и данных в устройство 14 и блок 24 подпрограмм, шин . 37 выдачи адресов и данных в устройство сопряжения 21, шины 38-1 — 38-2 исходной установки, шины 39-1 — 39-3 выхода блока

24 подпрограмм, шину 40 управления выборкой из устройства 12 буферной памяти команд, шину 14 выдачи адресов команд в устройство сопряжения 21, шину 42 блокировки дешифрации команд по битам значимости.

В блок 25 управления устройством буферной памяти команд(фиг. 4) входят четыре регистра 43-46 номера команд, ассоциативныйй запоминающий узел 47, счетчик 48 номера команд, счетчик 49 индекса команд, четыре регистра 50-53 индекса команд.

В устройство управления 13 (фиг. 4) входят счетчик 54 дешифрации команд, четыре регистра 55-58 дешифрации команд, регистр 59 управления, сдвигатель 60 выборки команд, сдвигатель 61 распаковки команд, три сумматора 62-64 формирования полей распакованной команды, блок 65 буферной памяти распакованной команды.

В устройство 14 буферной памяти данных (фиг. 4) входят блок 66 памяти битов значимости, блок 67 буферной памяти стека, блок 68 буферной памяти считывания, блок 69 выходной буферной памяти.

В коммутатор 15 данных (фиг. 5) входят блок 70 памяти результатов, регистры 71 результатов, коммутатор 72 операндов, коммутатор 73 результатов.

В блок 18 индексации (фиг. 6) входят восемь идентичных узлов 18-1 — 18-8 индексации, каждый из которых содержит блок 74 буферной памяти команд, блок 75 буферной памяти описателей массивов, регистр 76 приращения базы, регистр 77 базы, сумматор 78 формирования текущего адреса, сумматор 79 формирования текущего индекса, сумматор.80 формирования адреса записи в блок буферной памяти считывания, сумматор

81 формирования нового значения базы, В блок 20 перевода математического адреса в физический (фиг. 7) входит восемь идентичных ассоциативных запоминающих узлов 82-1 — 82-8 и узел 83 таблицы страниц оперативной памяти.

В каждый ассоциативный запоминающий узел 82 входят блок 84 входной буферной памяти, сумматор 85 формирования адреса следующей страницы, блок 86 буферной памяти данных, блок 87 ассоциативной памяти соответствия математических и физических адресов, сумматор 88 формирования физического адреса слова. Узел 83 таблицы страниц оперативной памяти содержит регистр 89 базы страниц, сумматор

90 формирования адре"= строки;;гблиць., блок 91 памяти таблицы стоаниц.

В блок 24 подпрограмм (фиг. 8) входит дешифратор 92 команд, базовые регистры

93, дополнительные базовые регистры 94, блок 95 буферной памяти связующей информации, управляющие регистра 96, сумматор 97.

Арифметико-логическое устройство 16 (фиг. 9) содержит блоки 98 и 99 сложения, 100 и 101 умножения, 102 и 103 логических преобразований, блок 104 деления.

Коммутатор 4 линий связи (фиг. 10) содержит коммутатор 105 модулей системы, адаптер 106 управления и пульт l07 управления.

Устройство сопряжения 21 (фиг. 11) содержит коммутатор 108 запросов в память, коммутатор 109 приема данных из памяти, блок 110 адресов назначения и адаптер 111 управления и прерываний, блок 112 исходного состояния, В блок 17 вызова-записи данных (фиг.

12) входят блок 113 входных регистров, сумматор 114 формирования адреса обращения в память, сумматор 115 сравнения индекса и размера массива, блок 116 формирования записываемого числа, выходной регистр 117 адреса, выходной регистр 118 числа.

Управление вычислительной системой производится по алгоритму (фиг.13), Программа находится под управлением штатной операционной системы 119 управляющей ЭВМ 5 и включает в себя блок

120 команд оператора, блок 121 автоматического оператора, диспе1 чер 122, блок 123 управления системой, блок 124 телеметрии, блок 125 индикации, архив 126 индикации, блок 127 тестирования, архив 128 тестов. блок 129 регистрации, Цепи управляющих и тактирующих сигналов в описании не показаны.

Вычислительная система работает следующим образом.

Оператор с любой из управляющих

3BM5-1 — 5-8(фиг. 1) по шинам 10и 11 через коммутатор 4 линий связи выполняет исходную установку модулей системы и загрузку программы инициализации раскрутки операционной системы в устройстве 22 локальной оперативной памяти всех центральных процессоров 2-1 — 2-16, Центральный процессор, имеющий младший номер в системе (в случае максимальной конфигурации зто процессор 2-1), по шине 7 производит инициализацию процессора ввода-вывода 3-1, имеющего младший номер в системе, после чего последний по каналам обмена 8 пересылает операционную систему с внешнего

1777148

15

40

50 запоминающего устройства в общую оперативную память 1-1 — 1-8.

Путь передачи из процессора ввода-вывода 3-1 по шине 7 в коммутатор 23 вводавывода центрального процессора 2-1 и через устройство сопряжения 21 по шине 6 в устройства 1 оперативной памяти. После выполнения этой пересылки все центральные процессоры 3 загружают операционную систему по шине 6 из устройств 1 oG eA оперативной памяти в свои устройства 22— локальной оперативной памяти и инициализируют каналы обмена 8 во всех процессорах ввода-вывода 3.

В дальнейшем вычислительная система работает в автоматическом режиме пад управлением операционной системы, получая задания по каналам обмена 8. Синхронизация параллельной работы модулей системы реализуется посредством управляющей шины 9 путем передачи сигналов прерывания, Устройства 1 общей оперативной памяти используются для хранения больших массивов и общих данных параллельно исполняемых процессов на разных центральных процессорах 2. Программные коды и локальные области данных задач загружаются с внешней памяти по каналам 8 процессорами ввода-вывода 3 через шину 7, коммутатор 23 ввода-вывода и устройство сопряжения 21 в устройства 22 локальной оперативной памяти центральных процессоров 2.

Управляющая программа управляющих

ЭВМ 5-1 — 5-8 по шинам 10 и 11 через коммутатор 4 производит периодический сбор телеметрической информации о состоянии модулей вычислительной системы и сигнализирует оператору об аварийных ситуациях и итоговых результатов опроса. При наличии аварийных ситуаций выполняется автоматическая диагностика аварийного модуля, а также при необходимости, автоматическая повторная загрузка операционной системы с внешней памяти.

Программа управления вычислительной системой запускается как отдельная задача. Первым вызывается блок 126 команд оператора. Этот блок 120 выполняет интерпретацию команд оператора вычислительной системы в виде последовательности заданий для диспетчера 122. Кроме того, из блока 120 может быть вызван блок 121 автоматического оператора вычислительной системы, который обеспечивает управление в автоматическом режиме с заданными функциями управления.

Диспетчер 122 обеспечивает по заданиям из блоков 120 и 121 вызов блоков 123, 124, 125, архива 126, блока 127, а также взаимодействует с операционной системой.

118 управляющей ЭВМ при выполнении обменов па линии связи и с внешними устройствами управляющей ЭВМ (печать, накопители на магнитных дисках (НМД).

Блок 123 управления системой выполняет команды исходной установки модулей (сброс, установка начальных значений в регистры, переключения конфигурации), а также загрузку операционной системы в устройство 22 локальной оперативной памяти центрального процессора 2.

Блок 124 телеметрии выполняет в заданном объема сбор информации о состоянии модулей и режимах функционирования модулей вычислительной системы.

Блок 125 индикации выполняет отображение нэ алфавитно-цифровом дисплее управляющей ЭВМ состояния схем модулей вычислительной системы. Для этого из архиBB 124 индикации используется информация о способах допуска к требуемым схемам модулей и видах их отражения на экране дисплея.

Блок 127 тестирования обеспечивает загрузку в модули вычислительной системы набора тестов для контроля функционирования и диагностики неисправностей. Вызов тестов выполняется с помощью архива

126 тестов, который является справочником размещения тестов на НМД управляющей

3BM.

Блок l29 регистрации обеспечивает отображение на экране дисплея и вывод на печать аварийных состояний модулей вычислительной системы и результатов про верки их функционирования, Наличие в составе вычислительной системы однотипных модулей позволяет достичь высокого быстродействия путем организации их параллельной работы. За счет изменения количества модулей, можно строить комплексы различной производительности применительно к конкретным условиям. Важным следствием модульной организации является высокая структурная надежность вычислительной системы за счет резервирования однотипных модулей и структуры связей по типу каждый с каждым.

При наличии достаточного резерва вычислительная система является практически безотказной, а вычислительный процесс непрерывным, благодаря аппаратуре динамической реконфигурации, автоматически исключающей неисправный модуль иэ состава рабочей конфигурации и соответствующей поддержке операционной системы, позволяющей продолжать вычисления на изменяющемся составе рабочей конфигура1777148

10

30

40

50 ции за счет динамического управления ресурсами вычислительной системы.

Возможность создания полностью изолированных подсистем и модульная организация органов управления (несколько управляющих ЭВМ со средствами коммутации управляющих воздействий) позволяют проводить восстановительные и регламентные работы беэ нарушения работы основного вычислительного процесса.

Каждый центральный процессор 2-1—

2-16 работает следующим образом.

Исходная установка процессора поступает по шине 11 через устройство сопряжения 21 ° Она включает в себя загрузку программы операционной системы устройство 22 оперативной памяти и установку по шинам 38-1 — 38-2 регистров блоков подпрограмм 24 и управления устройством буферной памяти команд 25.

Блок 25 выполняет подкачку программного кода из устройства 22. С этой целью он выдает запросы по шине 41 через устройство сопряжения 21 в устройство 22, Программный код из.устрайства 22 через устройство сопряжения 21 по шине 26-1 поступает в устройство 12 буферной памяти команд.

Блок 25 управления па шине 40 управляет выборкой программного кода из устройства

12. По шине 27 он поступает в устройство управления 13, Устройства управления 13 по шине 28-2 выдает команду в арифметика-логическое устройство 16 па шине 28-3 в блок 17 вызова — записи данных, по шине 28-4 в блок 18 индексации по шине 28-5 в блок 24 подпрограмм и по шине 28-6 в блок 25 управления по шине 28-1 читает операнды из устройства

14 буферной памяти данных, по шине 28-7 управляет работой коммутатора 15 данных, обеспечивая передачуданных па шине 29 из устройства 14 и па шине 32-1 результатов операций арифметика-логического устройства 16 и блок 17 данных вызова-записи.

Данные поступают на информационные входы операндов арифметика-логического устройства 16 и блока 17 по шинам 30-1 и

30-2, соответственно. Па шине 31-2 указанные данные поступают в устройство 14 буферной памяти данных и по шине 31 3 в блок 24 подпрограмм. Данные, необходимые для работы блока 18 индексации, передаются через блок 17 вызова-записи данных по шине 33.

Основное назначение блока 17 — скалярные обращения в устройство 1 оперативной памяти по чтению и записи, В случае чтения данных в устройство 14, блок 17 по шине 34 выдает адреса в ассоциативное запоминающее устройства 9 и б.",а;: "O,,ерсвода математического appGcG в физический.

При удачном поиске в устройстве 19 данные по шине 36 передаются в устройство 14. s противном случае преобразованный физический адрес из блока 20 по шине 37 поступает в устройство сопряжения 21 и далее в устройство 22 локальной оперативной памяти или по шине 6 в устройства общей оперативной памяти 1-1 — 1-8. Данные из устройства 22 или устройств 1-1 — i-8 через устройство сопряжения 21 по шине

26-2 заносятся в устройство 14 буферной память данных и по шине 26-3 в ассациативное запоминающее устройство 19, чтобы сакратить время доступа к ним при повторных обращениях.

При выполнении записи в память, в блок 17 по шине 30-2 поступает адрес записи и по шине 31-1 — записываемое число, Далее адрес и число по шине 34 выдаются в устройство 19 и блок 20. Запись в устройства 1 и 22 выполняется беэусловно, а в устройство 19 только при наличии ячейки с указанным адресом записи, Блок 18 индексации является генератором адресов элементов массивов, Перед циклическим участком программы в блок 18 через блок 17 вызова-записи данных па цзине 33 загружаются дескрипторы массивов, к которым будут выполняться обращения в циклической программе и программе формирования адресов элементов массивов (шаг изменения адреса для каждого испальзуемого массива). В цикпическам участке программы, по команде поступающей па шине 28-4 из устройства управления 13, блок 18 индексации по шине 35 выдает требуемые адреса элементов массивов в устройство 19 и блок 20 аналогично описанному выше для блока 18 вызова записи данных. . В центральном процессоре 2 используется архитектура длинного командного слова (см. фиг. 3) и управление работой устройств на основе статического планирования на этапе трансляции программы. Команда в процессоре 2 имеет переменную длину и может достигать 36 байтов. В команде максимальной длины может садержаться семь арифметика-логических операций (два сложения, два умножения, две логические операции и одна деление), операция для блока 18 индексации и операция передачи управления. Адресные и управляющие поля команды обеспечивают выборку восьми операндов из устройства

14, передачу их и семи результатов предшествующих операций в арифметика-лагиче1777148

12 ское устройство 16, запись четырех результатов операций в устройство 14.

Устройство управления 13 каждый такт может выдавать по шине 28-2 распакованную команду максимального размера и обеспечивать тем самым полную загрузку параллельного полностью сегментированного арифметико-логического устройства

16.

Большинство блоков в процессоре 2 и связи между ними имеют параллельную орГанизацию.

Так устройство сопряжения 21 обеспечивает в каждом такте чтение до восьми слов данных и команд и запись двух слов данных устройства 1 или 22.

Устройство 12 буферной памяти команд выполнено по двухпортовой схеме и обеспечивает в каждом такте запись восьми и чтение шестнадцати слов программного кода.

Устройство 14 буферной памяти данных выполнено по 16-ти портовой схеме и обеспечивает в каждом такте чтение и запись восьми слов данных.

Коммутатор 15 данных обеспечивает передачу пятнадцати операндов по шине

30-1 в арифметико-логическое устройство

16 и по шине 30-2 в блок 17 вызова-записи данных и четырех результатов операций в устройство 14 по шине 31-2.

Устройство 16 и блок 17 вызова-записи каждый такт выдают семь результатов операций в коммутатор 15данных по шине 32-1.

Блок 18 индексации каждый такт по шине 35 формирует восемь, а блок 17 вызовазаписи по шине 34 два адреса обращения в оперативную память.

Ассоциативное запоминающее устройство 19 каждый такт обрабатывает два, а блок 20 перевода математического адреса в физический восемь обращений в память.

Блок 25 управления каждый такт выдает обращения за восьмью командными словами и обеспечивает передачу управления по одному из четырех направлений ветвления без перерывов в дешифрации команд.

Блок 24 подпрограмм выполняет подготовку адресного контекста трех процедурных переходов и процедурное переключение (смену контакта и вызов программного кода) беэ приостановки дешифрации команд.

Таким образом, структура центрального процессора 2 эа счет существенно параллельной органиэации ориентирована-на векторные вычисления. Вместе с тем архитектура широкого командного слова дает возможность испольэовать параллельную структуру процессора для организации рас5 в последующие операции (уменьшение влияния зависимости по данным), ветвление по

30

50 параллеливания скалярных вычислений.

Этому способствует наличие коммутатора

15 данных, который обеспечивает быструю передачу результатов в качестве операндов одному из 4-х направлений и условное выполнение нескольких параллельных ветвей программы (уменьшение влияния зависимости по управлению), быстрый процедурный переход без приостановки дешифрации, Передача управления осуществляется в два этапа. На первом этапе по команде подготовки перехода происходит запоминание индексом перехода одного из регистров 4346 номера команд, поиск по заданному индексу в ассоциативном запоминающем узле

47 и, выдача в соответствующий регистр 5053 индекса команды адреса перехода по устройству 12 буферной памяти команд.

В случае неуспешного поиска счетчик

48 номера команды выдает в устройство 21 сопряжения по шине 41 серию запросов на всю страницу программного кода, после чего из устройства локальной оперативной памяти 22 программный код через устройство сопряжения 21 по шине 26-1 поступает в устройство 12 буферной памяти команд.

Адреса чтения команд по шине 40 поступают в устройство 12 и обеспечивают выборку в течение одного такта 16-и командных слов на соответствующий регистр 55-58 дешифрации команды устройства управления 13. Кроме того, адрес поступает в счетчик 49 индекса команды для формирования последующих адресов программного кода.

Блок 25 управления устройство буферной памяти команд может принять три команды подготовки перехода, что обеспечивает на втором этапе по команде передачи управления ветвление программы по одному из 4-х направлений (одно "на провал" и три "на переход"), без приостановки дешифрации, так коды всех 4-х направлений имеются на регистрах 55-58 дешифрации команд. Ветвление выполняется с помощью регистра 59 управления, в который по шине 32-2 загружаются условные признаки передачи управления, вычис. ленные по командам отношений в арифметика-логическом устройстве 16.

Программный код хранится в устройстве 12 буферной памяти команд в упакованном виде. Это значит, что в любой широкой команде произвольная часть фрагментов может отсутствовать и значимые фрагменты размещаются без пропусков. Информация о

1777148

20

30

55 составе значимых фр.-"гмантав задается полем шкалы широкой команды (фиг. 3) и используется с двигателями 60 и 61 выборки и распаковки устройства управления 13 при формирования исполнительного распакованного представления команды.

В формировании исполнительного вида команды участвует счетчик 54 дешифрации команд, Он хранит номертакта дешифрации команды, присвоенный команде при составлении расписания выполнения команд на этапе трансляции. Этот номер является базовым адресом при формировании на сумматоре 62 номеров тактов выдачи результатов операций, содержащихся в команде и на сумматоре 63 адресов результатов предшествующих операций, :ðàíÿùèõñÿ в блоке 70 памяти результатов и используемых при выполнении операций текущей широкой команды. На сумматоре бч формируются адреса считывания по блокам 67 и 68 буферной памяти стека и считывания; Для этого по шине 39-2 иэ блока 24 подпрограмм на сумматор 64 передаются базовые адреса по указанным блокам буферной памяти 67 и 68.

Распакованная команда поступает в блок 65 буферной памяти распакованной команды и далее по шине 28-1 в устройство 14 буферной памяти данных (чтение операндов), в коммутатор 15 данных (выборка результатов, коммутация операндов и результатов), в устройство 16 и блоки

17,18,24,25 (коды операций и короткие константы из программного кода). Необходимость блока 65 вызвана воэможностью нарушения синхронного расписания выполнения команд иэ-за переменного времени выполнения операций чтения данных из оперативной памяти в устройство 14 буферной памяти данных.

В некоторых случаях на этапе трансляции не представляется возможным определить место переменной в иерархическим организованной оперативной памяти (ассоциативное запоминающее устройство 19, устройства 22 и 1-1 — 1-К). В других случаях место нахождения переменной во времени может меняться согласно вычисляемым условиям.

Указанные случаи приводят к тому, что при попытке чтения операндов иэ устройства 14 буферной памяти данных может оказаться, что данные е це не поступили. Это приводит к блокировке очередной широкой команды в блоке 65 и остановке конвейера на ступенях ниже блока 65. Блокировка выдается по шине 42 как результат просверки наличия операндов в блоке бб памяти битов значимости.

При поступлении данных блокировка снимается, операнды выбираются из блоков

67 или 68 и через блок 69 по шине 29 поступают в коммутатор 15 данных.

Наличие в устройстве 14 буферной памяти данных двух блоков 67 и 68 буферной памяти стека считывания вызвано необходимостью обеспечить высокую эффективность в условиях смешанных скалярно-векторных вычислениях, При работе с массивами данных устройство 14 является промежуточным буфером между оперативной памятью и арифметика-логическим устройством 16, куда данные поступают, как правило, для однократного использования. При выполнении скалярных вычислений рабочая совокупность переменных (стек) многократно используется. Совмещение блоков 67, 68 в одном блоке резко ухудшает эффективность буферной памяти на скалярных вычислениях вследствие вытеснения скалярных переменных, вызываемых элементами массивов.

Коммутатор 15 данных содержит неэависимоуправляемые коммутатор 72 операндов и коммутатор 73 результатов, Необходимость двух коммутаторов обьвсняется тем, что в начале выполнения широкой команды стоит задача распределения операндов по исполнительным устройствам арифметико-логического устройства 16, а затем, по мере выполнения операций — коммутация семи возможных результатов в 4-х каналах записи в устройство 14 буферной памяти данных. Управление коммутатором

73 результатов осуществляется посредством хранящегося в блоке 65 буферной памяти распакованной команды фрагмента кода, определяющего коммутацию и адреса записи устройства 14 буферной памяти данных.

Это позволяет выполнять процедурные переключения с совмещением начала выполнения команд новой процедуры и окончания выполнения команд покидаемой процедуры, т.к. адреса записи в устройство

14 формируются в устройстве управления

13 в момент дешифрации очередной широкой команды.

Блок 70 памяти результатов позволяет решать задачу коммутации результатов выполненных операций не только в момент окончания каждой операции, но и в течение некоторого интервала времени, что облегчает составление расписания выполнения программы на этапе трансляции. Задержка в использовании результатов задается спе1777148

10

20

40 циальным полем результата широкой команды (фиг. 3).

Регистр 71 результатов служит для ускорения передачи параметров из запускающей процедуры в запускаемую.

Общепринятый способ передачи параметров — запись в заданную ячейку устройства

14. В тех случаях, когда передаваемые параметры являются последними вычисляемыми результатами запускающей процедуры, а запускаемая процедура использует последние передаваемые параметры в самых первых командах, может произойти приостановка дешифрации по причине временного отсутствия параметров. Введение регистров результатов на несколько тактов сокращает доставку параметров в запускаемую процедуру.

При работе с массивами данных значительное место в программном коде занимает вычисление адресов элементов массивов, Вместе с тем, как правило, для некоторой векторной формулы закон вычислений адресов элементов массива остается постоянным. Это свойство использовано при организации блока 18 индексации, Для создания высокого темпа генерации адресов блок 18 индексации содержит восемь параллельно работающих узлов 18-3 — 18-8, в каждом из которых имеется блок 75 буферной памяти описателей массивов и блок 74 буферной памяти операций, содержимое которых заносится вне циклического участка программы по шине 33 иэ блока 17 вызовазаписи данных. Фактически блок 74 содержит программу доступа к элементам массивов, описатели которых хранятся в блоке 75.

При исполнении циклического участка программы устройство управления 13 по шине 28-4 выдает в блоке 18 индексации номер команды по блоку 74. Далее все восемь узлов блока 18 индексации по заданному номеру выполняют команду вычисления адреса элемента массива. В зависимости от алгоритма содержимое блоков 74 и 75 в узлах 18-1 — 18-8 может совпадать или быть разным, В первом случае создается высокий темп обращения к одному массиву данных, во втором — выполняется параллельное обращение ко многим массивам данных.

Адрес элемента массива формируется на сумматоре 73 путем сложения базового адреса массива со значением текущего индекса по массиву. На сумматоре 79 формируется значение текущей переменной для следующего обращения в массив (изменяется на шаг продвижение по массиву) и заносится в блок 75 буферной памяти описателей массивов.

Сумматоры 80 и 81 служат для формирования адресов назначения по блоку 68 буферной памяти считывания. Для обеспечения доступа в блок 68 используется метод передвигаемых баэ, когда в циклической программе адрес загружаемой ячейки остается постоянным, а базовый адрес для данного узла обращения может изменяться в каждом цикле на шаг приращения базы.

С этой целью в каждом узле блока 18 индексации имеются регистры 77 и 76 базы и приращение базы. На сумматоре 80 формируется текущий адрес назначения по блоку 68, а на сумматоре 81 — модифицируется текущее значение базы на шаг приращения.

Новое значение базы заносится в регистр базы 77, а сформированные математический адрес элемента массива и адрес назначения по шине 35 из всех узлов выдаются в ассоциативное запоминающее устройство

19 и блок 20 перевода математического адреса в физический.

Для поддержания высокого темпа обращений в оперативную память блок 20 перевода математического адреса в физический содержит восемь узлов 82-1 — 82-8, каждый иэ которых с помощью блока 87 ассоциативной памяти соответствия математических и физических адресов обеспечивает требуе-. мое преобразование.

Заполнение блока 87 имеет превентивный характер. С этой целью блок 87 выполнен по двухпортовой схеме, и параллельно с поиском строки соответствия по заданному адресу выполняется поиск следующей

Строки следующей математической страницы, Для скалярных обращений — это станица с увеличенным на единицу текущим математическим адресом, а для векторных обращений — увеличенный на шаг продвижения по массиву, Формирование адреса следующей страницы выполняется сумматором 85.

При отсутствии требуемой строки в блоке 87 выдается запрос в узел 83 таблицы страниц оперативной памяти. Блок 1 памяти таблицы страниц содержит полную таблицу соответствия математической и физической оперативной памяти.

На сумматоре 90 формируется адрес требуемой строки таблицы, и выполняется чтение из блока 91 памяти таблицы страниц, При организации таблицы страниц используются методы уплотнения (типа Н-кодирования), в связи с чем возможно вторичное обращение с выхода блока 91 на собственный вход.

1777148

Выбранная строка соответствия заносится в блок 87 ассоциативной памяти заданного узла 82. Таким образом, на фоне обращений в текущую математическую страницу выполняется подкачка строки соответствия.для следующей математической страницы.

Блок 84 входной буферной памяти служит для хранения запросов в случае выполнения поиска в узле 83 таблицы страниц оперативной памяти для текущей математической страницы. После ее вызова запросы в блок 87 ассоциативной памяти повторяются.

Сумматор 8& служит для формирования физического адреса слова (складываются физический адрес текущей страницы и адрес слова внутри страницы).

Блок 86 буферной памяти данных служит для хранения записываемых в оперативную память данных на время преобразования математического адреса записи в физический.

По шине 37 физические адреса и данные (в случае записи) выдаются в устройство сопряжения 21.

Заполнение блока 91 памяти таблицы страниц и регистра 89 базы страниц производится по шине 34 иэ блока 17 вызова-записи.

Блок 24 подпрограмм выполняет подготовку и переключение контекста при процедурных переходах, При этом базовые регистры 93 определяют контекст текущей процедуры, дополнительные базовые регистры 94 служат для создания контекста вызываемых процедур, блок 95 буферной памяти связующей информации для хранения динамической истории обращений к незавершенным процедурам, а управляющие регистры 96, содержат общесистемные регистры (таймер, часы, регистры конфигурации и т.д.).

Процедурные переключения как и внутрипроцедурные передачи управления, выполняются в две фазы. На фазе подготовки происходит копирование контекста иэ основных базовых регистров 93 в дополни: «тельные базовые регистры 94,"упрятывание" в блок 95 связующей информации регистров контекста, подлежащих коррекции при процедурном переключении, выход из оперативной памяти или формирование контекста вызываемой процедуры в дополнительных базовых регистрах 94, передача дескриптора программного сегмента в блок

25 управления для подкачки кода вызываемой процедуры в устройство 12 буферной памяти команд и устройство управления 13.

На фазе переключения происходит передача подготовленного контекста в базовые регистры 93 и переключение на дешифрацию программы вызванной процедуры в устройстве управления 13 и блоке 25 управления. Возврат в процедуру выполняется аналогичным образом за исключением того, что коррекция контекста выполняется из блоке 95 буферной памяти связующей

10 информации.

Принципиальным моментом в организации блока 24 подпрограмм является его асинхронная работа по подготовке процедурного переключения на фоне исполнения

15 участка программы, предшествующего процедурному переключению. Это вызвано тем, что программная реализация процедурного переключения требует ощутимого размера программного кода и будет вызывать остановку "конвейера" иэ-эа ожиданий поступлений элементов связующей информации из устройств общей оперативной памяти 1-1 — 1-8.

Использование управляющих 5-1 — 5-8

ЭВМ в качестве средства управления и ото20

25 бражения состояния вычислительной системы предоставляет воэможность в дополнение к ручному иметь режимы автоматического управления и сигнализации вычислительной системы на независимые подсистемы требует наличия нескольких управляющих ЭВМ 5-1 — 5-8 ЭВМ и средств коммутации их с модулями вычислительной системы.

Коммутатор линий связи 4 обеспечивает подключение восьми управляющих ЭВМ 5 типа ЕС 1845 ко всем модулям вычислительной системы.

Адаптер 106 управления по командам с

ЭВМ 5 подключает шину линии связи 10

ЭВМ 5 к шине линии связи 11 заданного модуля вычислительной си