Устройство для определения заданной ординаты корреляционной функции

Иллюстрации

Показать всеРеферат

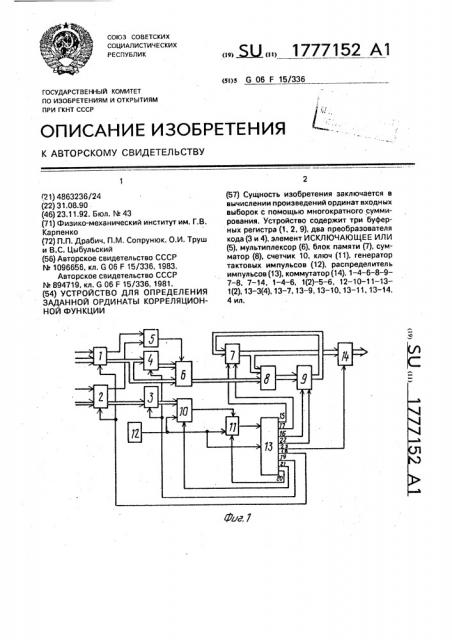

Сущность изобретения заключается в вычислении произведений ординат входных выборок с помощью многократного суммирования . Устройство срдержит три буферных регистра (1, 2, 9), два преобразователя кода(3 и 4), элемент ИСКЛЮЧАЮЩЕЕ ИЛИ

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (sl)s G 06 F 15/336

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4863236/24 (22) 31.08.90 (46) 23.11.92. Бюл. ЬЬ 43 (71) Физико-механический институт им. Г.В.

Карпенко (72) П.П. Драбич, П,М. Сопрунюк, О.И. Труш и В.С. Цыбульский (56) Авторское свидетельство СССР

М 1096656, кл. G 06 F 15/336, 1983.

Авторское свидетельство СССР

М 894719, кл. G 06 F 15/336, 1981. (54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ

ЗАДАННОЙ ОРДИНАТЫ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ Ы 1777152 А1 (57) Сущность изобретения заключается в вычислении произведений ординат входных выборок с помощью многократного суммирования. Устройство содержит три буферных регистра (1, 2, 9), два преобразователя кода(3 и 4), элемент ИСКЛЮЧАЮЩЕЕ ИЛИ (5), мультиплексор (6), блок памяти (7), сумматор (8), счетчик 10, ключ (11), генератор тактовых импульсов (12), распределитель импульсов (1 3), коммутатор (14). 1-4 — 6 — 8-9—

7 — 8, 7-14, 1-4-6, 1(2) — 5-6, 12 — 10-11-131(2), 13-3(4), 13-7, 13 — 9, 13-10, 13 — 11, 13-14, 4 ил.

1777152

Изобретение относится к вычислительной технике и может быть использовано для корреляционного анализа непрерывных случай и ых процессов.

Целью изобретения является упрощение устройства и снижение аппаратурных за рат.

Заявляемое устройство осуществляет определение ординат корреляционной функции в соответствии с алгоритмом

=f(y(k+m) Ьt)) где Кху(а At) — вэаимокорреляционная функция процессов у(т), y(t);

N — число отсчетов;

К=1,2... N; ! — максимальная задержка; т1,2 ...L.

На фиг. 1 представлена блок-схема заявляемого устройства; на фиг. 2 — один из возможных вариантов построения распределителя импульсов; на фиг. 3 приведена временная диаграмма работы коррелятора

flpN II=4, !Mage=8; на фиг. 4 паказач пример работы счетчика при !!=13, + =11. 4 с=-16.

Предлагаемый коррелятор содержит первый и второй буферные блохи 1 и 2, регистр старших разрядов 3, преобразова-. тель прямого када в дополнительный 4, схе му ИСКЛЮЧАЮЩЕЕ ИЛИ 5, мультиплексор

6, блок памяти 7, сумматор 8, третий буферный регистр 9, счетчик 10, ключ 11, генератор тактовых импульсов (ГТИ) 12, распределитель импульсов 13 и коммутатор

14. Информационные (знаковые и кодовые) входы первого и второго буферных регистров 1 и 2 являются входами коррелятора, кодовый выход первого буферного регистра соединен с первым информационным входом мультиплексора 6 и через преобразователь прямого кода в дополнительный 4 — с вторым информационным входом мультиплексора 6, выход которого соединен с первым входом сумматора 8, второй вход которого соединен с выходом блока памяти

7, а вь ход через третий буферный регистр 9 соединен с информационным входам блока памяти 7, знаковые выходы первого и второго буферных регистров 1 и 2 соединены с входами схемы ИСКЛЮЧА!ОЩЕЕ ИЛИ 5, выход которой соединен с управляющим входом мультиплексора 6. кодовый выход второго буферного регистра 2 соединен через регистр старших разрядов 3 с входом начальной установки счетчика 10, выход ко5 распределителя импульсов 13 и через ключ

30

50 тройства. Загрубление входного сигнала, а

20 торого соединен с первым управляющим входом кл1оча 1!, выход генератора тактовых импульсов 12 подключен к счетному входу счетчика 10, к входу синхронизации

11 — к входу задания рабочего интервала распределителя импульсов 13. Вход коммутатора 14 соединен с выходом блока памяти

7, а выход является выходом коррелятора в целом. Первый выход 15 распределителя импульсов 13 соединен с управляющим входам считывания блока памяти 7, второй выход 16 — с управляющим входом записи третьего буферного регистра 9, третий выход 17- с управляющим входом записи блока памяти 7, четвертый выход 18 — с управляющими входами первого и второго буферного регистров 1 и 2, пятый выход 19 — с управляющими входами регистра старших разрядов 3 и преобразователя прямого кода в дополнительный 4, шестой выход 20 — с вторым управлиощим входом ключа 11, седьмой выход 21 — с управляющим входом счетчика 10, восьмой выход 22 — с управляющим входом коммутатора 14 и девятый выход 23 — с входам обнуления третьего буферного регистра 9. у

Один из возможных вариантов построения распределителя импульсов 13 приведен на фиг, 2. Распределитель импульсов состоит из элементов задержки 24 — 29, схем

ИХ!И 30 и 31, делителя импульсов 32, счетчика цикла 33, выходных формирователей

34-42. Выходные формирователи преднаэначены для формирования управляющих сигналов с необходимыми параметрами.

Значение !! определяется уровнем сигнала y((k+m) A t) и находится в пределах

О

imgKc, при этом погрешность можно значительно уменьшить, если сигнал yf(k+m) At) будет кодирован нелинейно, а закон нелинейности поставить в зависимость от закона распределения значений входного сиt нала (43. При этом устройство несколько упростится за счет уменьшения числа разрядов, а также увеличится быстродействие yc- также преобразование линейного када сиг нала y((k+m) A t) в нелинейный выполняет регистр старших разрядов 3.

Заявленное устройство работает следующим образом.

Отсчеты вхадны;.". сигналов g (k Ь t) и

y((k+m) A t) поступают на информационные входы первого и второго буферных регистров 1 и 2, при этом код..соответствующий

1777152.".ов, ло входных oi:г;,а "or:, ooступает на кодов;4е вхог,ы, а информацу.; о з,аке входных сигналов поступает на знаковые входы буферных регистров 1 и 2, Импульсы ГТИ 12, поступающие на вход синхронизации распределителя импульсов

13, делятся в распределителе импульсов 13 в I

cL;rHàëà в регистре старших разрядов 3 значение сигнала y((k+m) Л tj записывается в счетчик 10. Командой н а зап и сь я вляется выходной сигнал с седьмого выхода 21 распределителя импульсов 13, задержанный по отношению к сигналу с четвертого выхода

18 на время Г4 > тз . Одновременно с сигналом с седьмого выхода 21 сигнал с шестого выхода 20 распределителя импульсов 13 поступает на BTорой управляющий вход ключа 11 и открывает его, после чего импульсы ГТИ 12 начинают поступать и на вход задания рабочего интервала распределителя импульсов управления 13, Информация о знаках входных сигналов сс знаковых выходов первого и второго буферных регистров 1 и 2 поступает на схему ИСКЛЮЧАЮЩЕЕ ИЛИ 5, управляемую мультиплексором 6. В случае совпадения знаков входных сигналов через мультиплексор 6 на первые входы сумматора 8 поступает отсчет сигнала p (k Л1) в прямом коде, в случае несовпадения — в дополнительном.

Этот отсчет суммируется с содержимым блока памяти 7, поступающим на второй вход сумматора 8, Командой на считывание сигнала из блока памяти 7 является импульс, поступивший с выхода ГТИ 12 через открытый ключ 11 на вход задания рабочего интервала распределителя импульсов 13 и появившийся на его первом выходе 15. Далее сигнал с второго выхода 16 распределителя импульсов 13, задержанный на время

t1 по отношению к сигналу на первом выходе 15, поступает на управляющий вход записи третьего буферного регистра 9, и выходной сигнал сумматора 8 записывается в третий буферный регистр 9. После этого по сигналу с третьего выхода 17 рлсп ределителя импульсов 13, задержанному по отношесигналу на восьмой выходе 22, подает команду на обнуление третьего буферного регистра 9, после чего нулевые значения переписываются в блок памяти 7 по коман50 де с третьего выхода 17 распределителя импульсов 13, задержанной по отношению к выходному сигналу на девятом выходе 23 на время т6. Коррелятор готов к вычислению . очередного значения корреляционной функции.

Импульсы ГТИ 12, поступающие через ключ 11 на вход задания рабочего интервала распределителя импульсов 13, проходят нэ первый выход 15 через схему ИЛИ 30 и

40 ниlo к сигнал на первoM йыхо ;. 1 : нл го а-;л т 2, содержилго,! Третье буфер}-гого реrLIстра 9 переписывается в блок памяти 7 вместо прежнего значения.

Этот же импульс ГТИ 12 поступает на счетный вход счетчика 10 и уменьшает значение записанного туда кода на единицу.

При следующем импульсе ГТИ 12 операция суммирования повторяется. Когда содержимое счетчика 10 станет равным нулю. после

Ь сул.мирований отс«ета сигнала g(k Atj. выходной сигнал счетчика 10 закрывает ключ 11 и импульсы ГТИ 12 не проходят на вход задания рабочего интервала распределителя импульсов 13. Таким образом, каждый отсчет сигнала!)

y({k+m) A tj.

После каждых isaac импульсов ГТИ 12 цикл повторяется, т.е. происходит многократное суммирование очередного отсчета входного сигнала.

Сумматор 8 работает беэ внешней синхронизации, его выходные сигналы изменяются по мере изменения входных. Выборка выходных сигналов сумматора 8 в нужные моменты времени осуществляется синхронизацией последующих узлов. После N циклов многократного суммирования отсчетов сигнала g(k Л1)(где N определяет усреднение во времени) сигнал с восьмого выхода

22 распределителя импульсов 13 подает команду на включение коммутатора 14. Одновременно с первого выхода 15 поступает команда считывания из блока памяти 7. Полученное результирующее значение корреляционной функции поступает на выход коррелятора. Число N необходимо выбирать таким, чтобы операция деления полученного результата сводилась к считыванию старших разрядов.

Далее выходной сигнал на девятом выходе 23 распределителя импульсов 13, задержанный на время z s по отношению к

1777152 выходной формирователь 34, на второй выход 16 — через элемент задержки 24 с временем задержки г1 и выходной формирователь 35 и на третий выход 17— через элементы задержки 24 и 25 с временем задержки х1, г2 соответственно, схему ИЛИ 31 и выходной формирователь 36.

Импульсы ГТИ 12, поступающие на -вход синхронизации распределителя импульсов

13, поступают на делитель импульсов 32 с коэффициентом деления смаке. С выхода делителя импульсов 32 импульсы проходят на четвертый выход 18 через выходной формирователь 37, на пятый выход 19 — через элемент задержки 26 с временем задержки тз и выходной формирователь 38, на шестой выход 20 — через элементы задержки 27 с временем задержки t 4 и выходной формирователь 39, на седьмой выход 21— через элементы задержки 27 и выходной формирователь 40, а также на вход счетчика цикла 33 с коэффициентом пересчета N, С выхода счетчика цикла 33 импульсы проходят на восьмой выход 22 через выходной формирователь 41, на первый выход 15— через схему ИЛИ 30 и выходной формирователь 34, на девятый выход 23 — через элемент задержки 28 с временем задержки тэ и выходной формирователь 42 и на третий выход 17 — через элементы задержки 28 и 29 с временем задержки гg, r е соответственно, схему ИЛИ 31 и выходной формирователь 36.

Как следует из описания заявляемого устройства, оно проще прототипа и обеспечивает снижение аппаратурных затрат.

Формула изобретения

Устройство для определения заданной ординаты корреляционной функции, содержащее первый и второй буферные регистры, информационные входы которых являются входами устройства, блок памяти, выход которого соединен с первым входом сумматора, мультиплексор, счетчик, преобразователь прямого кода в дополнич а ю щ е е с я тем, что, с целью упрощения и снижения аппаратурных затрат, в

5 него введены генератор тактовых импульсов, регистр старших разрядов, ключ и эле10

35

40 обнуления счетчика, пятый и шестой выходы распределителя импульсов соединены с входами соответственно считывания и записи блока памяти, седьмой и восьмой выходы — с входами записи и обнуления третьего

20 тельный, третий буферный регистр, коммутатор и распределитель импульсов, о т л имент ИСКЛЮЧАЮЩЕЕ ИЛИ, при этом знаковые выходы первого и второго буферных регистров через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с управляющим входом мультиплексора, кодовый выход первого буферного регистра соединен с первым информационным входом мультиплексора и через преобразователь прямого кода в дополнительный — с вторым информационным входом мультиплексора, выход которого соединен с первым входом сумматора, выход которого через третий буферный регистр соединен с информационным входом блока памяти, выход которого соединен с вторым входом сумматора и через коммутатор — с выходом устройства, кодовый выход второго буферного регистра через регистр старших разрядов соединен с входом начальной установки счетчика, выход генератора тактовых импульсов соединен с вычитающим входом счетчика, с входом синхронизации распределителя импульсов и через ключ — с входом задания рабочего интервала распределителя импульсов, первый выход которого соединен с входами записи первого и второго буферных регистров, второй выход — с входами синхронизации преобразователя кода прямого в дополнительный и регистра старших разрядов, третий выход — с входом записи счетчика, четвертый выход — с первым управляющим входом ключа, второй управляющий вход которого соединен с выходом буферного регистра, а девятый выход — с управляющим входом коммутатора.

1777152

Фиг. 2

1777152 гтрк

Юыгаа игривая 2 >алигер Иу кне рггиглгггг

Лмугл &ал ,14

4maa Icvnmv гйотрыРан глюгагг

Суиюыгаииг

Snnna nn nmu

Bunts 8mpam ургрим7рггж

rr

Аыаз А&ач

nn nmu 2 лмай геиюииг га

Я люи

Фиг 4

Составитель П.Драбич

Редактор Г.Бельская Техред М,Моргентал Корректор А.Козориз

Заказ 4123 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж 35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101