Динамический триггер на транзисторах

Иллюстрации

Показать всеРеферат

ОПИСАН ЙЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 1

Союз Соеетскиа

Социалистических

Республик

I.

Зависимое от авт. свидетельства ¹

Заявлено 05Х!.1963 (№ 840439/26-24) с присоединением заявки ¹

Приоритет

Опубликовано 08.1.1966. Бюллетень № 2

Дата опубликования описания 16.II.1966

Комитет по делам иаобретений и открытий при Сосете Министров

СССР

621.374.3 (088.8)

681. 142. 66 (088.8) В. М. Головков и Г. П. Фролов

Авторы изобретения

Заявитель

ДИНАМИЧЕСКИЙ ТРИГГЕР НА ТРАНЗИСТОРАХ

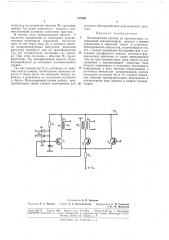

В состоянии, соответствующем «О», потенциал базы транзистора Т, задается потенциалом отсечки диода Да, подключенному к источнику — Е, напряжения через сопротивление Рс. Во время отсутствия синхронизирующих импульсов потенциал базы транзистора Т, устанавливается ниже такового транзистора Т,, поэтому весь ток, задаваемый источником + Е., напряжения и сопротивлением R, òå÷åò в коллекторную цепь транзистора Т;,. В соответствии с этим транзисторы

Т, и Т» закрыты. При поступлении положительного синхронизирующего импульса в базу транзистора Т,, последний закроется, и весь ток переключателя потечет в коллекторную цепь транзистора Тт Транзистор Т» будет закрыт, так как потенциал его эмнттера не станет выше нулевого уровня. Таким образом, с

30 каждым поступлением синхронизирующего

Известные динамические триггеры на транзисторах, содержащие запоминающую емкость с цепями управления и обратной связи и усилитель-формирователь импульсов, позволяют получить парафазный выход лишь объединением двух триггеров, что делает подобные устройства громоздкими и приводит к дополнительным задержкам выходных импульсов.

Предлагается триггер, в котором для повышения быстродействия и получения парафазного выхода усилитель-формирователь выполнен по схеме переключения тока на трех транзисторах, база одного из них соединена с запоминающей емкостью, база второго подключена к источнику постоянного напряжения, а база третьего подсоединена к источнику импульсов синхронизации, причем выходами состояний «О» и «1» служат вторичные обмотки трансформаторов, включенные в коллекторные цепи первого и второго транзисторов, На чертеже изображен описываемый триггер.

Он выполнен на переключателе тока, образованном транзисторами Т,, Т» и Т, и сопротивлением R, . Запоминающая емкость С, к которой подключены диоды Д, сброса, Д установки, Дз обратной связи и сопротивление

Ис смещения, соединена с базой транзистора

Т,. В коллекторную цепь этого транзистора включен трансформатор Тр1 с обмотками LV и % е, импульсы с выхода которого соответствук1т состоянию «О» триггера. База транзистора Т., в коллекторную цепь которого включен трансформатор Тр» д я снятия импульсов при состоянии триггера в положешш «1», присоединена к уровню постоянного напряжения (в данном случае — к нулевому уровню). База транзистора Т;; соединена с источником синхронизирующих импульсов.

177930

-Е

Составитель Б. П, Тимохин

Редактор Л. A. Ильина Тсхред А. А. Камышникова Корректоры: С. Н. Соколова и К. М. федулова лаказ 202 15 Тираж 1900 Формат бум. 60p,90 /ö Объем 0,16 изд. л. Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Типогра<рии, пр. Сапунова, д. 2 нмпуJIbcB Н3 вторич 1ой ool

В случае, если запоминающая емкость С окажется заряженной до некоторого положительного потенциала импульсом, поступающим на нее через диод Д, в моменты прихода синхронизирующих импульсов выходные импульсы возникнут уже на трансформаторе

Тра, что соответствует состоянию «1» триггера При этом сигналом с обмотки W. трансформатора Тра запоминающая емкость будет подзаряжаться до исходного положительного уровня.

Так как транзистор Т, в состоянии «1» триггера всегда закрыт, необходимое значение емкости С очень мало, что позволяет быстро заряжать и разряжать ее сигналами установки и сброса. Ненасыщенный режим работы всех транзисторов также создает возможность для высокого быстродействия динамического триггера.

Предмет изобретения

Динамический триггер на транзисторах, содержащий запоминающую емкость с цепями управления и обратной связи и усилительформирователь импульсов, отличающийся тем, что, с целью повышения быстродействия и получения парафазного выхода, усилитель-формирователь выполнен по схеме переключения тока на трех транзисторах, база одного из них соединена с запоминающей емкостью, база второго подключена к источнику постоянного напряжения, а база третьего подсоединена к источнику импульсов синхронизации, причем выходами состояний «О» и «1» служат вторичные обмотки трансформаторов, включенные в коллекторные цепи первого и второго транзи20 сторов.