Коммутатор

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и импульсной технике и может быть использовано в системах коммутации цифровых сигналов. Коммутатор содержит 12 элементов И восемь элементов ИЛИ. Все входы и выходы устройства выполнены парафазными. Коммутатор обеспечивает повышение достоверности передачи цифровой информации за счет того, что любая одиночная константная неисправность обязательно проявляется на его выходах и обнаруживается в момент ее первого проявления. 1 з. п. ф-лы, 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ /" (54) КОММУТАТОР ОО !

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4937761/21 (22) 26,04.91 (46) 07,12,92. Бюл. ¹ 45 (75) С. В. Шевцов и С. Д. Чуприн (56) 1. Титце У., Шенк К. Полупроводниковая схемотехника: Справочное руководство.—

М.: Мир, 1982, с. 327, рис. 19, 14.

2. Прагер Э., Шимек Б., Дмитриев В. П, Цифровая техника в связи. — M.: Радио и связь: Прага, SNTL, 1981, с. 177. рис. 7.22.

Изобретение относится к автоматике и импульсной технике и может быть использовано в системах коммутации цифровых сигналов повышенной надежности, Известен коммутатор, используемый в качестве мультиплексора цифровых сигналов, содержащий первый и второй элементы

И, выходы которых подключены к входам элемента ИЛИ, выход которого является выходом устройства. входами которого являются первые входы первого и второго элементов И, вторые входы которых подключены соответственно к входу и выходу инвертора, вход которого является управляющим входом устройства (1).

Недостатком известного устройства является низкая надежность.

Наиболее близким к предлагаемому является коммутатор, содержащий с первого по четвертый элементы И, а также первый и второй элементы ИЛИ, первые входы которых соединены соответственно с выходами первого и третьего элементов И, а вторые входы подключены соответственно к выходам второго и четвертого элементов И, пер,5U, „1780171 А1 (57) Изобретение относится к автоматике и импульсной технике и может быть использовано в системах коммутации цифровых сигналов. Коммутатор содержит 12 элементов

И восемь элементов ИЛИ, Все входы и выходы устройства выполнены парафазными.

Коммутатор обеспечивает повышение достоверности передачи цифровой информации за счет того, что любая одиночная константная неисп равность обязательно проявляется на его выходах и обнаруживается в момент ее первого проявления. 1 з. и, ф-лы, 1 ил, вые входы которых обьединены и подключены к первому входу, второй вход которого подключен к первым входам первого и третьего элементов И, вторые входы с первого по четвертый элементов И соединены с управляющими входами устройства (2), Недостатком прототипа также является низкая надежность. заключающаяся в том, что устройство не может проверять само себя на наличие неисправности, Цель изобретения — повышение надежности коммутатора за счет обеспечения его самопроверяемости.

Указанная цель достигается совокупностью всех существенных признаков, изложенных в формуле изобретения, обеспечивающих обнаружение любой одиночной константной неисправности устройства.

Существенными отличительными признаками заявленного технического решения. обусловливающими его соответствие критериям изобретения, являются наличие парафазных входов устройства, дополнительных элементов И и ИЛИ, а также связей указанных входов с элементами схемы.

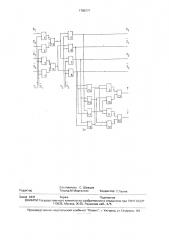

На чертеже представлена функциональная схема предлагаемого коммутатора.

Комму Гатор содержит с первого по двенадцатый элементы И 1 — 12, и с первого по восьмой элементы ИЛИ 13-20.

Первые входы первого 1 и второго 2 элементов И подключены соответствен!!о к первому Х1 и второму Х2 прял1ым и!!формационным входам, а вторые входы подкл(очены соответственно к прямому Ut u инверсному U1 первым управляющим входам, первые входы третьего 3 и четвертого

4 элементов И соединены соответственно с первым У! и BTopbtM Х2 инверсными н!!формационными входами устройства, а вторые входы подключены соответственно к прямому U1 и инверсному О1 первым управляющим входам, выход первого элемента ИЛ И

13 соединен с первыми входами пятогс 5 и седьмого 7 элементов И, выходы которых соединены соответственно с первым Zt u вторым Zz прямыми информацион!!Ыми Bbl- ходами устройства, первый Z1 и второй Zz инверснble информационные выходы которого соединены соответственно с выходал1и шестого 6 и восьмого 8 элементов И, первые входы которых объединены и подключе Ibl к выходу второго элемента ИЛИ 14, вторые входы пятого 5 и шестого 6, а также седьмого 7 и восьмого 8 элементов И пог!Врио Обьединены и подключены соответстве!!но .:: прямому Uz и инверсному U2 вторым управля!Огцим входам, первые входы первого 13 и второгс1 14 элементов ИЛИ соединены соответственно с выходами первого i и третbего

3 элементоэ И, а BT opûc Входы подкл ючеtl û к ВыхОДам ВтороГО 2 и !етвертого 4 зле!16нтов И, первый и второй входы третьего элемента ИЛИ 15 подключены соответственно к инверсным первому и второму информационным выходам устройства, первый tt

ВторОй прямые и!!форма!4ионнл!6 выходы которсГО соединены соотнетствен!!О с псрвым и вторым входами четвертого элема!Гга

ИЛИ 16, первый и второй входы пятого элемента ИЛИ 17 подключены соответственно к прямому первому и инверсному второму информационным выходам устройства, прямой второй и инверсный первый информаЦИОННЫЕ ВЫХОДЫ КОТОРОГО СОЕДИ!!Е!!Ы соответствен IO с первым и вторым входами шестого элемента ИЛИ 18, выход третьего элемента ИЛИ 15 соединен с первыми входами девятого 9 и одиннадцатого 11 элементов И, Выход четвертого элемента ИЛИ

16 подключен к первым входам десятого 10 и двенадцатого 12 элеме1:.тов И, выход пятого элемента ИЛИ it7 соедине!! с вторыми

5 1 0 15

Г5 входами десятого 10 и одиннадцатого 11 элементов И, выход шестого элемента ИЛИ 18 подкл!Очен к вторым входам девятого 9 и двенадцатого 12 элементов И, выходы девятого 9 и десятого 10 элементов И подключены соответственно к первому и второму входам седьмого элемента ИЛИ 19, выход которого соединен с прямым F контрольным выходомустройства, инверсный F контрольный выход которого соединен с выходом восьмого элемента ИЛИ 20, первый и второй входы которого подключены соответственно к выходам одиннадцатого 11 и двенадцатого 12 элементов И.

Коммутатор работает следующим обраЗОМ, На инфсрмационнь|е входы Х1, Х! и Х2, Х2 поступают с двух направлений парафазные сигналы, которые необходимо передать !!а какую-либо одну пару выходов Z1, Z1 или

Zz, Zz, в зависимости от значений сигналов !!а управляющих входах U1, О! и Uz, Uz.

Парафазный сигнал. поступающий на управляющий вход U1, U1, выбирает данные, поступа!Ощие на информационные входы устройства, Управляющие входы Uz, Uz служат для того, чтобы можно было выбрать один из информационных выходов Z1,21 или

Z2, Zz, на которые необходимо направить

Выбранные входные данные. На невыбранt tbtx выходах присутствуют нулевые логические сигналы. Выходы F, Г служат для

I

01 или 10, что позволяет в дальнейшем в случас появления ошибки при передаче обнаружить ее. Если на входы коммутатора поступа!От значения (Х1, Х1; Х2, Х2; U1, 01;

Uz)=01100101, 011 01001, 10010110, 1001 1010, осуществляются полное его тестирование и обнаружение любой одиночной константной неисправности (ОКН). При об«наружении в устройстве ОКН на выходах F, Г самопроверяемой схемы встроенного контроля появляются значения 00 либо 11. При правильной работе устройства на выходах

F, F присутствуют значения 01 или 10. Для индикации неисправности может быть использован любой сигнальный элемент, например светодиод, подключаемый к выходу

1780171 элемента РАВНОЗНАЧНОСТЬ, входы которого соединены соответственно с прямым и инверсным контрольным выходом устройства.

Предлагаемый коммутатор по сравнению с прототипом обеспечивает повышение достоверности передачи цифровой информации за счет того, что любая одиночная константная неисправность обязательно проявляется на его выходах и обнаруживается в момент ее первого. проявления.

Формула изобретения

1. Коммутатор, содержащий с первого по четвертый элементы И, первый и второй элементы ИЛИ, первые входы которых соединены соответственно с выходами первого и третьего элементов И, а вторые входы подключены к выходам второго и четвертого элементов И, причем первые входы первого и второго элементов И подключены соответственно к первому и второму прямым информационным входам, а вторые входы подключены соответственно к прямому и инверсному первым управляющим входам, отличающийся тем, что, с целью повышения надежности коммутатора путем обеспечения его. самопроверяемости, все входы и выходы коммутатора выполнены парафазными, введены с пятого по восьмой элементы И, причем первые входы третьего и четвертого элементов И соединены соответственно с первым и вторым инверсными информационными выходами коммутатора, а вторые входы подключены соответственно к прямому и инверсному первым управляющим входам, выход первого элемента

ИЛИ соединен с первыми входами пятого и седьмого элементов И, выходы которых соединены соответственно с первым и вторым прямыми информационными выходами коммутатора, первый и второй инверсные информационные выходы которого соединены соответственно с выходами шестого и восьмого элементов И, первые входы которых объединены и подключены к выходу второго элемента ИЛИ, вторые входы пятого и шестого, а также седьмого и восьмого элементов И попарно объединены и подключены соответственно к прямому и ин5 версному вторым управляющим входам, 2, Коммутатор по и. 1, о т л и ч а ю щ и йс я тем, что, с целью обнаружения любой одиночной константной неисправности, он

10 содержит с третьего по восьмой элементы

ИЛИ и с девятого по двенадцатый элементы

И, причем первый и второй входы третьего элемента ИЛИ подключены соответственно к инверсным первому и второму информа15 ционным выходам коммутатора, первый и второй прямые информационные выходы которого соединены соответственно с первым и вторым входами четвертого элемента

ИЛИ, первый и второй входы пятого элемен20 та ИЛИ подключены соответственно к прямому первому и инверсному второму информационным выходам коммутатора, прямой второй и инверсный информационные выходы которого соединены соответст25 венно с первым и вторым входами шестого элемента ИЛИ, выход третьего элемента

ИЛИ соединен с первыми входами девятого и одиннадцатого элементов И, выход четвертого элемента ИЛИ подключен к первым

30 входам десятого и двенадцатого элементов

И, выход пятого элемента ИЛИ соединен с вторыми входами десятого и одиннадцатого элементов И, выход шестого элемента ИЛИ подключен к вторым входам девятого и две35 надцатого элементов И, выходы девятого и десятого элементов И подключены соответственно к первому и второму входам седьмого элемента ИЛИ, выход которого соединен с прямым контрольным выходом

40 коммутатора, инверсный контрольный выход которого соединен с выходом восьмого элемента ИЛИ, первый и второй входы которого подключены соответственно к выходам одиннадцатого и двенадцатого

45 элементов И.

1780171

Составитель С. Шевцов

Техред M,Mîðãåíòàë КоРРектоР Т,Палий

Редактор

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101

Заказ 4441 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5