Устройство фазовой автоподстройки частоты

Иллюстрации

Показать всеРеферат

Использование техника связи, устройства авторегулирования частоты и фазы сигнала Сущность изобретения: устройство фазовой автоподстройки частоты содержит цифровой фазовый детектор, усреднитель, первый и второй перемножители, первый и второй сумматоры, цифроаналоговый преобразователь , управляемый генератор, регистр , блок задержки на такт элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй коммутаторы, вычитатель и дополнительный регистр. В устройстве имеются три ветви управления, объединенные на втором сумматоре, что и позволяет повысить точность синхронизации. 1 ил

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)л Н 03 1 7/06

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4820876/09 (22) 03,05.90 (46) 15,12.92. Бюл. ¹ 46 (71) Центральный научно-исследовательский институт связи (72) Е.В.Зильберг (56) Oklno Т. and al. Clock Synchronization

System for Digital Neturhs, FuJttsu Techn.

Journ, 1985, v. 21, N 1, р. 76. (54) УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ (57) Использование: техника связи, устройства авторегулирования частоты и фазы сигИзобретение относится к технике связи и может быть использовано в устройствах эвторегулировэния частоты и фазы сигналов.

Целью изобретения является повышение точности синхронизации.

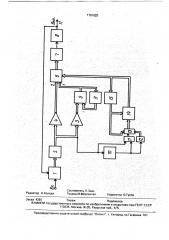

На чертеже представлена структурная электрическая схема устройства фазовой автоподстройки частоты.

Устройство фазовой автоподстройки ча-, стоты содержит цифровой фазовый детектор 1, усреднитель 2, первый и второй перемножители 3 и 4, первый и второй сумматоры 5 и 6, цифроаналоговый преобразователь 7, управляемый генератор 8, регистр

9, блок задержки 10 на такт, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй коммутаторы 12 и 13, вычитатель 14 и дополнительный регистр 15.

Устройстве: работает следующим образом. Цифровой фазовый дискриминатор 1 измеряет резкость фаз между сигналами. SU 1781820 Al нала. Сущность изобретения: устройство фаэовой автоподстройки частоты содержит цифровой фазовый детектор, усреднитель, первый и второй перемножители, первый и второй сумматоры, цифроаналоговый преобразователь, управляемый генератор, регистр, блок задержки на такт элемент

ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй. коммутаторы, вычитатель и дополнительный регистр. В устройстве имеются три ветви управления, объединенные на втором сумматоре, что и позволяет повысить точность синхронизации. 1 ил.

U8x и U8blx., а усреднитель 2 усредняет измеренную величину за время, равное периоду дискретизации. Затем усредненная величина разности фаз поступает на три параллельных ветви.. Первая ветвь, называемая

"пропорциональной", состоит иэ второго умножителя 4. Эта ветвь определяет фильтрующие свойства устройства фазовой автоподстройки частоты (УФАПЧ), причем эффективная фильтрация входных фазовых флуктуаций имеет место при значениях К1 существенно меньше единицы. Вторая ветвь, называемая "интегральной", состоит из первого умножителя 3, первого сумматора 5 и регистра 9, называемого "интегральным". Эта ветвь обеспечивает свойство астатизма и определяет время переходного процесса. УФАПЧ является устойчивым при

Kz «Къ Поэтому в тех случаях, когда усредненная разность фаз меньше величины, обратной Kz, то по существу свойство астатизма не проявляется без введения третьей ветви, и при наличии разности час1781820 тот установившаяся фазовая ошибка будет равна величине порядка 1/Кг.

" Алгоритм работы третьей ветви заключается в том, что при постоянстве знака усредненной разности фаз на каждом пери- 5 оде дискретизации содержимое вычитателя

: 14 по модулю увеличивается на единицу, а знак величины на выходах вычитателя 14 при этом такой, чтобы эта разность фаз компенсировалась после соответствующего уп- 10 равления частотой. При изменении знака усредненной разности фаз выход вычитате- ля 14 сбрасывается в нуль. Таким образом, третья параллельная ветвь представляет собой релейный накопительный регистр (до- 15 полнительный регистр 15), который сбрасывается, как только достигается цель накопления, т,е, разность фаз сводится к нулю. В связи с этим, третья ветвь анализирует только старший разряд кода усреднен- 20 ,ной разности фаз в блоке 10 содержится этот разряд. зафиксированный на предыду-— щем периоде дискретизации. Если на обоих входах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11 имеет место единица, т.е; фаза Us x, больше 25 фазы U ><., то на входы вычитаемого вычитателя 14 подается код единицы с первого информационного входа первого коммутатора 12, уменьшающая добавку от третьей ветви на выходе второго сумматора 6, Если 30 на обоих входах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11 имеет место нуль, то на входы вычитаемого вычитателя 14 коммутируется .код "-1" с второго информационного входа

: первого коммутатора 2, если сигналы на 35 входах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ . :различны, то HG входы вычитаемого вычитателя 14 коммутируется выход дополнительного регистра 15, вследствие чего выходы вычитателя 14 обнуляются. 40

Формула изобретения

Устройство фаэовой автоподстройки частоты, содержащее соединенные в кольцо цифровой фазовый детектор, усреднитель, первый перемножитель, первый сумматор, второй сумматор, цифроаналоговый преобразователь и управляемый генератор, а также второй перемножитель. включенный ,между выходом усреднителя и вторым входом второго сумматора, и регистр, включенный между выходом первого сумматора и его выходом, причем второй вход цифрового фазового детектора является входом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения точности синхронизации, в него введены соединенные последовательно блок задержки на такт и элемент

ИСКЛЮЧАЮЩЕЕ ИЛИ, соединенные последовательно вычитатель и дополнительный регистр, а также первый и второй коммутаторы, причем вход блока задержки на такт. второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и управляющий вход первого коммутатора соединены с выходом старшего разряда уСреднителя, первый информационный .вход первого коммутатора . является входом кода. "+1", его второй информационный вход — кодом "-1", а его выход соединей с первым информационным входом второго коммутатора, второй информационный вход второго коммутатора и. вход уменьшаемого вычитателя соединены с выходом дополнительного регистра, управляющий вход второго коммутатора соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход второго коммутатора подключен к входу вычитаемого вычитателя, выход которого соединен с третьим входом второго сумматора.

1781820

Корректор 0,Густи

Составитель Л.Закс

Техред М.Моргентал

Редактор Н.Коляда

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 4281 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 415