Устройство регистрации телеграфных посылок

Иллюстрации

Показать всеРеферат

Изобретение относится к технике передачи дискретных сообщений и предназначено для устранения искажений в передаваемых сигналах Целью изобретения является повышение достоверности правильной регистрации телеграфных посылок. С этой целью в устройство введены управляемый коммутатор, два реверсивных счетчика, четыре преобразователя сигналов посылок, интеграторы и решающий блок. Устройство обеспечивает выполнение поставленной цели за счет изменения зоны интегрирования по результатам регистрации предыдущих посылок. 3 ил.

союз советских

СОЦИАЛ И СТИЧ ЕСКИХ

РЕСПУБЛИК (я)5 H 04 1 1/22

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (21) 4912957/09 (22) 19.02.91 (46) 15.12.92. Бюл. N 46 (72) Ю.В.Кузьмин и В.Б.Киселев (56) Мартынов Е.Н, Синхронизация в системах передачи дискретных сообщений. — М.:

Связь, 1972, с. 13 — 14. (54) УСТРОЙСТВО РЕГИСТРАЦИИ ТЕЛЕГРАФНЫХ AOCblflOK (57) Изобретение относится к технике передачи дискретных сообщений и предназначеИзобретение относится к телеграфии.

Цель изобретения — повышение достоверности правильной регистрации посылок.

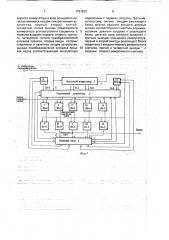

На фиг.1 изображена структурная электрическая схема предложенного устройства; на фиг.2 — схема управляемого коммутатора; на фиг,3 — схема решающего блока.

Устройство содержит кольцевой коммутатор 1, управляемый коммутатор 2, первый преобразователь 3 сигналов посылок, пер- вый интегратор 4, решающий блок 5, первый реверсивный счетчик 6, второй преобразователь 7 сигналов посылок, второй интегратор 8, третий преобразователь 9 сигналов посылок, третий интегратор 10, второй реверсивный счетчик 11, четвертый. преобразователь 12 сигналов посылок, четвертый интегратор 13, пятый преобразователь 14 сигналов посылок, шестой интегратор 15.

Управляемый коммутатор 2 содержит элемент И 16-29, элементы ИЛИ 30, 31, ре; гистры сдвига 32.33, элементы ИЛИ 34 — 37, (5U 1781833А1 но для устранения искажений в передаваемых.сигналах. Целью изобретения является повышение достоверности правильной регистрации телеграфных посылок, С этой целью в устройство введены управляемый коммутатор, два реверсивных счетчика, четыре преобразователя сигналов посылок, интеграторы и решающий блок. Устройство обеспечивает выполнение поставленной цели за счет изменения зоны интегрирования по результатам регистрации предыдущих посылок. 3 ил, триггер 38, блок совпадения 39, дешифраторы 40, 41.

Решающий блок 5 содержит блоки сравнения 42 — 45, инверторы 46, 47, счетчики 48—

51, линию задержки 52, делитель 53, ключи

54. 55, 56, 57, 58, 59, Устройство работает следующим образом, ° Ъ

Предлагаемое устройство является элементом аппаратуры передачи сообщений, в составе которой имеется и устройство тактоеой синхронизации, содержащее задающий генератор и схему автоподстройки ОО тактовой частоты по рабочему сигналу. Уст- (ф) ройство тактовой синхронизации формиру- (Д

1 ет последовательность тактовых импульсов с частотой Fo, соответствующей частоте следования посылок сигнала; принимаемых по и каналу связи, а также обеспечивает поддержание постоянного фазового взаиморасположения тактовых импульсов с частотой Fo., Производится форм и рова н ие последовательности синхроимпульсов иСИ", используемых для последующего стробирования

1781833 посылок сигнала, получаемых из канала связи с номинальной длительностью, Частота следования синхроимпульсов

"СИ" fp в и раз выше, чем Fp, и — число разрядов в кольцевом коммутаторе 1, т.е. на 5 длительность одной посылки сигнала приходится и синхроимпульсов. В пределах . длительности каждой посылки сигнала первый СИ соответствует переднему фронту (началу) посылки сигнала, получаемой по ка- 10 налу связи.

Максимальная длина основной зоны интегрйрования — n — 2m .импульсов, где m импульсов длина каждой из четырех вспомогательных зон. Длина основной зоны ин- 15 тегрирования меньше длины всей посылки на удвоенную величину вспомогательной зоны за счет внешних зон, расположенных у переднего и заднего фронтов телеграф-. ной посылки. . .., . 20

СИ, подаваемые на коммутаторы 1.2 используются для формирования "гребенок", предназначенных для последующего стробирования в преобразователях (блоки 3, 7, 9, 12; 14) посылок сигнала и преобразовате- 25 ля их в "пачки" импульсов. Конфйгурация

"гребенок", ойределяющих величины основ ной и вспомогательной, зон интегрирования, бпределяется коммутацией выходов кольцевого коммутатора 1 и входов преоб- 30 разователей (блоки 3,7,9,12,14), осуществляемой в управляемом коммутаторе 2 по сигналам реверсивных счетчиков 6,11.

При работе сигнал "1", соответствующий положению тактового импульса, с час- 35 татой Fp записывается в первую ячейку кольцевого коммутатора 1 и под воздействием подаваемых на него синхроимпульсов с частотой fp продвигается вдоль коммутатора. Так как выходы первых 1 — /n/2-2т+1/ 40 ячеек коммутатора 1 подключены через элементы И 16 — 22 и элемент ИЛИ 30 к первому . входу регистра 32, то с коммутатора 1 на реверсивный счетчик 13 сигнал придет через элемент И из числа эл. 16 — 22, который 45 вторым входом подключен к тому выходу дешифратор 40, наличие "1", на котором соответствует состоянию счетчика 6 в данный, момент. В результате в первую ячейку регистра 32 записывается "1", определяющая 50 начало внешней вспомогательной зоны у переднего фронта основной эоны. Под действием поступающих на второй вход регистра 32 синхроимпульсов эта "1" сдвигается вдоль регистра 32 от 1-й до 2m -ой ячейки. 55

Получаемые при этом на выходе регистра 32 синхроимпульсы поступают: с "1" ячеек на элемент ИЛИ (34), с (m+1)-2m ячеек на элемент ИЛИ (35), с m+1 выхода на вход триггера 36.!

4 (1

Импульс с m+1 выхода регистра 32 соответствует переднему фронту основной зоны интегрирования . "Пачки" синхроимпульсов с частотой fp, располагающиеся соответственно слева и справа от него и получаемые на выходе элементов ИЛИ 34, 35 образуют "гребенки" соответственно внешней и внутренней вспомогательных зон интегрирования. Через 2 и 3 выходы коммутатора 2 эти сигналы подаются собт-! ветственно на первые выходы преобразова-! телей 7, 9 для стробирования частей посылки, располагающихся около передйего фронта основной зоны.

При дальнейшем продвижении 1 по коммутатору 1 сигналы синхроимпульсов будут с выходов п/2+1 — п-2в+1 последовательно поступать на первые входы элементов И 23-29. Через подключенный к ним элемент ИЛИ 31 на первый вход регистра 33 придет сигнал "1" через элемент И из числа

1 элементов 23-29, который вторым входом подключена к тому выходу дешифратора 41, наличие "1" на котором соответствует состо-янию счетчика 11 в данный момент. В результате в первую ячейку регистра 33 будет . записана "1", определяющая начало внутренней вспомогательной зоны у заднвго фронта, основной зоны. Под действием поступающих на второй вход регистра 33 синхроимпульсов с частотой fp эта,1" сдвигается вдоль регистра 3, Получаемые . при этом СИ поступают с 1 — m ячеек на элемент ИЛИ 36, с (m+1) — 2m ячеек регистра

ЗЗ на элемент ИЛИ 37; с m -ro выхода на вход 2 триггера 38.

Импульс с m -го выхода регистра 33 соответствует заднему фронту основной 30ны интегрирования. "Пачки" синхроимпульсов, располагающиеся слева и справа от него и получаемые на выходах элементов

ИЛИ 36, 37, образуют "гребенки" соответственно для внутренней и внешней вспомогательных зон интегрирования. Через 4 и 5 выходы коммутатора 2 эти сигналы подаются на первые входы преобразователей 12, 14 для стробирования частей посылки сигнала, располагаюЩихся у заднего фройта

ОСНОВНОЙ ЗОНЫ.

Под действием импульсов, соответствующих переднему (с m+1 выхода регистра

32 и заднему) с m выхода регистра 33 фронтам основной зоны, триггер 38 вырабатывает сигнал, соответствующий по дли- . тельности основной зоне. Этот сигнал с триггера 32 подается на первый вход блока совпадения 39, на второй вход которой подаются синхроимпульсы с частотой fp, На выходе блока совпадения 39 получается

"гребенка" для основной зоны, Сигналы

1781,833 этой "гребенки" через первый выход коммутатора 2 подаются на первый вход преобразователя 3 для стробирования посылок сигнала.

С использованием сформированных

"гребенок" в блоках 3, 7, 9, 12, 14 осуществляется преобразование получаемых из канала связи посылок сигнала в "пачки" ков 3, 7, 9, 12, 14 поступают соответственно на первые входы интеграторов 4, 8, 10, 13, 15. B интеграторах производится счет импульсов в "пачках" по посылкам в прямом и инвертированном виде и сравнение результатов подсчета импульсов "пачек" прямой и инвертированной частей посылки, поступающей из канала, принимается решение об амплитуде посылки в.соответствующей зо15

20 не

С выхода интегратора 4 сигнал зарегистрированной посылки поступает на общий выход устройства регистрации, а также на вход 1 решающего блока 5. С выхода интег25 раторов 8, 10, 13, 15 сигналы о значении посылки подаются соответственно на 2, 3, 4, 5, входы решающего блока 5, в котором,производится оценка возможности расшйрения основной зоны или необходимости ее

30 уменьшения

В решающем блоке 5 на. блоках сравнения 42-45 производится в момент прихода сигнала с выхода линии задержки 52 попарное сравнение величины сигналов, 35 получаемых в интеграторах вспомогательных зон (блоки 8, 10, 13, 15) и в интеграторе основной зоны (блок 4), Результаты сравнения подсчитываются счетчиками 7 — 10,. подключенными к выходам блоков сравнения.

Цепь сброса всех счетчиков через делитель

53 и линию задержки 52 подключена через вход 10 блока 5 к выходу 3 коммутатора 1.

Число посылок сигнала в выборке составляет К посылок, Через каждые К посылок

40 счетчики блока 5 сбрасываются в "0". Результат сравнения сигналов оцейки амплитуд основной-. зоны и внешней вспомогательной зоны переднего фронта выдается с блока 42 на счетчик 48, При на45 личии К совпадений оценок с выхода счет- 50 чика выдается импульс, который через открытые ключи 54, 56 и выход 1 блока 5 поступает на счетчик 6, изменяя его состоя-. ние продвижением "1", на регистр 32, для расширения основной зоны по переднему 55 фронту.

При этом в коммутаторе 2 производится переключение среди элементов И 16-22 и осуществляется сдвиг передней границы основной эоны в сторону расширения. Одсинхроимпульсов основной зоны и вспомогательных зон. Эти "пачки" с выходов бло- 10 новременно с сравнением в блоке 42 производится сравнение в блоке 43 значения амплитуды основной зоны с инвертированным значением внутренней вспомогательной зоны, и на счетчик 49 ничего не подается. Если бы амплитуды не совпадали, то на вход счетчика 49 поступали бы импульсы после каждой посылки. По результату счета выдается сигнал через нормально открытый ключ 57 на счетчик 6, изменяя его состояние для осуществления в коммутаторе 2 соответствующей сдвигу передней границы основной зоны, в сторону сокращения основной зоны. Одновременно сигнал с выхода счетчика 49 подается на вход ключа 54, закрывая его и исключая подачу на счетчик

6 сигнала о расширении. основной зоны.

С использованием эл. 44, 55, 58 и 45, 47, 51, 59 блока 5 производятся аналогичные действия по изменению величины основной зоны по заднему фронту.

Предусмотренные в блоке 5 третий, четвертый, пятый, шестой ключи 56, 57, 58, 59 предназначены для прекращения подачи на соответствующие входы реверсивных счетчйков 6, 11 импульсов при нахождении реверсивных счетчиков в состояниях, соответствующих максимальному увеличению и максимальному уменьшению основной зоны интегрирования. В этом случае по сигналам какого-либо из выходов 6, 7, 8, 9 блока 2, подаваемых через входы 6; 7, 8, 9 блока 5 на вторые входы ключей, происходит

Запйрание соответствуЮщего ключа. Как видно иэ описания устройства, особенностью его функционирования при работе на канале связи является наличие зоны интегрирования большей величины по сравнению с устройствами, где величина эоны фиксированная.

Формула изобретения

Устройство регистрации телеграфных посылок, содержащее кольцевой коммутатор, последовательно соединенные первый преобразователь сигналов посылок и пер вый интегратор, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности правильной регистрации посылок, введены управляемый коммутатор, первый, второй реверсивные счетчики, второй, третий. четвертый, пятый преобразователи сигналов посылок, второй, третий, четвертый, пятый интеграторы и решающий блок, при этом первый и второй входы управляемого коммутатора подключены соответственно к первому и второму выходам кольцевого коммутатора, третий и четвертый входы управляемого коммутатора подключены к выходам соответственно первого и второго реверсивных счетчиков, пятый вход управ1781833

1"

От гейврат6ра оинхоонмпульоов

Хихон канала овнза ляемого коммутатора и вход кольцевого регистра являются входом синхронизации устройства, первый, второй, третий, четвертый, пятый выходы управляемого коммутатора соответственно соединены с первыми входами первого, второго, третьего, четвертого, пятого преобразователей сигналов посылок, вторые входы которых соединены и являются входом устройства, выходы преобразователей сигналов посылок через соответствующие интеграторы подключены к первому, второму, третьему, четвертому, пятому входам решающего блока, шестой, седьмой, восьмой, девятый выходы соответственно с шестым, седьмым, 5 восьмым, девятым входами и решающего блока, десятый вход которого соединен с третьим выходом кольцевого коммутатора, первый и второй выходы решающего блока соединены с входами первого реверсивного

10 счетчика, третий и четвертый выходы — с входами второго реверсивного счетчика;

1781833

1781833

Составитель Н.Лазарева

Техред M.Ìoðãåíòàë Корректор Т.Палий

Редактор

Производственно-издательский комбинат "Патент", r. Ужгород, yn,Гагарина, 101

Заказ 4282 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5