Устройство для обмена информацией

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к устройствам для обмена информацией между процессором и абонентами через буфер в многопроцессорной системе с ее отображением на дисплее, и может быть использовано при построении программируемых многопроцессорных контроллеров . Цель изобретения - расширение . функциональных возможностей устройства за счет обеспечения возможности обмена в случайные промежутки времени по инициативе любого абонента. Для достижения цели в устройство для обмена информацией, содержащее п периферийных абонентов 4.1 - 4.п, буферную память 2, первый шинный формирователь 3, первую группу шинных формирователей 3.1-З.п абонентов 4.1--4 п второй шинный формирователь 6, вторую группу шинных формирователей 6.1-б.п, введены дешифратор 5, дешифратор состояния 7, группы элементов ИЛИ 7.1-7.п и многорежимное ОЗУ клавиатуры 8. Роль буферной памяти 2 в данном случае выполняет 03-У индикации емкостью 16 байтов контролл ера индикации и клавиатуры КР580ВВ79. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (s>)s G 06 F 11/00

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ L

К ПАТЕНТУ

»

I»

Ъ»

1 (21) 4782929124 (22) 04.12.89 (46) 23,12.92. Бюл. ¹ 47 (71) Самарское специальное конструкторское бюро Научно-производственного объединения "Нефтехимавтоматика" (72) В.H.Àñòàïîâ и Г.Г,Воробьев (73) Самарское специальное конструкторское бюро Научно-производственного o6beдинения "Нефтехимавтоматика" (56) Авторское свидетельство СССР

¹410392,,кл. G 06 F 13/06. 1971.

Шевкогляс Б.В, Микропроцессорные структуры. Гл. 12,2. Обмен информацией процессорами через буфер типа FiF0, — М.:

Радио и связь, 1986 с. 255-256, (54) УСТРОЙСТВО ДЛЯ ОБМЕНА ИНФОРМАЦИЕЙ (57) Изобретение относится к вычислительной технике, в частности к устройствам для обмена информацией между процессором и .абонентами через буфер в многоп роцессор.„„5LI „„1784103 А3

2 ной системе с ее отображением на дисплее, и может быть использовано при построении программируемых многопроцессорных контроллеров, Цель изобретения — расширение . функциональных возможностей устройства за счет обеспечения возможности обмена в случайные промежуткИ времени по инициативе любого абонента. Для достижения цели в устройство для обмена информацией, содержащее и периферийных абонентов 4,1 — 4.п, буферную память 2, первый шинный, формирователь 3. первую группу шинных формирователей 3,1-3.пабонентов 4,,1--4.п. второй шинный формирователь 6, вторую группу шинных формирователей 6.1-6.п, введены дешифратор 5, дешифратор состояния 7, группы элементов ИЛИ 7.1-7,п и многорежимное ОЗУ клавиатуры 8. Роль буферной памяти 2 в данном случае выполняет

ОЗУ индикации емкостью 16 байтов контролл ера индикации и клавиатуры

КР580ВВ79. 1 ил.

1784103

Изобретение относится к области вы- данного сигнала начинает поочередной опчислительной техники. в частности к устрой- рос каждого периферийного абонента по ствам для обмена информацией между алгоритму, описанномудля первого случая. процессорами, клавиатурой и процессора- 3 случай: инициатором является клавиами через буфер в многопроцессорной сис- 5 тура. теме с ее отображением на дисплее и может При нажатии клавиши с кодом опредебыть использовано при построении про- ленного периферийного абонента 4.1-4.п граммируемых контроллеров нэ базе мик- процессор 1 анализирует данный код. и в ропроцессоров.. соответствии с ним подключает выбранный

Целью изобретения является расшире- 10 оператором процессор, B результате такой ние функциональных возможностей за счет коммутации клавиатура и блок регистров обеспечения возможности обмена в случай- отображения становится частью архитектуные промежутки времени по инициативе ры выбранного процессора. По окончании любого абонента. работы с клавиатурой, нажимают клавишу с

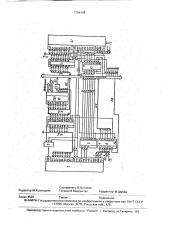

На чертеже приведена функциональная 15 кодом конца связи. который периферийный схема устройства. абонент анализирует и выдает сигнал конец

Устройство состоит из процессора1, бу- связи (к.с.) на вход ПР процессора 1. котоферной памяти 2, первого шинного форми- рый переводит схему в исходное состояние, рователя 3, первой группы шинных . С функциональной точки зрения второй формирователей 3,1 — З.п, процессоров — 20 шинный формирователь 6 и вторая группа абонентов4.1 — 4.n,äåøèôðàòîðà5, второго шинных формирователей 6.1 — 6.п являются шинного формирователя 6, второй группы ключами, которые под управлением процесшинных формирователей элемента ИЛИ 7 . сора 1, подключают управляющие входы будешифратора состояния, группы элементов ферной памяти 2 к шине управления

ИЛИ б,п, 7.1 — 7.п многорежимного ОЗУ(МО- 25 соответствующего абонента 4,1-4.п или

ЗУ) клавиатуры 8, буфера клавиатуры 9, ре- процессора 1. а также при работе с клавиагистров отображения информации 10, турой шинные формирователи 6 и 6.1 6.п

Работа устройства осуществляется сле- подключают линию сигнала прерывания от дующим образом. М03У 8 клавиатуры на вход дешифратора

Исходное состояние устройства такое. 30 состояния 7. На вход СБ (разрешение выхочто буферная память 2, МО3У клавиатуры 9 да) формирователя 6 также поступает сиги блок регистров отображения информации нал с дешифратора 5.

10 подключены к процессору 1, Роль буферной памяти 2 в данном слу1 случай: инициатором обмена является чае (фиг. 1) выполняет ОЗУ индикации. это процессор 1, 35 запоминающее устройство с произвольным

Процессор 1 через порт Р1 на дешифра- доступом емкостью шестнадцать 8-разрядтор 5 выставляет номер периферийного ных слов-йредназначено для хранения инпроцессора, с которым необходимо произ- формации. После загрузки в КР580ВВ79 вести обмен информацией, Дешифратор 5 управляющих слов чтения и записи содеротключает буферную память 2 от процессо- 40 жимое ОЗУ индикации может быть прочитара и через выбранный из первой группы но и изменено процессором с помощью шинный формирователь 3.1--3.п подключает.. команд 1N и QVT, шину данных буферной памяти 2 к порту С клавиатуры может задаваться любая ввода-вывода РО выбранного абонента 4,1 — информация и в любые моменты времени, 4,п, а через шинный формирователь второй 45 если программы прерывания не запрещены группы 6.1 — 6.п подключает шину управле- т.е, когда не занята общая магистраль, при ния буферной памятью: После такой комму- нажатии клавиши вырабатывается сигнал тации буферная память 2 становится частью нэ прерывание и начинает работать проархитектуры одного из абонентов 4.1 — 4.п, грамма обслуживания прерывания от клавион может читать и записывать в нее любую 50 атуры по заданному алгоритму. информацию, В концесвязи периферийный Регистры 10 управляются по внугрен.абонент через порт Р1 выставляет сигнал ней шине аппаратными средствами контконец связи (к.с,), который вызывает преры- роллера клавиатуры индикации КР580ВВ79. вание процессора 1, который переводит Синхронизация контроллера осуществляетсхему в исходное состояние. 55 ся через шину управления (ШУ) сигналом ТО

2 случай: инициатором является пери- от внутреннего генератора процессора 1; ферийный абонент. Периферийный абонент . Ф о р м у л а и з о б р е т е н и я

4.1 — 4.п через порт Р1 выставляет сигнал Устройство для обмена информацией начало связи (н.с.), вызываощий прерыва- между абонентами и процессором. содерние процессора 1. который при получении жащее буферную память, первый шинный

1784103

5 6 формирователь, первую группу шинных входы дешифратора являются входами устформирователей, причем первая группа ройства для подключения к шине адреса входов/выходов буферной памяти соедине- процессора, выходы дешифратора соединена с первой группой входов/выходов перво- ны с первыми входами элементов ИЛИ групго шинного формирователя, вторая группа 5 пы. с входами управления передачей первой входов/выходов которого является группой и второй групп шинных формирователей. входов/выходов устройства для подключе- выход буферной памяти соединен с инфорния к шине данных процессора, вторая мационными входамй шйнных формировагруппа входов/выходов буферной памяти телей второй группы, выходы которой является группой входов/выходов устрой- 10 соединены с вторыми входами соответствуства для подключения к первой группе вхо- ющих элементов ИЛИ группы и являются дов/выходов шинных формирователей выходами устройства для подключения к сопервой группы, группы выходов котбрйх Фв= " " ответствующему разряду шины управления ляются группами выходов устройства для . одноименных абонентов, выходы элементов подключения шин данных соответствующих 15 ИЛИ группы являются выходами устройства абонентов, управляющие входы буферной для подключения к входам прерывания однопамятисоединенысвыходами второгошин- именных абонентов, выходы начала и конца ного формирователя, информационные вхо- -запросов которых подключены к информациды которого являются входами устройства онным входам дешифратора состояния, выдля подключения. к шине управлений .про- 20 ход которого подключен к входу прерывания цессора, о т л и ч а ю щ е е с я тем. что, с процессора. выход втЬрого шинного формицелью расширения функциональных воз- . рователя к входу прерывания процессора, выможностейза счетобеспечения возможно- . код второго шинного формирователя сти обмена в случайные промежутки подключен к входам шинных формироватевремени по инициативе любого абонента, 25 лей второй группы и к информационным вхоустройство содержит дешифратор, дешиф- дам дешифратора состояния. и+1-й выход .ратор состояния (элемент ИЛИ 7), группу дешифратора(гдеп — числоабонентов)соедиэлементов ИЛИ, вторую группу шинных нен с входами управления первого и второго формирователей. причем информационные шинных формирователей.

1784103

Составитель 8,Остапов

Редактор М.Кузнецова Техред М.Моргентал Корректор И.Шулла

Заказ 4530 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35. Раушская наб„4/5

Производственно-издательский комбинат "Патент". r. Ужгород, ул,Гагарина. 101