Преобразователь перемещения в код

Иллюстрации

Показать всеРеферат

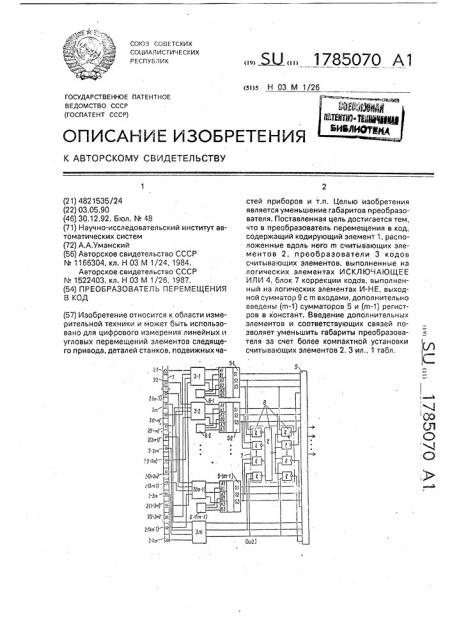

Изобретение относится к области измерительной техники и может быть использовано для цифрового измерения линейных и угловых перемещений элементов следящего привода, деталей станков, подвижных частей приборов и т.п. Целью изобретения является уменьшение габаритов преобразователя . Поставленная цель достигается тем, что в преобразователь перемещения в код, содержащий кодирующий элемент 1, расположенные вдоль него m считывающих элементов 2. преобразователи 3 кодов считывающих элементов, выполненные на логических элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 4, блок 7 коррекции кодов, выполненный на логических элементах И-НЕ, выходной сумматор 9cm входами, дополнительно введены (т-1) сумматоров 5 и (т-1) регистров в констант. Введение дополнительных элементов и соответствующих связей позволяет уменьшить габариты преобразователя за счет более компактной установки считывающих элементов 2. 3 ил,, 1 табл. сл

СОЮЗ COOFTCКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (II) (51)5 Н 03 M 1/26

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОбРЕТЕНИЯ

I Я) (.л

С) II

С) гр

2P m

2(гм!

2-2т

?(2i2nP г-ГЗ «) 2-,1а г(/ 3m

2Г2

2Фл

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4821535/24 (22) 03,05.90 (46) 30.12.92. Бюл. N 48 (71) Научно-исследовательский институт автоматических систем (72) А.А,Уманский (56) Авторское свидетельство СССР

N 1166304, кл. Н 03 М 1/24, 1984.

Авторское свидетельство СССР

Л 1522403, кл. Н 03 М 1/26, 1987. (54) ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЯ

В КОД (57) Изобретение относится к области измерительной техники и мажет быть использовано для цифрового измерения линейных и угловых перемещений элементов следящего привода, деталей станков, подвижных частей приборов и т.п, Целью изобретения является уменьшение габаритов преобразователя. Поставленная цель достигается тем, что в преобразователь перемещения в код, содержащий кодирующий элемент 1, расположенные вдоль него m считывающих элементов 2, преобразователи 3 кодов считывающих элементов, выполненные на логических элементах ИСКЛЮЧАЮЩЕЕ

ИЛИ 4, блок 7 коррекции кодов, выполненный на логических элементах И-НЕ, выходной сумматор 9 с m входами, дополнительно введены (m-1) сумматоров 5 и (m-1) регистров в констант. Введение дополнительных элементов и соответствующих связей позволяет уменьшить габариты преобразователя за счет более компактной установки считывающих элементов 2, 3 ил„1 табл.

1 785070

Изобретение относится к области измерительной техники и может быть использовано для цифрового измерения линейных и угловых перемещений элементов следящего привода деталей станков, подвижных частей приборов и т.п.

Известны применяемые для этой цели преобразователй перемещение-код, содержащйе кодовую- шкалу, расположенные вдоль нее считывающие элементы и преобразователь кода считывающих элементов в двоичный арифметический. Недостатком таких преобразователей перемещения в код является возможность появления сбоев выходного кода при погрешностях расположения считывающих элементов, не превышающих величины кванта преобразования.

Этот недостаток устранен в преобразователе перемещения в код, содержащем кодирующий элемент с периедом d, m групп по Ксчитывающих элементов, m преобразователей кодов 1-го, (i+m)-го, ...(I+(K-1)m)-го считывающих элементов, блок коррекции этих кодов и выходной сумматор с m входами. Указанный преобразователь наиболее близок к предлагаемому. его недостаток— большие габариты преобразователя вследствие того, что считывающие элементы в известном преобразователе перемещения в код должны быть расположены вдоль кодирующего элемента с шагом

d (n + — ), где n — целое число, что су1

2кгп щественно ограничивает возможность выбора оптимальных размеров преобразователя. Например, при ко=8, шаг расположения считывающих элементов должен выбираться из следующих допустимых значений; 0,0625d; 1,0625d; 2,0625d. Те же значения, выраженные в квантах преобразования 1; 17; 33...

Целью предлагаемого изобретения является уменьшение габаритов преобразователя.

Поставленная цель достигается тем, что в преобразователь перемещения в код, содержащий равномерно квантованный кодирующий элемент с периодом d, m преобразователей кодов, m групп по К считывающих элементов, где К вЂ” число кратное двум, выходы i-го, (i+m)-ro, (i+2m)-го, (i+(K1)m}-го считывающих элементов соединены с входами i-го преобразователя кодов, выходной сумматор на m слагаемых, выходы которого являются выходами преобразователя, выходы m-ro преобразователя кодов соединены со входами младших разрядов

m-ro слагаемого выходного сумматора, а выходы двух старших разрядов m-ro преобразователя кодов соединены с m-й группой входов блока коррекции, I-й выход которого соединен со входом старшего разряда i-ro слагаемого выходного сумматора, в него введены (m-1) сумматоров и (m-1) регистров

5 констант, а считывающие элементы расположены с шагом (1 + 2n ), где и—

2Km целое число, выходы каждого из преобразователей кодов кроме m-ro соединены со вхо10 дами первого слагаемого одноименных сумматоров, входы второго слагаемого которых подключены к выходам одноименных регистров констант, выходы каждого из сумматоров соединены со входами младших

15 разрядов одноименного слагаемого выходного сумматора, выходи двух старших разрядов каждого из сумматоров соединены с одноименной группой входов блока коррекции кодов.

20 Все признаки, указанные в отличительной части формулы изобретения, каждый в отдельности, известны и проявляют присущие им свойства, Однако, совокупность введенных признаков обеспечивает получение

25 сверхсуммарного положительного эффекта, заключающегося в уменьшении габаритов преобразователя за счет существенного увеличения количества допустимых значений шага расположения считывающих эле30 ментов вдоль кодирующего элемента, что позволяет оптимально компоновать преобразовател ь. В ведение до пол нител ьных сумматоров и регистров, в которые записаны константы, подсчитанные по выражению, 35 приведенному в описании изобретения, изменяют слагаемые, поступающие на выходной сумматор таким образом, что функционирование предлагаемого преобразователя, в отличие от известного стано40 вится возможным при многих значениях шага расположения считывающих элементов, При mK= — 8, как уже говорилось выше, в известном преобразователе необходимо располагать считывающие элементы с ша45 гом 1; 17; ... и т.д, квантов преобразования, а в предлагаемом — 1; 3; 5; 7; 9; 11; 13; 15;

17; ... ит.д, Сущность изобретения поясняется чертежами, где на фиг,1 представлена блок-схе50 ма предлагаемого преобразователя в общем случае, на фиг.2 блок-схема при m

К=8, на фиг.3-допустимые варианты расположения считывающих элементов вдоль кодирующего элемента при m К=8 (а, и — для

55 известного преобразователя перемещения в код; а, б, в, r, д, е, ж, з, и — для предлагаемого)..

Предлагаемый преобразователь перемещения в код содержит кодирующий элемент 1, расположенные вдоль н; 1785070 считывающие элементы 2-1, 2-2,...2-4m, преобразователи 3-1....3-m кодов считывающих элементов, выполненные на логических элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 4, трехразрядные сумматоры 5-1, 5-2,...,5-(m-1), регистры 6-1, 6-2,...,6-(m-1) констант, блок 7 коррекции кодов, выполненный на логических элементах И-Н Е 8, выходной сумматор

9 с m входами.

Выходы 2-1-го, 2-(1+m)-ro, 2-(1+2m)-ro u

2-(1+3m)-го считывающих элементов связаны с входами преобразователя 3-1 кодов считывающих элементов в трехразрядный двоичный арифметический код; выходы 2-2ro, 2-(2+m)-ro, 2-(2+2m)-го и 2-(2+3m)-ro считывающих элементов — с входами преобразователя 3-2; выходы 2-(m-1)-го, 2(2m-1)-ro, 2-(3m-1)-го и 2-(4m-1)-ro считывающих элементов — с входами преобразователя 3-(е-1); выходы 2-m-го, 22m-го, 2-3m-го и 2-4m-го считывающих элементов — с входами преобразователя З-m, Выходы преобразователей 3-1-3-(m-1) связаны соответственно, с входами трехрэзрядных сумматоров 5-1-5-(m-1), выходы которых связаны с входами с 1-ro no m-1-го сумматора 9, а выход преобразователя 3-m связан непосредственно с m-м входом сумматора 9. С другими входами трехрэзрядных сумматоров соединены, соответственно, выходы трехразрядных регистров 6-1-6-(m-1) констант, Два старшие разряда трехразрядных выходов сумматоров 5 и преобразователя 3 m связаны с входами блока коррекции 7, Выходы блока 7 коррекции соединены с входами сумматора

9. Выход сумматора 9 является выходом предлагаемого преобразователя.

Работает предлагаемый преобразователь следующим образом. При перемеще. нии кодирующего элемента 1 относительно считывающих элементов 2 последние оказываются попеременно то против активных участков кодирующего элемента, то против пассивных. Соответственно, на выходах считывающих элементов 2 появляются сигналы высокого или низкого уровня, образующие К.m-разрядный код считывающих элементов. Из этого кода формируются m групп по К разрядов таким образом, что в каждой группе оказываются сигналы l-го, (l+m)-ro, (I+2m)-го, (I+(K-1)т)-ro считывающих элементов (I-1,2,3...m), Полученные таким образом К-разрядные коды, каждый из которых при перемещении считывающих элементов 2 вдоль кодирующего элемента 1 на величину его периода образует 2К неповторяющихся комбинаций, подаются на входы

m преобразователей 3 кода считывающих элементов в двоичный арифметический код.

40

45 с! =-(1+2К вЂ” (— ) и

) °

5

В известном преобразователе перемещения в код двоичные арифметические коды с выходов преобразователей 3 непосредственно подаются на входы сумматора 9. Правильное, без сбоев нарастание кодов на выходе сумматора 9 (T.å, на выходе известного преобразователя пере мщения в код) происходит только в том случае, если в начальном положении кодирующего элемента

1 относительно считывающих элементов 2 все арифметические коды на входах сумматора 9 равны нулю. Именно по этой причине в известном преобразователе, считывающие элементы 2 должны располагаться при

К m=8 с шагом 1 или 17 или 33 ... и Ъ.д. квантов образования, что является его недостатком, При других значениях шага расположения считывающих элементов, в начальном положении кодирующего элемента нулю равен только код на выходе преобразователя З-m, на выходе остальных преобразователей коды смещены на некоторую величину, зависящую от номера преобразователя, шага расположения считывающих элементов и их количества. В этом случае правильность нарастания кода на выходе сумматора 9 нарушается. В предлагаемом преобразователе перемещения в код для компенсации упомянутого смещения коды с выходов всех преобразователей

3, кроме З-m-го, а именно преобразователей

3-1, 3-2,...3-(m-1), подаются на один иэ входов трехрэзрядных сумматоров 5-1-5-(m-1).

На другой вход трехразрядных сумматоров с выхода регистров 6 констант подаются постоянные коды — такие, что в сумме с кодами преобразователей 3 они в начальном положении кодирующего элемента дают на выходах сумматоров нуль. Благодаря этому правильное, без сбоев нарастание кода на выходе сумматора 9 (выходного кода преобразователя перемещение-код) обеспечивается при шаге расположения считывающих элементов, равном любому нечетному целому числу квантов преобразования, Значения констант С;, хранящихся в регистрах 6. определяются по выражению:

Третье слагаемое в этом выражении и результат Cl берутся по модулю 2К; квадрэтные скобки означают, что берется целая часть от выражения в скобках, l=1,2„,.m-1 — номер регистра 6.

К двоичным арифметическим кодам на вь.ходах сумматоров 5 и преобразователя

3-m блок 7 коррекции этих кодов выполненный на логических элемента И-НЕ, в соот1785070 ветствии с логикой работы этих элементов. в необходимых случаях добавляет дополнительный старший разряд, аналогично тому, как это происходит в известном преобразователе.

В таблице приведены коды на входах и выходах основных узлов предлагаемого преобразователя для случая. когда m=2, К=п=4 при перемещении считывающих элементов 2-1-2-8 вдоль кодирующего элемента 1 вверх по фиг.2, В соответствии с формулой изобретения. в этом случае в состав преобразователя перемещения в код входит один регистр констант, в которых должно быть записано число (1+2К вЂ” (— 1 ) л

» «(1+2 4 — (1)

= 41о = 1002

)«

2 (Индекс указывает на основание системы счисления). Из таблицы следует, что благодаря суммИрованию выходного кода преобразователя 3-1 с константой, записанной в регистр 6, на вход сумматора 9 подаются слагаемые, сумма которых, с учетом коррекции блоком 7, представляет собой правильно нарастающий четырехразрядный двоичный арифметический код. Если бы на вход сумматора 9 непосредственно подавался код с выхода преобразователя 3-1, как в известном преобразователе, сумма на его выходе (и; следовательно, на выходе известного преобразователя перемещения в код) изменялась бы неправильно, со сбоями, Предпочтительное значение количества

К считывающих элементов в каждой из m групп равно четырем, т,к. при этом достигается максимальная величина допуска на расположение считывающих элементов.

Таким образом, по сравнению с прототипом, предлагаемый преобразователь работает при значительно большем количестве допустимых значений шага считывающих элементов: если в известном преобразователе шаг расположения считывающих элементов в рассмотренном примере должен составлять 1, 17, 33 и т.д, квантов преобразования, то.в предлагаемом он может быть равен любому нечетному числу, Это особенно важно для преобразо5 вателей с большим количеством считывающих элементов, например, основанных на применении интегральных линеек фотопри- . емников, приборов с зарядовой связью и др.

Конструкция предлагаемого преобразова10 теля, в частности при использовании интегральных линеек фотоприемников, может быть при этом получена оптимальной, а его габариты — минимальными.

Формула изобретения

15 Преобразователь перемещения в код, содержащий равномерно KBBHTOBBHHblA кодирующий элемент с периодом d, m преобразователей кодов, m групп по k считывающих элементов, где k — число крат20 ное двум, выходы i-ro (i+m)-го, (i+2m)-ro (i+(k1)m)-го считывающих элементов соединены с входами i-го преобразователя кодов, выходной сумматор на m слагаемых, выходы которого являются выходами преобразова25 теля, выходы m-ro преобразователя кодов срединены с входами младших разрядов mro слагаемого выходного сумматора, а выходы двух старших разрядов m-ro преобразователя кодов соединены с m-й

30 группой входов блока коррекции,i-й выход которого соединен с входом старшего разряда 1-го слагаемого выходного сумматора, отличающийся тем, что, с целью уменьшения габаритов преобразователя, а

35 него введены (m-1) сумматоров и (m-1) регистров констант, а считывающие элементы б расположены с шагом (1 + 2п ) 2, где

2К(п

n — целое число, выходы каждого из преоб40 разовэтелей кодов, кроме m-ro, соединены с входами первого слагаемого одноименных сумматоров, входы второго слагаемого которых подключены к выходам одноименных регистров констант, выходы каждого из сумма45 торов соединены с входами младших разрядов одноименного слагаемого выходного сумматора, выходы двух старших разрядов каждого из сумматоров соединены с одноименной группой входов блока коррекции кодов, 50

178507 О ментов

Ко на вхо е

Код на выходе сумматора

- Ко на выхо е

Код на входе сумматора 9 п/и

2-6 г-у

2-4

2-2 г-з

З-I

2-1

3-2

З-2

-o о г з

5

7 в

»

12

1З

14

t6 о о о о о о о

1

1

1

1.

1

1

1

О о

О о о о о о

Код считываю их эле

О о о о

1

1

I

1

О о о о

1

1 О

О о о о о о о

1

1

1 о о

1

1

1

1 о о о о о о I

О о о о о о о

О

1

1

1

»»

»ю

»10

»00

»0Î

1ÎÎ0 юоо

0000 оооо

000t

ООО! ао»

ООИ

0t»

0»1

1t» оооо оооо

ООО!

0001

0λ

ОО»

0»1

О!»

»и

»1 I

»1О

»10

»оо

»00

1ООО юоо

101

Ю!

»О

»о

»1

»1

001

ÎÎ1 ою ою о» о»

100

ÎÎ1

00t ою

010 ои о»

1ÎÎ

1ÎÎ

10!

Ю!

»О

»о

»1

1»

000

00t

001

О10

О1О о» о»

1ÎI

101

»О

»О

»t

»1

1Î0Î

1001

10Î1

1ОЮ

1ОЮ

t0» юи

»00

11ОО

»О1

О1О! о»о о»о

О»1

0!И

1ÎÎ1

ЮО1

Ю10

10!О

1О»

10»

»00

»оо

ИО1

»О1 о»о

0»0

О»!

О!»

1000

ÎÎ01 оою

00»

ОЮО

ОЮ!

0»0

ОИ!

1ООО

1ÎÎ1

t0»

»00

»О!

1»0

»»

1785070 о

Р-У

"оставитель А.Уманский

Техред М.Моргентал Корректор A,Moòûëü

Редактор

Прои водственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина. 101

Заказ 4370 Тираж Подписное

БНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5