Демодулятор фазоманипулированных сигналов

Иллюстрации

Показать всеРеферат

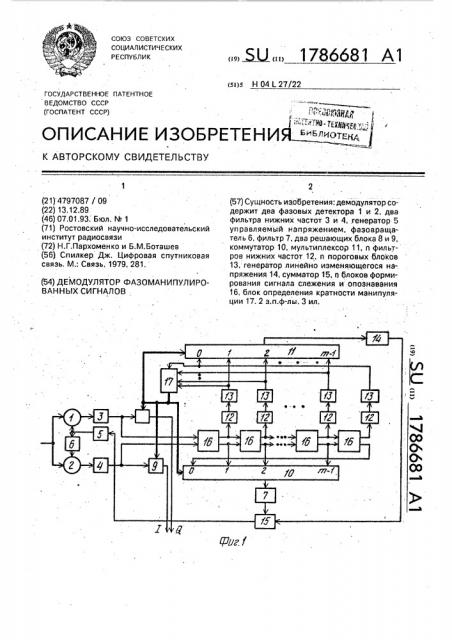

Сущность изобретения: демодулятор содержит два фазовых детектора 1 и 2, два фильтра нижних частот 3 и 4, .генератор 5 управляемый напряжением, фазовращатель 6, фильтр 7. два решающих блока 8 и 9, коммутатор 10, мультиплексор 11, п фильтров нижних частот 12, п пороговых блоков 13, генератор линейно изменяющегося напряжения 14, сумматор 15. п блоков формирования сигнала слежения и опознавания 16, блок определения кратности манипуляции 17. 2 з.п.ф-лы. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 Н 041 27/22

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4797087 / 09 (22) 13.12.89. (46) 07,01.93, Бюл. М 1 (713 Ростовский научно-исследовательский институт радиосвязи (72) Н.Г.Пархоменко и Б.M.Áoòàøåâ (56) Спилкер Дж. Цифровая спутниковая связь, М,: Связь, 1979, 281. (54) ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ

„,!Ы„„1786681 А1

2 (57) Сущность изабретения: демодулятор содержит два фазовых детектора 1 и 2, два фильтра нижних частот 3 и 4, генератор 5 управляемый напряжением, фазовращатель 6, фильтр 7, два решающих блока 8 и 9, коммутатор 10, мультиплексор 11, и фильтров нижних частот t2, п пороговых блоков

13, генератор линейно изменяющегося на-. пряжения 14, сумматор 15, п блоков формирования сигнала слежения и опознавания

16, блок определения кратности манипуляции 17. 2 з.п.ф-лы. 3 ил.

1786681

Изобретение относится к радиотехнике и может быть использовано в аппаратуре систем связи с фазовой манипуляцией (Ф М).

Целью изобретения является демодуля- 5 ция сигналов в условиях априорно неопределен ной кратности и повышение помехоустойчивости демодулятора ФМсигналов, На фиг. 1 изображена функциональная 10 схема демодулятора фазоманипулированных сигналов; на фиг. 2 - функциональная схема блока формирования сигнала слеже-. ния и опознавания; на фиг. 3 — функциональная схема блока определения кратности 15 манипуля ции.

Демодулятор ФМ-сигналов содержит (фиг. 1) первый 1 и второй 2 фазовые дет ек- . торы, первые входы которых обьединены и соединены с входом демодулятора, а выхо- 20 ды соединены с входами .соответственно синфазного первого 3 и второго квадратурного4фильтров ни>кних частот, Второй вход первого фазового детектора 1 соединей с выходом генератор 5, управляемого напря- 25 жением, непосредствейно и через фазавращатель 6 йа 90О, с вторым входом фазового детектора 2.

В состав демодулятора входят фил ьтр петли фапч 7, два решающих блока 8 и 9, 30 коммутатор 10, мультиплексор 11, третьи фильтры нижних частот 12, пороговые блоки

13, генератор линейно изменяющегося напряжения 14, сумматор 15, блоки формирования сигйала слежения и опознавания 16 и 35 блок определения кратности манипуляции

17.

Первые входы первого 8 и второго 9 решающих блоков подключены к выходам соответственно первого 3 и второго 4 филь- 40 трав нижних частот и соответственно к первому и второму входам блока формирования сигнала слежения и опознавания 1.6, первый и второй выходы которого через после-. довательно соединенные последующие 45 блоки формировайия сигнала слежения и опознавания 16 подключены соответственно к первому и второму входам последнего блока формирования сигнала слежения и опознавания 16. Первый выход каждого 50 . блока формирования сигнала слежения и опознавания 16 через последовательно соединенные третий фильтр нижних частот 12 и пороговый блок 13 соединен с соответствующим входом блока определения кратно- 55 сти манипуляции> 17 и с соответствующим входом мультиплЬксора 11, выход которого через генератор линейно изменяющегося напряжения 14 соединен с первым входам сумматора 15, выход которого соединен с входом генератора 5, управляемого напряжением, Второй выход каждого блока формирования сигнала слежения и опознавания 16 соединен с соответствующим входом коммутатора 10, выход которого через фильтр 7 соединен с вторым входом сумматора 15. Выход блока определения кратности манипуляции 17 соединен с управляющим входом мультиплексора 11, управляющим входом коммутатора 10 и вторыми входами первого 8 и второго 9 решающих блоков, выходы которых являются выходами демодулятора.

Каждый блок формирования сигнала слежения и опознавания 16 содержит (фиг.

2) два перемно>кителя 18 и 19, вычитатель

20, усилитель 21 и сумматор 22, первый вход которого соединен с первым входом вычитателя 20 и первым входом первого перемножителя 18, второй вход которого соединен с тарым входом вычитателя 20 и вторым входом сумматора 22, выход которого соединен с первым входом второго перемножителя

19, второй вход которого подключен к выходу вычитателя 20. Вход усилителя 21 подключен к выходу первого перемножителя

18, первый и второй входы которога являют-, ся соответственно первым и вторым входами блока формирования сигнала слежения и опознавания 16, первым и вторым выходами которого являются соответственно вы-. ход второго перемножителя 19 и выход усилителя 21. Усилитель 21 имеет коэффициент усиления по напряжению, равный двум.

Блок определения кратности манипуляции 17 содержит (фиг. 3) шифратор 23 и элементы И 24, выходы которых соединены с входами шифратора 23, причем разрешающие входы всех. элементов И 24 объединены, а выходы всех элементов И 24, кроме первого, соединены с соответствующими входами последующих элементов И 24, разрешающие и сигнальные входы которых являются входами блока определения кратности майипуляции 17, выходом которого является выход шифратора 23.

Демодулятор работает следующим образом. Входной М-позиционный ФМ-сигнал с единичной амплитудой можно представить в виде;

S x(t) =сов(в,т+ К ), 2л где в> — несущая частота сигнала;

М = 2 — количество позиций ФМ;

m — кратность манипуляции, 1786681

К вЂ” целое число, выбираемое из множества (1, 2, „., M) в соответствии с передаваемыми информационными символами.

После умножения ФМ-сигнала на опорное колебание Son(t), имеющего вид:

$ОП(1) =2cos(an t+ p), где р- фазовое рассогласование между сигналом и опорным колебанием в фазовом детекторе 1, иумножения насдвинутоена90 колебание в фазовом детекторе 2 имеем на выходах синфазного 3 и квадратурного 4 фильтров нижних частот соответственно:

Sl=cos(M +p ): (1)

So = sin(„+ф )

2лК

Эти сигналы поступают в первый блок формирования сигнала слежения и опознавания 16. Выходные сигналы первого блока

16 в соответствии с фиг. 2 имеют вид:

Sl1=(Si+ So)(Si — So)- $ i — S а:

So1- 2%$а (2) Подставляя значение Sl и $а из (1) в (2), получим на выходе первого блока 16:

Sl1-cos(„„+2@ ); (3)

$а1= sin(+2 p ).

4#К

Иэ соотношений (3) видно, что каждый блок 16 производит удвоение фазы квадратурных составляющих сигналов при их прохождении с входа блока 16 на выход.

Аналогично, на выходе второго блока 16

$ц-сов(„+4@ );

$аг-sin(„+4p ).

8_#_К (4) Аналогично на вйходах m-ro блока 16

2m+1 ГК

$i = cos(М

+ 2m@ )=

= созМ р;

2 лК

$omsln(. + 2 p )=

=slnM р. (5) Из соотношения (5) видно, что в сигналах на выходе m-ro блока 16 нет компоненты, связанной с манипуляцией.

Сигнал $ап через коммутатора 10, 5 фильтр петли ФАПЧ 7 и сумматор 15 поступает на управляющий вход генератора.5, управляемого напряжением и, таким образом, замыкает петлю фаэовой синхронизации.

10 Для устранения ложных захватов используется сигнал Slm. В случае ложного захвата за боковую полосу сигнала, либо дискретную компоненту в спектре входного колебания сигнал $ представляет собой

15 биения с разностной частотой. Постоянная составляющая биений выделяется третьим фильтром нижних частот 12 и поступает на пороговый блок 13. Порог срабатывания пороговых блоков 13 выбирается в интервале

20 0-1 и может составлять 1/2. Так как посоянная составляющая сигнала на выходе третьего фильтра нижних частот 12 не превышает установленного порога (в случае биений), то

: пороговый блок 13 производит запуск гене25 ратора линейно изменяющегося напряжения 14; который череЗ сумматор 15 перестраивает генератор 5, управляемый напряженйем, в ийтервале неопределенйо-сти по чаСтоте.

30 .. После достижения- петлей ФАПЧ синхронного состояния фазовая ошибка р0, а следовательно, $ П - ..Постоянйая составляющая $ П с выхода третьего фильтра нижних 12 поступает в пороговый блок 13, где

35 превышает установленный порог 1/2 и через генератор линейно-изменяющегося напряжения 14 останавливает перестройку частоты генератора 5. С этого момента петля ФАПЧ переходйт в режим слежения за . 40 фазой ФМ-сигнала.

Данныйдемодулятор позволяетобеспечивать когерентную обработку ФМ-сигналнов с числом фаз.от 2 до М = 2 (кратность от 1 до m), При этом в соответствии с числом

45 фаз ФМ-сигнала коммутатор l0 и мультиплексор 11 должны подавать в петлю ФАПЧ и схему поиска сигйалы с выходов соответствующего блока 16 (т.е. с выходов первого блока 16 при однократной ФМ; с выходов

50 второго блока 16 — при двухкратной Ф М и т.д.), Автоматическое определение кратно сти ФМ и управление работой коммутатора

10 и мультиплексора 11 происходит следую55 щим образом. В начальный момент времени, когда кратность ФМ-сигнала не опререлена, на выходе блока определения кратности манипуляции 17 присутствует нулевой код, который определяет подачу в петлю ФАПЧ и схему поисКа соответственно

1786681 сигналов с второго выхода m-го блока 16 и входом фазовращателя, выход которого порогового блока 15;,Таким образом, при . подключен ко второму входу второго фазовхождении петли ФАПЧ в синхронизм в на- вого детектора, первый вход которого являчальный момент демодулятор работает в со- ется входом демодулятора, о т л и ч а ю щ иответствии с опианным выше алгоритмом s 5 и с я -тем, что, с целью демодуляции сигнарасчете на случай максимально возможной лов в условиях априорно неорпеделенной кратности. ФМ. После перехода петли . кратности и повышения помехоустойчивоФАПЧ в режим слежения за фазой ФМ-сиг- . сти, введены мультиплекстор, коммутатор, нала на выходах пороговых блоков 13 с 1-го блок определения кратности манипуляции, по m 1-й присутствуют нулевые уровни, а 10 блоки формирования сигнала слежения и на выходах пороговых блоков 13 с п -го пр опознавания, генератор линейно иэменяюm-й-единичные уровни (здесь в — количест- щегося напряжения, пороговые блоки, во блоков 16 в демодуляторе, т.е, максй- третьи фильтры нижних частот, первый и мально возможная кратность ФМ, а второй решающие блоки, первые входы коmc-кратность принимаемого ФМ-сигйала). 15 торых подключены к выходам соответствен9 соответствии суровйями сигналов на но первого и второго фильтров нижних выходах блоков 13 в блоке определения частотисоответственнок первомуи вторократности манипуляцйи 17(см.фиг.3) проис-. му входам первого блока форййрования сигходитопределение кратности т йринимае- нала слежения и опознавания, первый и мого ФМ-сигнала.. .-:;.. "-: 20 второй выходы которого через последоваСигналс m-го порогового блока 13(оэ- тельно соединенные последующие блоки начающий синхронизм петли ФАПЧ) посту-. формирования сигнала слежения и опознапает на разрешающий вход блока .17, на . вания подключены соответственно к первоостальныевходыкоторогопоступаютсигна- му и второму. входам последнего блока лы с 1-го no m-1-й лок 13. В соответствии 25 формирований сигйала слежения и опознасо схемой организации элементов И 24 на вания, первый выход каждого блока формивход шифратора 23 поступает сигнал уни-.. рования сигнала слежения и опознавания тарного двоичного кода п кратности мани-: через послеДовательно соединенные трепуляции при m<4 m. Если же кратность .: . тийфильтрнижнихчастоти пороговый блок манипуляции m< - m; на входы шифратора 30 соединен с соответствующим входом блока

23. поступают нули (поскольку в этом случае: определения кратности манипуляции и сона выходах всех пороговых блоков 13, кроме ответствующим входом мультиплексора, последнего, т,е.,е-го- нулевые уровйи). Сиг- выход которого через генератор линейно иэнал. кода с выхода шифратора 23 по шине . меняющегося напряжения соединен с перадреса управляет работой коммутатора.10 и. 35 вым входом сумматора, выход которого мультиплексора 11, а также определяет ве- . соединен с входом генератора, управляемо . личины порогов принятия решения в рева- ro напряжением, второй выход каждого блоющих блоках 8 и 90.. ка формирования сигнала слежения и

Демодулированные квадратурнйе со- опознавания соединен с Соответствующим ставляющие сигнала Si u Sa поступают в 40 входом коммутатора, выход которого через решающие блоки 8 и 9, предтавляющие со- фильтр соединен с вторым входом сумматобой в общем случае многоуровневые кван- ра, выхоД блока определения кратности матователи, на вйходе которых формируются нипуляции соединен с управляющим отсчеты, соответствующие передаваемой . входом .мультиплексора, с управляющим йнформацйойной последовательности. 45 входом коммутатора и со вторыми входами

Таким образом, предлагаемый демоду- первого и второго решающих блоков, выхолятор, по сранению с прототипом, автома- ды которых являются выходамидемодулято- . тически обеспечивает демодуляцию ра. сигналов произвольной кратности, а также 2. Демодулятор по и. 1, о т л и ч а ю щ иопределяет и устраняет ложный захват. 50 и с я т ем, что каждый блок формирования

Ф о р м у л а и з о б р е т е н и я сигнала слеженйя и опоэнаванйя содержит

1. Демодулятор фаэоманипулирован- два перемножителя, вычитатель. усилитель ных сигналов, содержащий фильтр, сумма- . и сумматор, первый вход которого соедйнен тор, первый и второй фильтры нижних с первым входом вычитателя и с первым частот, входы которых подключены к выхо- 55 входом первого перемножителя, второй дам соответственно. первого и второго фа- " вход которого соединен со вторым входом эовых детекторов. первые входы которых -" вычитателя и со вторым входом сумматора, обьединены, генератор, управляемый на- . выход которого соединен с первым входом пряжением, выход которого соединен с вто- второго перемножителя, второй вход которым входом первого фазового детектора и с рого подключен к выходу вычитателя, вход

1786681

10 усилителя подключен к выходу первого перемножителя, первый и второй входы которого являются соответственно первым и вторым входами блока формирования сигнала слежения и опознавания, первым и 5 вторым выходами которого являются соответственно выход второго перемножителя и выход усилителя.

3, Демодулятор по и, 1, о т л и ч а ю щ ий с я тем, что, блок определения кратности 10 манипуляции содержит шифратор и элементы И, выходы которых соединены со входами шифратора, причем разрешающие входы всех элементов И объединены, а выходы всех элементов И, кроме первого, соединены с соответствующими входами последующих элементов И, разрешающие, и сигнальные входы которых являются входами блока определения кратности манипуляции, выходом которого является выход шифратора.

1786681 ар еа ающ. вхоЗ, /ам ер

Составитель Н, Пархоменко

Техред M.Ìîðãåíòàë Корректор С. Юско

Редактор

Производственно-издательский комбинат "Патент", г. Ужгород,.ул.Гагарина, 101

Заказ 258 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035. Москва, Ж-35, Раушская наб., 4/5